MSP430寄存器详细分类.docx

《MSP430寄存器详细分类.docx》由会员分享,可在线阅读,更多相关《MSP430寄存器详细分类.docx(41页珍藏版)》请在冰豆网上搜索。

MSP430寄存器详细分类

时钟模块

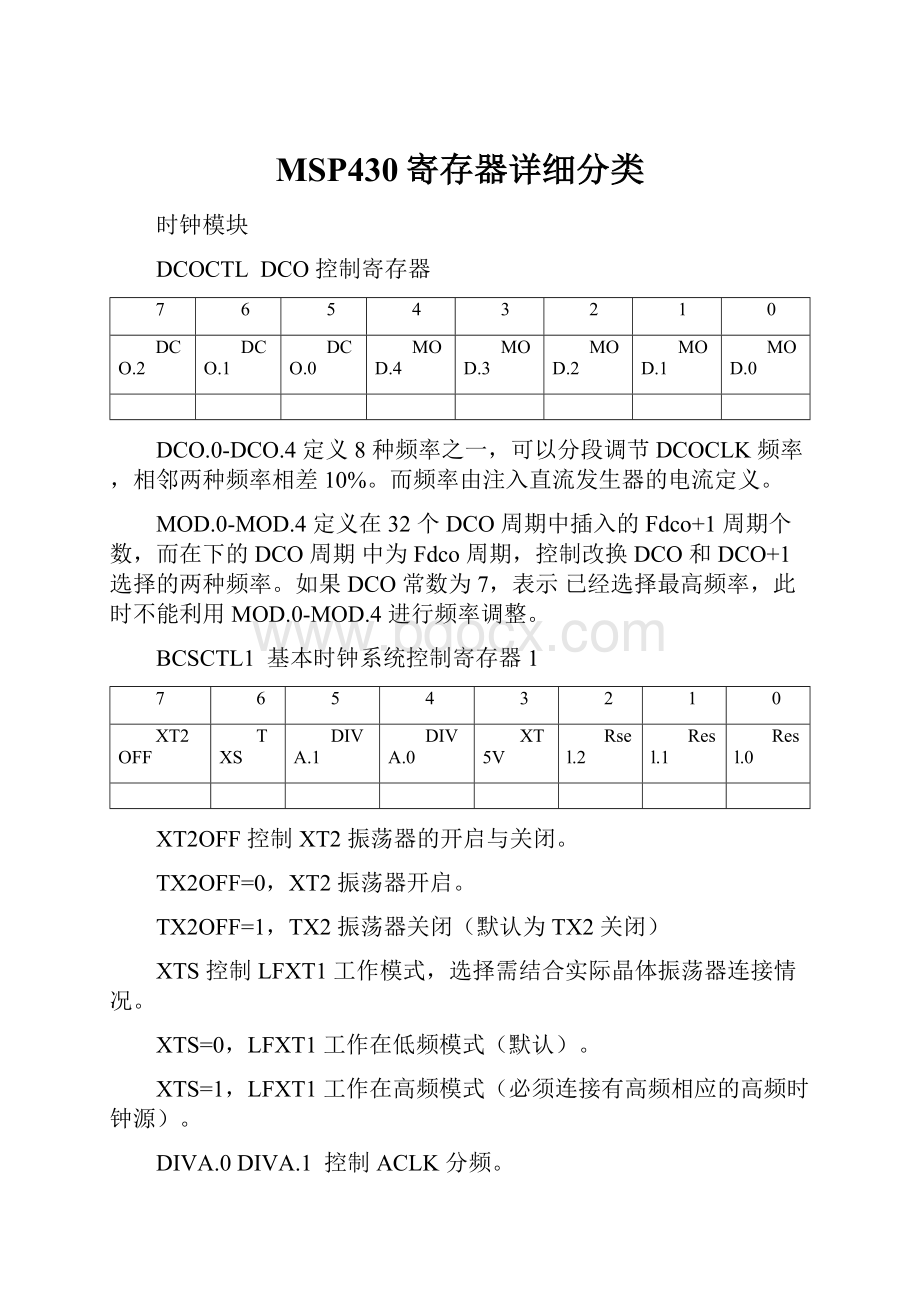

DCOCTLDCO控制寄存器

7

6

5

4

3

2

1

0

DCO.2

DCO.1

DCO.0

MOD.4

MOD.3

MOD.2

MOD.1

MOD.0

DCO.0-DCO.4定义8种频率之一,可以分段调节DCOCLK频率,相邻两种频率相差10%。

而频率由注入直流发生器的电流定义。

MOD.0-MOD.4定义在32个DCO周期中插入的Fdco+1周期个数,而在下的DCO周期中为Fdco周期,控制改换DCO和DCO+1选择的两种频率。

如果DCO常数为7,表示已经选择最高频率,此时不能利用MOD.0-MOD.4进行频率调整。

BCSCTL1基本时钟系统控制寄存器1

7

6

5

4

3

2

1

0

XT2OFF

TXS

DIVA.1

DIVA.0

XT5V

Rsel.2

Resl.1

Resl.0

XT2OFF控制XT2振荡器的开启与关闭。

TX2OFF=0,XT2振荡器开启。

TX2OFF=1,TX2振荡器关闭(默认为TX2关闭)

XTS控制LFXT1工作模式,选择需结合实际晶体振荡器连接情况。

XTS=0,LFXT1工作在低频模式(默认)。

XTS=1,LFXT1工作在高频模式(必须连接有高频相应的高频时钟源)。

DIVA.0DIVA.1控制ACLK分频。

0不分频(默认)

12分频

24分频

38分频

XT5V此位设置为0。

Resl1.0,Resl1.1,Resl1.2三位控制某个内部电阻以决定标称频率。

Resl=0,选择最低的标称频率。

……..Resl=7,选择最高的标称频率。

BCSCTL2基本时钟系统控制寄存器2

7

6

5

4

3

2

1

0

SELM.1

SELM.0

DIVM.1

DIVM.0

SELS

DIVS.1

DIVS.0

DCOR

SELM.1SELM.0选择MCLK时钟源

0时钟源为DCOCLK(默认)

1时钟源为DCOCLK

2时钟源为LFXT1CLK(对于MSP430F11/12X),时钟源为XT2CLK(对

于MSP430F13/14/15/16X);

3时钟源为LFTXTICLK。

DIVM.1DIVM.0选择MCLK分频

01分频(默认)

12分频

24分频

38分频

SELS选择SMCLK时钟源

0时钟源为DCOCLK(默认)

1时钟源为LFXT1CLK(对于MSP430F11/12X),时钟源为XT2CLK(对

于MSP430F13/14/15/16X)。

DIVS.1DIVS.0选择SMCLK分频。

01分频

12分频

24分频

48分频

DCOR选择DCO电阻

0内部电阻

1外部电阻

PUC信号之后,DCOCLK被自动选择MCLK时钟信号,根据需要,MCLK的时钟源

可以另外设置为LFXT1或者XT2。

设置顺序如下:

[1]复位OscOff

[2]清除OFIFG

[3]延时等待至少50us

[4]再次检查OFIFG,如果仍然置位,则重复[3]、[4]步骤,直到OFIFG=0

为止。

IO端口

MSP430的端口

器件

P1

P2

P3

P4

P5

P6

S

COM

MSP430F11X

√

√

MSP430F12X

√

√

√

MSP430F13/14/15/16

√

√

√

√

√

√

MSP430F4XX

√

√

√

√

√

√

√

√

MSP430F20X

√

√

MSP430F21X

√

√

MSP430F22X

√

√

√

√

MSP430端口功能

端口

功能

P1、P2

I/O、中断功能、其他片内外设功能

P3、P4、P5、P6

I/O、其他片内外设功能

S、COM

I/O、驱动液晶

PxDIR方向寄存器

7

6

5

4

3

2

1

0

P7DIR

P6DIR

P5DIR

P4DIRP3DIR

P2DIR

P1DIRP0DIR

0为输入模式

1为输出模式

在PUC后全都为复位,作为输入时,只能读;作为输出时,可读可定。

PxIN输入寄存器

7

6

5

4

3

2

1

0

PxIN

PxIN

PxIN

PxINPxIN

PxIN

PxINPxIN

输入寄存器是只读的,用户不能对它写入,只能读取其IO内容。

此时引

脚方向必须为输入。

PxOUT输出寄存器

7

6

5

4

3

2

1

0

P7OUT

P6OUT

P5OUT

P4OUTP3OUT

P2OUT

P1OUTP1OUT

这是IO端口的输出缓冲器,在读取时输出缓存的内容与脚引方向定义无关。

改变方向寄存器的内容,输出缓存的内容不受影响。

PxIFG中断标专寄存器

7

6

5

4

3

2

1

0

P7IFG

P6IFG

P5IFG

P4IFGP3IFG

P2IFG

P1IFGP0IFG

标志相应引脚是否有待处理中断信息。

0没有中断请求

1有中断请求

PxIES中断触发沿选择寄存器

7

6

5

4

3

2

1

0

P7IES

P6IES

P5IES

P4IESP3IES

P2IES

P1IESP0IES

0上升沿使相应标志置位

1下降沿使相应标志置位

PxIE中断使能寄存器

7

6

5

4

3

2

1

0

P7IE

P6IE

P5IE

P4IEP3IE

P2IE

P1IEP0IE

0禁止中断

1允许中断

PxSEL功能选择寄存器

7

6

5

4

3

2

1

0

P7SEL

P6SEL

P5SEL

P4SELP3SEL

P2SEL

P1SELP0SEL

0选择引脚为I/O功能。

1选择引脚为外围模块功能

关于端口P3、P4、P5、P6

端口P3、P4、P5、P6是没有中断功能的,其它功能与P1、P2相同。

所以

在此不再作详尽说明。

关于端口COM、S

这些端口实现与LCD片的驱动接口,COM端是LCD片的公共端,S端为LCD

片的段码端。

LCD片输出端也可以用软件配置为数字输出端口,详情使用请查

看其手册。

WDT看门狗

WDTCNT计数单元

这是16位增计数器,由MSP430所选定的时钟电路产生的固定周期时钟信号对计数器进行加法计数。

如果计数器事先被预置的初始状态不同,那么从开始计数到计数溢出为止所用的时间就不同。

WDTCNT不能直接通过软件存取,必须通过看门狗定时器的控制寄存器WDTCTL来控制。

WDTCTL控制寄存器

15--8

7

6

5

4

3

2

1

0

口令

HOLD

NMIES

NMI

TMSEL

CNTCL

SSEL

IS1

IS0

WDTCTL由高8位口令和低8位控制命令组成。

要写入操作WDT的控制命令,出于安全原因必须先正确写入高字节看门狗口令。

口令为5AH,如果口令写错将导致系统复位。

读WDTCTL时不需要口令。

这个控制寄存器还可以用于设置NMI引脚功能。

ISO,IS1选择看门狗定时器的定时输出。

其中T是WDTCNT的输入时钟源周期。

0Tx2(15)

1Tx2(13)

2Tx2(9)

3Tx2(6)

SSEL选择WDTCNT的时钟源

0SMCLK

1ACLK

由IS0,IS1,SSEL3可确定WDT定时时间。

WDT最多只能定时8种和时钟源相关的

时间。

下表列出了WDT可选的定时时间(晶体为32768HZ,SMCLK=1MHZ)。

WDT的定时时间表

SSEL

IS1

IS0

定时时间/ms

0

1

1

0.056

Tsmclkx2(6)

0

1

0

0.5

Tsmclkx2(9)

1

1

1

1.9

Taclkx2(6)

0

0

1

8

Tsmclkx2(13)

1

1

0

16

Taclkx2(9)

0

0

0

32

Tsmclkx2(15)(PUC复位后的值)

1

0

1

250

Taclkx2(13)

1

0

0

1000

Taclkx2(15)

CNTCL当该位为1时,清除WDTCNT。

TMSEL工作模式选择

0看门狗模式

1定时器模式

NMI选择RST/NMI引脚功能,在PUC后被复位。

0RST/NMI引脚为复位端

1RST/NMI引脚为边沿触发的非屏蔽中断输入。

NMIES选择中断的边沿触发方式

0上升沿触发NMI中断

1下降沿触发NMI中断

HOLD停止看门狗定时器工作,降低功耗。

0WDT功能激活

1时钟禁止输入,计数停止

定时器

各种定时器功能

定时器

功能

看门狗定时器

基本定时,当程序发生错误时执行一个受控的系统重启动。

基本定时器

基本定时,支持软件和各种外围模块工作在低频率、低功耗条件下。

定时器A

基本定时,支持同时进行的多种时序控制、多个捕获、比较功能和多种输出

波形(PWM),可以以硬件方式支持串行通信。

定时器B

基本定时,功能基本同定时器A,但比较定时器A灵

活,功能更强大。

TACTL控制寄存器

15--10

9

8

7

6

5

4

3

2

1

0

未用

SSEL1

SSEL0

ID1

ID0

MC1

MC0

未用

CLR

TAIE

TAIFG

SSEL1、SSEL0选择定时器输入分频器的时钟源

Timer_A时钟源

SSEL1

SSEL0

输入时钟源

说明

0

0

TACLK

用特定的外部引脚信号

0

1

ACLK

辅助时钟

1

0

SMCLK

子系统时钟

1

1

INCLK

见器件说明

ID1,ID0输入分频选择

00不分频

012分频

104分频

118分频

MC1,MC0计数模式控制位

00停止模式

01增计数模式

10连续计数模式

11增/减计数模式

CLR定时器清除位

POR或CLR置位时定时器和输入分频器复位。

CLR由硬件自动复位,其读出始终为0。

定时器在下一个有效输入沿开始工作。

如果不是被清除模式控制暂停,则定时器以增计数模式开始工作。

TAIE定时器中断允许位

0禁止定时器溢出中断

1允许定时器溢出中断

TAIFG定时器溢出标志位

增计数模式:

当定时器由CCR0计数到到0时,TAIFG置位。

连续计数模式:

当定时器由0FFFFH计数到0时,TAIFG置位。

增/减计数模式:

当定时器由CCR0减计数到0时,TAIFG置位。

TAR16位计数器

这是计数器的主体,内部可读写。

[1]修改TIMWER_A:

当计数时钟不是MCLK时,写入应该在计数器停止计数时写,

因为它与CPU时钟不同步,可能引起时间竞争。

[2]TIMER_A控制位的改变:

如果用TACLK控制寄存器中的控制位来改变定时器

工作,修改时定器应停止,特别是修改输入选择位、输入分频器和定时器清除位时。

输入时钟和软件所用的系统时钟异步可能引起时间竞争,使定时器响应出错。

CCTLx捕获/比较控制寄存器

1514

1312

11

10

9

8

765

4

3

2

1

0

CAPTMOD1-0

CCIS1-0

SCS

SCCIx

CAP

OUTMODx

CCIEx

CCIx

OUT

COV

CCIFx

TIMER_A有多个捕获比较模块,每个模块都有自己的控制寄存器CCTLx

CAPTMOD1-0选择捕获模式

00禁止捕获模式

01上升沿捕获

10下降沿捕获

11上升沿与下降沿都捕获

CCISI1-0在捕获模式中用来定提供捕获事件的输入端

00选择CCIxA

01选择CCIxB

10选择GND

11选择VCC

SCS选择捕获信号与定时器时钟同步、异步关系

0异步捕获

1同步捕获

异步捕获模式允许在请求时立即将CCIFG置位和捕获定时器值,适用于捕获信

号的周期远大于定时器时钟周期的情况。

但是,如果定时器时钟和捕获信号发生时

间竞争,则捕获寄存器的值可能出错。

在实际中经常使用同步捕获模式,而且捕获总是有效的。

SSCIx比较相等信号EQUx将选择中的捕获、比较输入信号

CCIx(CCIxA,CCIxB,Vcc和GND)进行锁存,然后可由SCCIx读出。

CAP选择捕获模式还是比较模式。

0比较模式

1捕获模式

注意:

同时捕获和捕获模式选择

如果通过捕获比较寄存器CCTLx中的CAP使工作模式从比较模式变为捕获模式,

那么不应同时进行捕获;否则,在捕获比较寄存器中的值是不可预料的,推荐的指

令顺序为:

[1]修改控制寄存器,由比较模式换到捕获模式。

[2]捕获

OUTMODx选择输出模式

000输出

001置位

010PWM翻转/复位

011PWM置位/复位

100翻转/置位

101复位

110PWM翻转/置位

111PWM复位/置位

定时器时钟上升沿时OUTx在各模式下的状态

输出模式

EQU0

EQUx

OUTx状态(或触发器输入端D)

0

X

X

X(OUTx位)

1

X

0

OUTx(不变)

X

1

1(置位)

2

0

0

OUTx(不变)

0

1

/OUTx(与以前相反)

1

0

0

1

1

1(置位)

3

0

0

OUTx(不变)

0

1

1(置位)

1

0

0

1

1

1(置位)

4

X

0

OUTx(不变)

X

1

/OUTx(与以前相反)

5

X

0

OUTx(不变)

X

1

0

6

0

0

OUTx(不变)

0

1

/OUTx(与以前相反)

1

0

1

1

1

0

CCIx捕获比较模的输入信号

捕获模式:

由CCIS0和CCIS1选择的输入信号通过该位读出。

比较模式:

CCIx复位。

OUT输出信号

0输出低电平

1输出高电平

如果OUTMODx选择输出模式0(输出),则该位对应于输入状态。

COV捕获溢出标志

0输出低电平

1输出高电平

[1]当CAP=0时,选择比较模式。

捕获信号发生复位,没有使COV置位的捕获事件。

[2]当CAP=1时,选择捕获模式,如果捕获寄存器的值被读出再次发生捕获事件,

则COV置位。

程序可检测COV来断定原值读出前是否又发生捕获事件。

读捕获寄存器时不会使溢出标志复位,须用软件复位。

CCIFGx捕获比较中断标志

捕获模式:

寄存器CCRx捕获了定时器TAR值时置位。

比较模式:

定时器TAR值等于寄存器CCRx值时置位。

CCRx捕获/比较寄存器

15--0

在捕获比较模块中,可读可写。

其中CCR0经常用作周期寄存器,其他CCRx相同。

TAIV定器器A中断向量寄存器

15--5

4--1

0

0--0

中断向量

0

Timer_A有两个中断向量,一个单独分配给捕获比较寄存器CCR0,另一个作为

共用的中断向量用于定时器和其他的捕获比较寄存器。

CCR0中断向量具有最高的优先级,因为CCR0能用于定义是增计数和增减计数模

式的周期。

因此,他需要最快速度的服务。

CCIFG0在被中断服务时能自动复位。

CCR1-CCRx和定时器共用另一个中断向量,属于多源中断,对应的中断标志

CCIFG1-CCIFGx和TAIFG1在读中断向量字TAIV后,自动复位。

如果不访问TAIV寄存器,则不能自动复位,须用软件清除;如果相应的中断允许位复位(不允许中断),

则将不会产生中断请求,但中断标志仍存在,这时须用软件清除。

关于中断挂起和返回不包括处理约需要11~16个时钟周期。

TIMER_A中断优先级

中断优先级

中断源

缩写

TAIV的内容

最高

捕获/比较器1

CCIFG1

2

捕获/比较器1

CCIFG1

4

捕获/比较器x

CCIFGx

最低

定时器溢出

TAIFG1

10

没有中断将挂起

0

比较器A

CACTL1比较器A控制寄存器1

7

6

5

4

3

2

1

0

CAEX

CARESL

CAREF1

CAREF0CAON

CAIES

CAIE

CAIFG

CAEX比较器的输入端,控制比较器A的输入信号和输出方向。

CARSEL选择内部参考源加到比较器A的正端或负端。

CAEX和CARSEL的含义

CARSECAEX含义

0

0

内部参考源加到比较器的正端

1

内部参考源加到比较器的负端

1

0

内部参考源加到比较器的负端

1

内部参考源加到比较器的正端

CAREF1、CAREF0选择参考源

0使用外部参考源;

1选择0.25Vcc为参考电压

2选择0.5Vcc为参考电压

3选择二极客电压为参考电压,必须见具体的芯片资料。

CAON控制比较器A的打开和关闭

0关闭比较器

1打开比较顺

CAIES中断触发沿选择

0上升沿使中断标志CAIFG置位

1下降沿使中断标志CAIFG置位

CAIE中断允许

0禁止中断

1允许中断

CAIFG比较器中断标志

0没有中断请求

1有中断请求

CACTL2比较器A控制寄存器2

7

6

5

4

3

2

1

0

CACTL2.7

CACTL2.6

CACTL2.5

CACTL2.4P2CA1

P2CA0

CAF

CAOUT

CACTL2.7—2.4含义请参见具体的芯片资料,例如,在MSP430X1XX系列中,这

位可以被执行,但不控制任何硬件,可被用作标志位。

P2CA1控制输入端CA1

0外部引脚信号不连接比较器A

1外部引脚信号连接比较器A

P2CA0控制输入端CA0

0外部引脚信号不连接比较器A

1外部引脚信号连接比较器A

CAF选择比较器输出端是否经过RC低通滤波器

0不经过

1经过

CAOUT比较器A的输出

0CA0小于CA1

1CA0大于CA1

CAPD端口禁止寄存器

比较器A模块的输入输出与IO口共用引脚,CAPD可以控制IO端口输入缓冲器的通断开关。

当输入电压不接近Vss或Vcc时,CMOS型的输入缓冲器可以起到分流作用。

这样可以减少了由不是Vss或Vcc的输入电压所引起的流入输入缓冲器的电流。

控制位CAPD0—CAPD7初始化为0,则端口输入缓冲器有效。

当相应控制位置1时,端口输入缓冲器无效。

ADC12模数转换模块

ADC12模块的所有寄存器

寄存器

寄存器缩写

寄存器含义

转换控制寄存器

ADC12CTL0

转换控制寄存器0

ADC12CTL1

转换控制寄存器1

中断控制寄存器

ADC12IFG

中断标志寄存器

ADC12IE

中断使能寄存器

ADC12IV

中断向量寄存器

存储及其控制寄存器

ADC12MCTL0-ADC12MCTL15

存储控制寄存器0-15

ADC12MEM0-ADC12MCTL15

存储寄存器0-15

ADC12CTL0转换控制寄存器0

15--12

11--8

7

6

5

4

3

2

1

0

SHT1

SHT0

MSC

2.5V

REFON

ADC12ON

ADC12TOVIE

ADC12TVIE

ENC

ADC12SC

ADC12SC采集/转换控制位

在不同条件ADC12SC的含义.

ENC=1

SHP=1

ADC12SC由0变为1启动AD转换

AD转换完成后ADC12SC自动复位

ISSH=0

SHP=0

ADC12SC保持高电平时采集

ADC12SC复位时启动一次转换

ENC=1表示转换允许(必须使用);ISSH=0表示采要输入信号为同相输入(推荐使用);SHP=1表示采样信号SAMPCON来源于采样定时器;SHP=0表示采样直接由ADC12SC控制。

使用ADC12SC时,需注意以上表格信号的匹配。

用软件启动一次AD转换,需要使用一条指令来完成ADC12SC与ENC的设置。

ENC转换允许位

0ADC12为初始状态,不能启动AD转换

1首次转换由SAMPCON上升沿启动

只有在该位为高电平时,才能用软件或外部信号启动转换。

在不同转换模式,

ENC由高电平变为低电平的影响不同:

□当CONSEQ=0(单通道单次转换模式)且ADC12BUSY=1(ADC12处于采样或者转

换)时,中途撤走ENC信号(高电平变为低电平),则当前操作结束,并可能得到错误

结果。

所以在单通道单次转换模式整个过程中,都必须保证ENC信号有效。

□当CONSEQ=0(非单通道单次转换)时,EN