画出图P42由或非门组成的基本RS触发器输出端Q.docx

《画出图P42由或非门组成的基本RS触发器输出端Q.docx》由会员分享,可在线阅读,更多相关《画出图P42由或非门组成的基本RS触发器输出端Q.docx(26页珍藏版)》请在冰豆网上搜索。

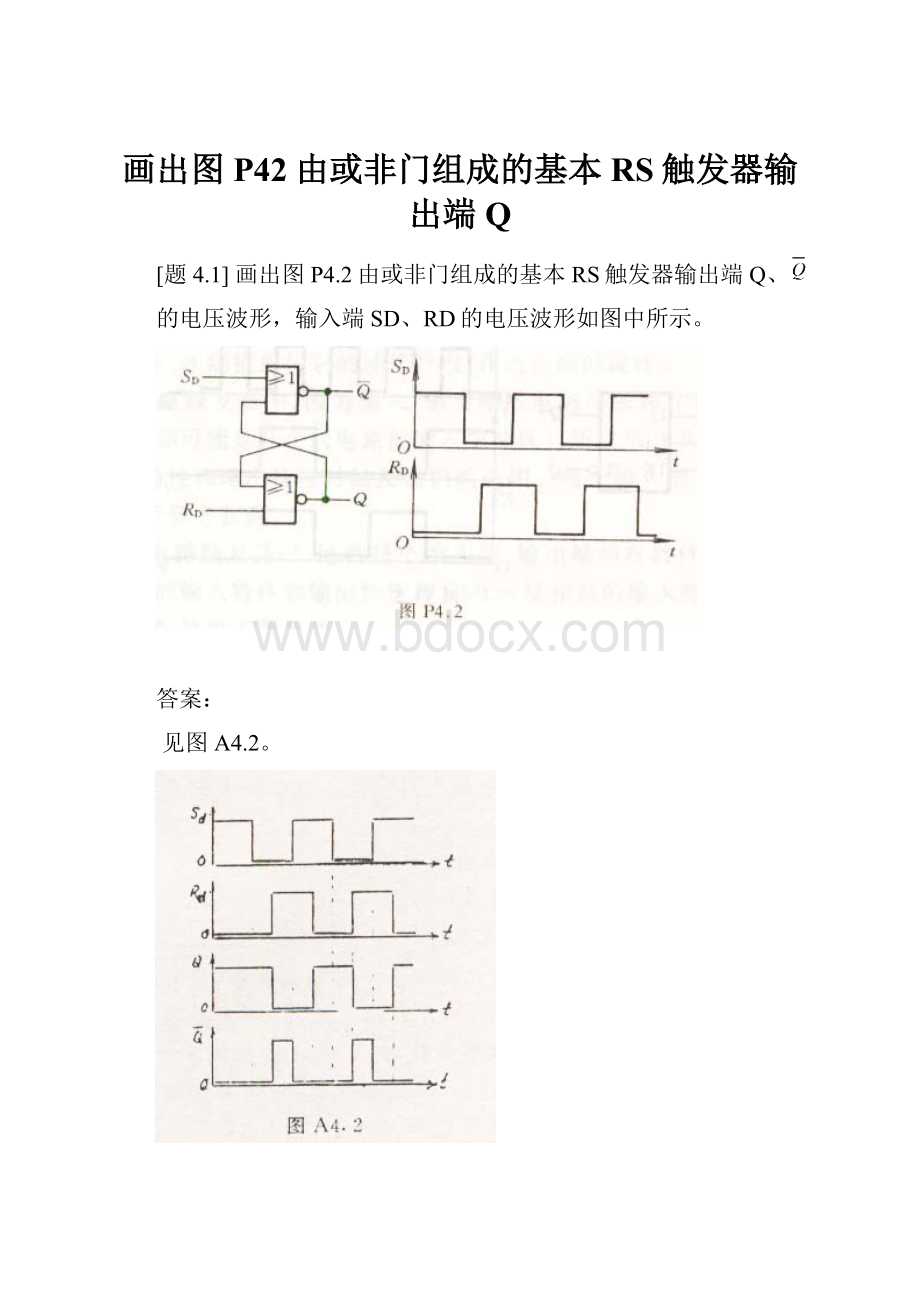

画出图P42由或非门组成的基本RS触发器输出端Q

[题4.1]画出图P4.2由或非门组成的基本RS触发器输出端Q、

的电压波形,输入端SD、RD的电压波形如图中所示。

答案:

见图A4.2。

[题4.2]在图P4.5电路中,若CP、S、R电压波形如图中所示,试画出Q、

端与之对应的电压波形。

假定触发器的初始状态为Q=0。

答案见图A4。

5

[题4.3]若主从结构RS触发器的CP、S、R、

各输入端的电压波形如图P4.8所示,

,试画出Q、

端对应的电压波形。

答案:

见图A4.8。

[题4.4]已知主从结构JK触发器J、K和CP的电压波形如图P4.9所示,试画出Q、

端对应的电压波形。

设触发器的初始状态为Q=0。

答案:

见图A4.9。

[题4.5]已知维持阻塞结构D触发器各输入端的电压波形如图P4.11所示,试画出Q、

端对应的电压波形。

答案:

见图A4.11。

[题4.6]设图P4.13中各触发器的初始状态皆为Q=0,试画出在CP信号连续作用下各触发器输出端的电压波形。

答案:

见图A4.13。

[题4.7]试画出图P4.20电路输出端Y、Z的电压波形。

输入信号A和CP的电压波形如图中所示。

设触发器的初始状态均为Q=0。

答案:

见图A4.20。

[题4.8]试画出图P4.22电路在一系列CP信号作用下Q1、Q2、Q3的输出电压波形。

触发器均为边沿触发结构,初始状态均为Q=0。

答案:

见图A4.22。

【试题4-9】JK触发器,时钟波形CP及输入控制J,K波形如图4-9所示。

试分别画出主从型JK触发器和负边沿JK触发器输出端Q的电压波形,设触发器的初始状态为零。

图4-9

【解题方法指导】

触发器时序图绘制要领

绘制触发器的时序图时要特别注意:

触发器中有边沿触发器和非边沿触发器之分。

对于边沿触发器,如TTL维持-阻塞D触发器和CMOS主从JK触发器等,其次态仅仅取决于CP脉冲到达时刻的输入状态。

对于非边沿触发器,如TTL主从JK触发器,其次态与整个CP=1期间的输入状态有关,存在着“一次变化”现象。

此时,绘制时序图的要领可归纳如下:

在触发器的动作沿,如果仅根据当时输入状态值,次态应保持0状态时,则在CP=1期间有J信号中的正向脉冲干扰(置1)会引起错误,而K信号中出现的干扰则无妨;如果次态应保持1状态,则CP=1期间K中的正向脉冲干扰(置0)会引起错误,而J信号中的正向脉冲干扰则无妨。

本题主要考点:

JK触发器的功能表和TTL主从JK触发器的“一次变化”现象,其中“一次变化”现象是重点和难点。

解答

主从JK触发器的输出波形Q如图4-10所示。

图4-10

说明如下:

(1)主从JK触发器的输出波形Q主从。

1.t=t1时,J=K=0,触发器应保持原初始状态0不变,但在t=t0前J=1,所以触发器翻转为1状态(一次变化效应)。

2.t=t3时,J=K=1,触发器状态翻转,Q主从变为0状态。

3.t=t5时,J=0,K=1,触发器应当清0(即保持原状态0不变),但在t=t4前J=1,所以触发器在t=t5时翻转为1状态(一次变化效应)。

4.t=t7时,J=1,K=0,触发器翻转为1状态。

5.t=t9时,J=0,K=0,触发器应保持原状态1不变,但在时t=t8时K变为1状态,所以触发器在t=t9时翻转为0状态(一次变化效应)。

6.t=t12时,J=0,K=0,触发器应保持原状态0不变,但在CP=1期间J曾为1状态,所以触发器在t=t12时翻转为1状态(一次变化效应)。

所以主从JK触发器的输出波形Q主从如图4-20所示。

(2)边沿JK触发器的输出波形Q负边沿。

1.t=t1时,J=K=0,触发器状态保持,Q负边沿继续为0状态。

2.t=t3时,J=K=1,触发器状态翻转(即计数状态),故Q负边沿变为1状态。

3.t=t5时,J=0,K=1,触发器清0,故Q负边沿变为0状态。

4.t=t7时,J=1,K=0,触发器置1,故Q负边沿变为1状态。

5.t=t9时,J=K=0,触发器状态保持,故Q负边沿继续保持为1状态。

6.t=t12时,J=K=0,触发器状态保持,Q负边沿继续为1状态。

所以边沿JK触发器的输出波形Q负边沿Q如图4-20所示。

【试题4-11】电路如图4-12所示,试求:

(1)各触发器的特征方程;

(2)对应图示的输入信号,分别画出各个触发器输出端Q端的波形。

图4-12

【解题指导】

图中触发器均为主从型触发器,主从触发器是为了满足实际应用的要求,即触发器在每个CP脉冲作用期间,状态只能变换一次而采用的一种有效结构。

这种结构的触发器,当有置位、复位信号作用时,触发器输出状态即被直接置0或置1。

在没有置位、复位信号作用时,输出状态转换则由CP信号和激励信号控制。

当CP信号上升沿到来时(以及CP=1期间),主触发器对激励信号采样使其输出状态根据激励而变化,从触发器关闭保持原状态不变。

而当CP下降沿到来时,主触发器关闭,从触发器打开,根据主触发器的采样输出进行输出状态转换。

所以,主从RS触发器的激励信号应该超前于CP下降沿才能有效。

对于其中的主从JK触发器,在CP=1期间,若信号多次变化,还要考虑“一次变化”问题。

由于三个电路都没有输出到输入的反馈线,只要掌握各触发器的基本逻辑功能,就能写出其状态方程。

画触发器输出波形图可以按如下口诀进行:

直接置位最优先(这里有直接置0端

为0的一段信号,将触发器初态复位为“0”);CP决定何时变(本例的触发器是主从型的,在CP=1期间接受信号,CP的下降沿触发);根据激励定输出(CP下降沿到来时,触发器到底翻转为何种状态决定于激励信号,由触发器的真值表决定)。

依据这个原则,就可正确地画出触发器输出端的波形。

本例涉及两种主从结构的触发器的动作特点。

因为RS触发器对R、S的取值附有约束条件,即R、S不能同时为1,否则可能出现触发器状态不定的情况。

而JK触发器其J、K取值不受任何约束,因此更具工程实用价值。

【解答】

图4-13

(1)状态方程:

图(a)Qn+1=S+

Qn,RS=0(约束条件,即RS不能同时为1);

图(b)

图(c)Qn+1=D(JK触发器转换为D触发器)

(2)本例(a)、(b)、(c)三个电路的输出波形分别画出为Q1、Q2、Q3如图4-13所示。

同时应注意主从JK触发器在CP=1期间若信号多次变化,输出要用“一次变化”的规律判断。

若为CMOS主从JK触发器则不存在“一次变化”问题,只要看CP由1↘0跳变前瞬时的激励信号,即有效跳变沿前一瞬间的激励信号作为确定输出的依据。

【试题4-12】触发器组成图4-14所示电路。

图中FF1为维持-阻塞D触发器,FF2分别为边沿JK触发器和主从JK触发器(图中未画出),试画出在时钟CP作用下,Q1、Q2的波形。

图4-14

【解题指导】

这是一个两个或多个触发器波形的画法问题,FF1为维持-阻塞D触发器,其状态在CP信号上升沿转换,

连到D1端,即构成计数型触发器。

要注意的是前级触发器的输出是后级的某个控制输入,因此后级触发器的输出波形须根据前级的输出波形来画。

同时题中已指明FF2分别为边沿JK触发器和主从JK触发器,负边沿JK触发器状态在CP信号下降沿转换。

它的次态仅取决于CP信号边沿到达时刻激励信号的取值。

而在此时刻之前或之后激励信号的变化,对触发器的状态没有影响。

因此,抗干扰能力强,工作可靠。

主从JK触发器,状态转换须分两步进行,当CP上升沿到来时,在CP=1期间对激励信号J、K进行采样;而当CP下降沿到来时状态进行转换。

为了可靠工作,要求在CP=1的期间J、K信号不能发生变化。

否则将使触发器受干扰而产生误动作。

这就提醒我们当FF2是主从JK触发器的话,画Q2波形时须考虑存在一次变化问题,认真判断这些干扰的影响,而FF2为边沿JK触发器则只要考虑CP下跳沿时的激励信号即可。

【解答】

由电路图可知,FF1的D=

,故FF1为T’触发器。

而FF2的J=K,故FF2相当于T触发器。

由T’触发器的特性可知,Q1将随CP的↑沿而翻转;由T触发器的特性可知,Q2状态是否改变与Q1状态有关。

若Q1=1,Q2在CP↓处翻转,而当Q1=0时,Q2状态维持不变。

当FF2为边沿J-K触发器时,Q1、Q2(设Q1、Q2初态均为0)和CP的波形见图4-15(a)。

图中Q1状态在CP↑跳处翻转,Q2状态仅在Q1=1情况下且有CP↓跳处翻转。

当FF2为主从J-K触发器时,Q1、Q2和CP的波形见图4-15(b)。

Q1状态和图(a)相同。

Q2状态由1变0出现在CP2,CP4,CP6,CP8的↓跳处,而不象图(a)中出现在CP3,CP7的↓跳处。

其理由是主从J-K触发器存在一次变化问题。

当CP2↑跳到达时,Q1=1不会马上回0,而是要经过一个D触发器的延迟时间(约为2—3个门的tpd),在这段时间内JK触发器的K端为1,因此主触发器接收K=1的信号而使主触发器的Q’=0,

’=1,尽管K端为1的信号只保留短暂的瞬间便很快回到0,但主触发器的状态不再发生变化,因而在CP2↓跳到达时,电路状态Qn+1也由1变0。

CP4,CP6,CP8的情况和CP2相同。

(a)(b)

图4-15

【试题4-13】已知维持-阻塞D触发器组成的电路及CP、A的波形如图4-16(a)、(b)所示,设触发器初态均为0。

试画出输出端Q1、Q2的波形。

(a)(b)

图4-16

【解题指导】

本例给定的电路,由两个维持-阻塞型D触发器构成。

第一个触发器D1=

,接成计数工作方式。

时钟信号即是输入信号A,当A信号上升沿到来时,触发器状态转换。

并由第二个触发器的

生成复位信号,一旦第二个触发器由0态转换为1态,则其

端有1变到0,随之即对第一个触发器复位。

第二个触发器在给定的CP信号上升沿到来时进行状态转换,激励信号D2=Q1。

本例电路中两个触发器相互关联,第一个触发器输出提供第二个触发器激励信号,第二个触发器输出提供第一个触发器复位信号。

因此,在画Q1、Q2的电压波形时,必须把两个触发器合为一体来处理,才能得出正确的结果。

例如,第一个触发器在A信号上升沿到来之前,状态保持为0。

由于D2=Q1=0,第二个触发器虽有CP信号作用,状态也维持为0。

而当A信号上升沿到来时,第一个触发器状态转换为1,从而D2=Q1=1。

只要CP信号上升沿到达,则第二个触发器状态Q2转换为1,而使

=0,随之将第一个触发器复位为0,使得D2=Q1=0。

此后,在CP信号作用下第二个触发器状态也由于此时的D2=Q1=0转换为0。

从而使

=1,解除了对第一个触发器的复位作用。

然后,再等待A信号的上升沿到达,重复上述过程。

【解答】

依照解题指导画出输出端Q1、Q2的波形,如图4-17所示。

图4-17

【试题4-14】图4-18(a)电路的输入波形如图4-18(b)所示,试画输出Q1、Q2波形。

设初始状态均为0。

(a)(b)

图4-18

【解题指导】

本题与上例类似,整个电路由两个触发器串接而成,且相互关联。

第一个触发器输出提供第二个触发器激励信号,第二个触发器输出提供第一个触发器复位信号,构思巧妙,画波形图时要分时段逐段画出,切忌操之过急。

【解答】

由图4-18(a)电路可见,触发器FF1是一个T触发器,其时钟脉冲是A波形,上升边触发;触发器FF2是一个由JK触发器构成的D触发器,其输入是Q1,其时钟脉冲是B波形,下降边沿触发。

由此可得触发器的输出波形如图4-19所示。

图4-19

说明如下:

1.t≤t0时,Q1=Q2=0,处于初始状态

2.t<t1时,因A波形没有上升边沿存在,Q1继续为0状态;因为Q1=0,Q2也保持0状态。

3.t=t1时,A上升边沿到达,由于Q2=0,

=1,即FF1的

端的信号为1,复位不起作用,触发器FF1翻转为1状态;因t=t1-时Q1=0,故Q2仍为0状态。

4.t=t2时,B波形下降边沿到达,触发器FF1的1状态被移入触发器FF2中,使Q2=1,同时将触发器FF1复位为Q1=0。

5.t=t3时,B波形下降边又到达,因此时Q1=0,所以Q2变为0状态;而触发器FF1因没有时钟脉冲上升边沿出现而保持0状态。

以下类同。

【习题4-15】主从RS触发器输入信号的波形如题图4-5(a)、(b)所示。

已知触发器的初态Q=1,试画出Q端的波形。

(a)(b)

题图4-5

【习题4-16】主从JK触发器输入信号的波形如题图4-6(a)、(b)所示。

已知触发器的初态Q=1,试画出Q端的波形。

(a)(b)

题图4-6

【习题4-17】主从JK触发器输入信号的波形如题图4-7(a)、(b)所示。

试画出Q端的波形。

(a)(b)

题图4-7

【习题4-18】下降沿触发的边沿JK触发器的输入波形如题图4-8(a)、(b)所示。

试画出Q端的波形。

(a)(b)

题图4-8

【习题4-19】维持-阻塞D触发器的输入波形如题图4-9(a)、(b)所示。

试画出Q端的波形。

(a)(b)

题图4-9

【习题4-20】电路如题图4-10所示,设各触发器的初态为0,画出在CP脉冲作用下Q端波形。

题图4-10

【习题4-21】试分析题图4-11(a)、(b)所示的两个触发器电路,分别写出它们的次态方程表达式,说明其能完成的逻辑功能。

(a)(b)

题图4-11

【习题4-22】逻辑电路如题图4-12所示。

已知CP和X的波形,试画出Q1和Q2的波形,设触发器的初态均为0。

题图4-12

【习题4-23】逻辑电路如题图4-13所示。

已知CP和A的波形,试画出触发器Q端的波形,设触发器的初态为0。

题图4-13

【习题4-24】边沿JK触发器构成的电路如题图4-14所示。

(1)分析电路的功能,画出CP与VO的波形;

(2)若已知门的延迟时间tpd=10nS,JK触发器的tpd=30nS,要想得到tW=70nS的正脉冲,电路应该作如何改动?

题图4-14

【习题4-25】三种不同触发方式的D触发器的逻辑符号、时钟CP和信号D的波形如题图4-15所示,画出各触发器Q端的波形图。

各触发器的初始状态为0。

题图4-15

【习题4-26】维持-阻塞D触发器组成的电路如题图4-16所示。

画出在时钟脉冲CP作用下,Q1、Q2端的波形。

题图4-16

【习题4-27】维持-阻塞D触发器组成的电路如题图4-17(b)所示。

输入波形如题图4-17(a)所示。

设触发器的初始状态Q2Q1=00,画出Q1、Q2端的波形。

(a)(b)

题图4-17

【习题4-28】触发器电路和输入波形如题图4-18所示,试写出Q1、Q2的状态方程并画出输出端Q1、Q2的波形。

题图4-18

【习题4-29】附表所示为XY触发器的特性表,试写出XY触发器的特性方程,并画出其状态转换图。

【习题4-30】题图4-20所示为XY触发器的状态转换图。

根据状态图中状态及其次态间的激励条件,写出XY触发器的特性方程,并写出其功能表。

题图4-20

【习题4-31】若已知XY触发器的特性方程为

试据其画出这个触发器的状态转换图和特性表。

【习题4-32】某触发器设为XY触发器特性表如附表所示。

要求:

(1)画出此XY触发器的状态转换图;

(2)试分别用D触发器,JK触发器和RS触发器转换成XY触发器,写出转换电路的表达式。

【习题4-33】T触发器组成电路如题图4-23所示。

分析电路功能,写出电路的状态方程,并画出状态转换图。

题图4-23

【习题4-34】RS触发器组成电路如题图4-24所示。

分析电路功能,写出电路的状态方程,并画出状态转换图。

题图4-24

【习题4-35】JK触发器组成电路如题图4-25所示。

分析电路功能,画出状态转换图。

题图4-25

【习题4-36】一个下降沿触发的JK触发器,设初始状态为0,如给定CP、J、K的波形如题图4-26所示,试画出相应的输出Q和

的波形图。

图4-26