计算机组成原理郑秋梅习题教学内容.docx

《计算机组成原理郑秋梅习题教学内容.docx》由会员分享,可在线阅读,更多相关《计算机组成原理郑秋梅习题教学内容.docx(18页珍藏版)》请在冰豆网上搜索。

计算机组成原理郑秋梅习题教学内容

计算机组成原理-郑秋梅_习题

第二章

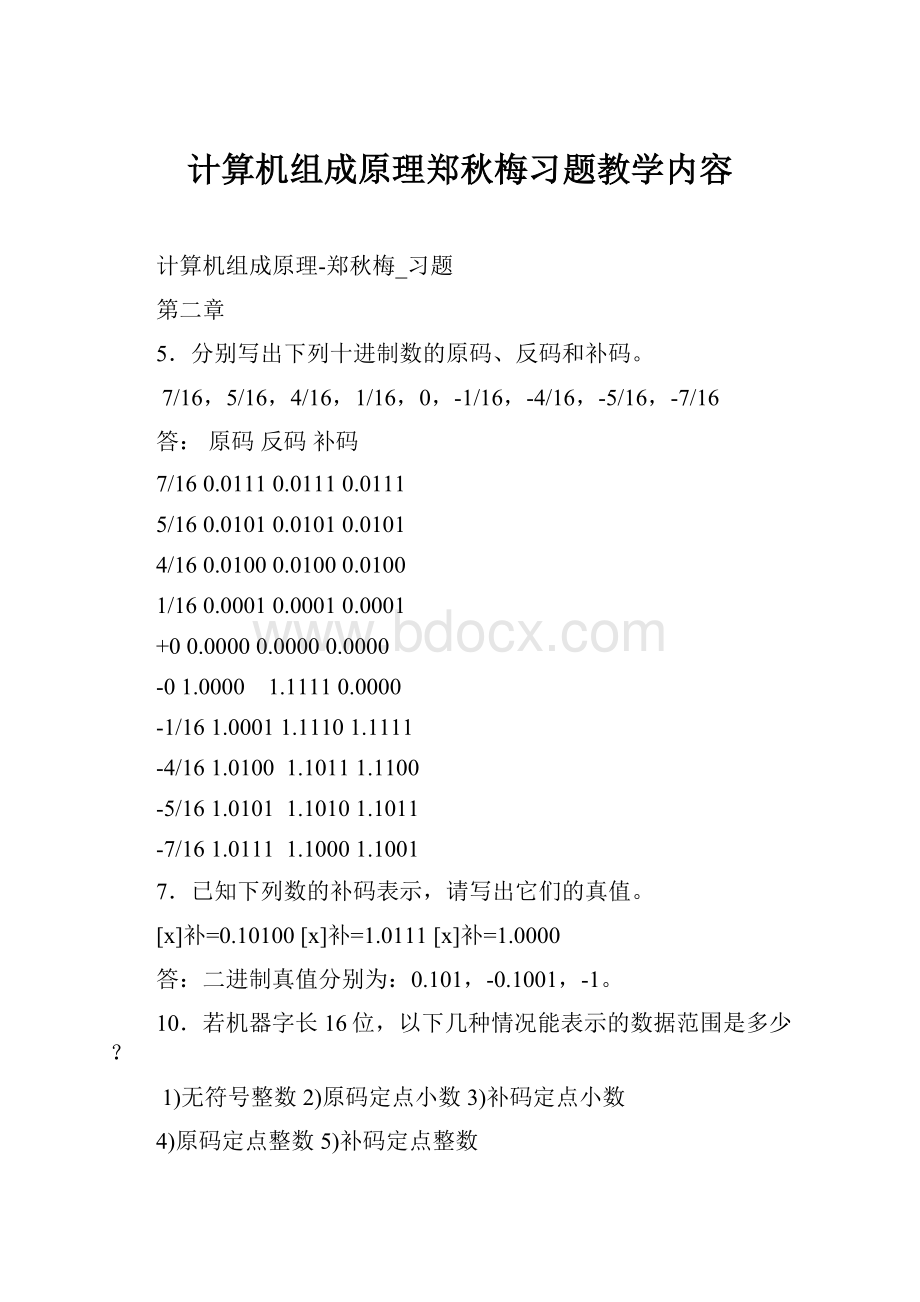

5.分别写出下列十进制数的原码、反码和补码。

7/16,5/16,4/16,1/16,0,-1/16,-4/16,-5/16,-7/16

答:

原码反码补码

7/160.01110.01110.0111

5/160.01010.01010.0101

4/160.01000.01000.0100

1/160.00010.00010.0001

+00.00000.00000.0000

-01.00001.11110.0000

-1/161.00011.11101.1111

-4/161.01001.10111.1100

-5/161.01011.10101.1011

-7/161.01111.10001.1001

7.已知下列数的补码表示,请写出它们的真值。

[x]补=0.10100[x]补=1.0111[x]补=1.0000

答:

二进制真值分别为:

0.101,-0.1001,-1。

10.若机器字长16位,以下几种情况能表示的数据范围是多少?

1)无符号整数2)原码定点小数3)补码定点小数

4)原码定点整数5)补码定点整数

答:

1)无符号整数0~216-12)原码定点小数-(1-2-15)~1-2-15

3)补码定点小数-1~1-2-154)原码定点整数-(215-1)~215-1

5)补码定点整数-215~215-1

14.将下列数转换为IEEE单精度浮点数:

1)28.75

解:

1)十进制数28.75转化为二进制数:

11100.11B,规格化为11100.11=1.110011×24

该数为正,符号位=0;移码表示的阶码=10000011;尾数=11001100000000000000000

以短浮点数格式存储该数为0,10000011,11001100000000000000000=41E60000H

21.某循环冗余校验码的生成多项式为x3+x2+1,若发送信息位1111和1100,则CRC码分别为什么?

接收端收到的CRC码:

0000000、1001111、0010111、1011000中哪些是发生了错误的?

答:

A(x)=1111和1100 左移r=3位后A(x)·x3=1111000和1100000

g(x)=x3+x2+1=1101 (r+1=4位)

A(x)·x3/g(x)=1011+111/1101和1001+101/1101

A(x)·x3+R(x)=1111111和1100101-----这就是2个CRC码

接收到的CRC码除以生成多项式余数不为0的出错:

1001111、1011000。

第三章

9.用原码一位乘法和原码两位乘法分别计算X×Y:

a.X=-0.11011,Y=0.11101

解:

a原码一位乘|X|=00.11011→寄存器B,|Y|=0.11101→寄存器C,0→寄存器A。

部分积A

乘数C

运算过程

00.00000

1

1

1

0

1

C5=1,+|X|

+

00.11011

00.11011

部分积右移一位

→

00.01101

1

1

1

1

0

C4=0,+0

+

00.00000

00.01101

部分积右移一位

→

00.00110

1

1

1

1

1

C3=1,+|X|

+

00.11011

01.00001

部分积右移一位

→

00.10000

1

1

1

1

1

C2=1,+|X|

+

00.11011

01.01011

部分积右移一位

→

00.10101

1

1

1

1

1

C1=1,+|X|

+

00.11011

01.10000

部分积右移一位

→

00.11000

0

1

1

1

1

由于两数异号,所以得X×Y =-0.1100001111

10.用补码一位乘法和补码两位乘法分别计算X×Y:

a.X=-0.11011,Y=0.11101

a补码一位乘部分积0→寄存器A,[X]补=11.00101→寄存器B,[Y]补=0.11101→寄存器C。

用Booth法求解过程如下:

部分积A

乘数C

附加位说明

00.00000

0.

1

1

1

0

10

C5C6=10,+[-X]补

+

[-X]补

00.11011

00.11011

右移一位

→

00.01101

1

0

1

1

1

01

C5C6=01,+[X]补

+

[X]补

11.00101

11.10010

右移一位

→

11.11001

0

1

0

1

1

10

C5C6=10,+[-X]补

+

[-X]补

00.11011

00.10100

右移一位

→

00.01010

0

0

1

0

1

11

C5C6=11,+0

+

0

00.00000

00.01010

右移一位

→

00.00101

0

0

0

1

0

11

C5C6=11,+0

+

0

00.00000

00.00101

右移一位

→

00.00010

1

0

0

0

1

01

C5C6=01,+[X]补

+

[X]补

11.00101

11.00111

1

0

0

0

1

最后一步不移位

所以[X×Y]补=11.0011110010,X×Y=-0.1100001111

12用原码加减交替法和补码加减交替法计算X÷Y。

a.X=-0.1001Y=0.1101

解:

a加减交替法|X|=00.1001,|Y|=00.1101,|Y|变补=11.0011

被除数/部分余数A

商C

0

0

0.1

0.11

0.110

0.1101

说明

00.1001

0

0

0

0.

0

-|Y|

+|Y|变补

11.0011

11.1100

0

0

0

0.

0

余数<0,商0,左移一位

←

11.1000

0

0

0

0.

0

+|Y|

00.1101

+|Y|

00.0101

0

0

0

0.

1

余数>0,商1,左移一位

←

00.1010

0

0

0

1.

0

+|Y|变补

11.0011

-|Y|

11.1101

0

0

0

1.

0

余数<0,商0,左移一位

←

11.1010

0

0

1

0.

0

+|Y|

00.1101

+|Y|

00.0111

0

0

1

0

1

余数>0,商1,左移一位

←

00.1110

0

1

0

1

0

+|Y|变补

11.0011

-|Y|

00.0001

0

1

0

1

1

余数>0,商1

00.0001

所以商Q=-0.1011,余数r=-0.0001×2-4。

a补码加减交替法[X]补=11.0111,[Y]补=00.1101,[-Y]补=11.0011

被除数/余数A

商C

0

0

0.1

0.11

0.110

0.1101

说明

11.0111

0

0

0

0.

0

[X]补和[Y]补异号,加除数

+[Y]补

00.1101

00.0100

0

0

0

0.

1

余数和除数同号,商1

←

00.1000

0

0

0

1.

0

,左移一位下次减除数

+[-Y]补

11.0011

11.1011

0

0

0

1.

0

余数和除数异号,商0

←

11.0110

0

0

1

0.

0

左移一位,下次加除数

+[Y]补

00.1101

00.0011

0

0

1

0.

1

余数和除数同号,商1

←

00.0110

0

1

0

1.

0

左移一位,下次减除数

+[-Y]补

11.0011

11.1001

0

1

0

1

0

余数和除数异号,商0

←

11.0010

1

0

1

0

0

左移一位,下次加除数

+[Y]补

00.1101

11.1111

←

11.1111

1

0

1

0

1

末尾恒置1

商[Q]补=1.0101,余数[r]补=11.1111×2-4。

第四章

12.某机器的16位单字长访内指令的格式如下:

4

2

1

1

8

操作码

Mode

@

I

D

其中,D为立即数或形式地址,补码表示;Mode为寻址模式,0表示立即寻址,1表示直接寻址,2表示基地址寻址,3表示相对寻址;@为间址标志,@=1表示间接寻址,@=0表示直接寻址;I为变址标志,I=1表示变址寻址,I=0表示非变址寻址。

设PC、Rx、Rb分别为指令计数器、变址寄存器、基址寄存器,EA为有效地址,试解答下列问题:

(1)该指令格式能定义多少种不同的操作?

(2)试写出立即寻址、直接寻址、基址寻址、变址寻址、相对寻址方式中计算有效地址EA的表达式。

(3)设基址寄存器为16位,在基址寻址时,可寻址的主存地址范围是多少?

(4)间接寻址时,可寻址的主存地址范围是多少?

若采用多重间址,可寻址的主存地址范围又是多少?

解:

(1)24=16。

(2)立即寻址:

无EA

直接寻址:

EA=D;D为指令中给出偏移量

基址寻址:

EA=(Rb)+D;

变址寻址:

EA=(Rx)+D;

相对寻址:

EA=(PC)+D;PC为程序计数器,D为偏移量

(3)0~216-1

(4)间接寻址可寻址的主存地址范围为0~216-1,多重间址可寻址的主存地址范围为0~215-1。

13.某机的指令格式如下:

1510

98

70

操作码

Mode

D

其中,D为立即数或形式地址,补码表示;Mode为寻址模式,0表示直接寻址,1表示用变址寄存器Rx1进行寻址,2表示用变址寄存器Rx2进行寻址,3表示相对寻址。

若已知(PC)=1000H,Rx1=0005H,Rx2=1005H,请计算出下列指令的有效地址:

①8442H②4545H

解:

①8442H=1000010001000010

因为Mode=0,所以为直接寻址,EA=D=0042H

②4545H=0100010101000101

因为Mode=1,所以用变址寄存器Rx1寻址,EA=(Rx1)+D=0005H+45H=004AH

16.某机字长32位,CPU的寻址范围为1MB,14个通用寄存器,共30条单字长双地址指令,要求有立即、直接、间接、寄存器、基址、相对寻址方式。

试设计其指令格式。

答:

14个通用寄存器需要4位来表示,30条单字长指令需要5位来表示,7种寻址方式需要3位来表示,剩下的20位用来表示操作数。

指令格式为:

5位操作码+3位寻址方式设置+4位寄存器操作数+20存储器操作数

第五章

9.用16K×1位的DRAM芯片组成64K×8位的存储器,要求:

(1)画出该存储器组成的逻辑图。

(2)设存储器读、写周期均为0.5μs,CPU在1μs内至少要访存一次。

试问采用哪种刷新方式比较合适?

两次刷新的最大时间间隔是多少?

答:

由题意知,存储器的总容量为64KB,故共需16条地址线(A0~A15),需要16K×1位DRAM芯片的个数为:

(64K×8位)/(16K×1位)=32片,芯片地址线占14位(A0~A13),高2位的地址线(A14~A15)作为2:

4译码器的输入端,4个输出端分别与4个DRAM芯片的片选信号端相连接。

其组成逻辑框图如下:

由已知条件可知,CPU在1μs内至少访存一次,故整个存储器的平均读/写周期与单个DRAM芯片的读/写周期基本相同,采用异步式刷新方式较合适。

动态MOS存储器两次刷新的最大时间间隔为2ms/128=15.625us,应该取15.5us比较合适(取存取周期的整数倍)。

16.某存储器容量为16M字,字长32位,模块数m=4,分别用顺序方式和交叉方式进行组织。

若存取周期T=200ns,数据总线宽度为32位,总线传送周期τ=40ns。

问:

顺序存储器和交叉存储器的平均存取时间、带宽各是多少?

答:

顺序存储器和交叉存储器连续读出4个字的信息总量都是:

q=32位×4=128位

顺序存储器连续读出4个字所需的时间是:

t1=m×T=4×200ns=800ns=8×10-7s;

交叉存储器连续读出4个字所需的时间是:

t2=T+(m-1)τ=200ns+3×40ns=320ns=3.2×10-7s

因此,顺序存储器和交叉存储器的带宽分别为:

W1=q/t1=128÷(8×10-7)=16×107(b/s)

W2=q/t2=128÷(3.2×10-7)=40×107(b/s)

19.容量为64块的cache采用组相联映像方式,字块大小为128个字,每4块为一组。

若主存容量为4096块,且以字编址。

(1)给出主存地址字段的组成及各段的长度;

(2)设Cache的初始状态为空,CPU从主存的第0号单元顺序读出500个字(一次读出一个字),重复读取上述数据10次,Cache的命中率为多少?

(3)若Cache的速度是主存速度的5倍,则增加Cache后比没有Cache时速度提高多少倍?

解:

(1)由每字块有128个字可得:

主存地址字段中字块内地址字段的长度w应为7位。

Cache容量为64块,每4块为一组,则Cache共有24个组,表示Cache组号的位数为4,表示组中块号的位数为2。

主存容量为4096块,Cache容量为64块,主存共分为4096/64=26个区,故地址字段中主存区号地址位数为6。

主存地址字段格式为:

区号地址(6位)

组地址(4位)

组内块号(2位)

字块内字地址(7位)

(2)Cache初始状态为空,每个字块中有128个字,故CPU第一次读500个字时,第0、128、256、384号单元,共有4次未命中,后9次重复读这500个字均命中,故命中率为:

[(500×10-4)/500×10]×100%=99.92%

(3)设Cache的存取周期为t,则主存存取周期为5t,没有Cache时,访问时间为5t×5000,有Cache后访问时间为t×(5000-4)+5t×4,故有Cache后速度提高的倍数为:

5t×5000/[t×(5000-4)+5t×4]-1=3.98

第六章

8.某机主要部件如图6-32所示。

⑴请补充各部件间的主要连接线,并注明数据流动方向。

⑵拟出指令ADD(R1),(R2)+的执行流程(含取指过程与确定后继指令地址)。

该指令的含义是进行加法操作,源操作数地址和目的操作数地址分别在寄存器R1和R2

中,目的操作数寻址方式为自增型寄存器间址。

其中:

LA—A输入选择器;

LB—B输入选择器;

C、D一暂存器。

解:

(1)各部件间的主要连线补充完成后如图所示:

移位器

ALU

LA

LB

IR

PC

C

D

R0

R1

R2

R3

MDR

MAR

M

+1

(2)指令ADD(R1),(R2)+的含义为:

((R1))+((R2))->(R2)

(R2)+1->R2

指令的执行流程如下:

(PC)->MAR;取指令

Read

M(MAR)->MDR->IR

(PC)+1->PC

(R1)->MAR;取被加数

Read

M(MAR)->MDR->C

(R2)->MAR;取加数

Read

M(MAR)->MDR->D

(11)(C)+(D)->MDR;求和并保存结果

(12)Write

(13)MDR->MM

(14)(R2)+1->R2;修改目的地址

14.某计算机共有操作控制命令62个,为了压缩整个控制字段长度,采用分组译码方法表示不同微命令,把互斥型微命令分在一个字段中,各字段中分别表示4个、10个、8个、15个、25个微命令,已知微指令字长28位,求:

⑴各个控制字段分别用几位二进制数编码。

⑵控制存储器最大容量是多少?

解:

第一个控制字段表示4个微命令,再增加1个不发出任何微命令的编码,共需表示5种情况,第1个控制字段需用3位二进制数编码,同理第2个控制器字段需用4位,第3个控制字段需用4位,第5个控制字段需用4位,第6个控制字段需用5位二进制数表示。

6个控制字段共需20位二进制数表示。

微指令字长28位,其余8位表示顺序控制字段,即下条微指令地址。

28=256,因此控存最大容量256个单元,每个单元28位。