半导体行业中DRAM的制造与测试.docx

《半导体行业中DRAM的制造与测试.docx》由会员分享,可在线阅读,更多相关《半导体行业中DRAM的制造与测试.docx(21页珍藏版)》请在冰豆网上搜索。

半导体行业中DRAM的制造与测试

半导体行业中DRAM的制造与测试

一、DRAM器件的基本介绍

二、DRAM器件的晶圆制造流程

三、DRAM器件的封装流程

四、DRAM器件的电性测试与良品率

五、DRAM器件晶圆制造的新工艺

一、DRAM的基本介绍

1.DRAM的基本介绍

A.内存的种类

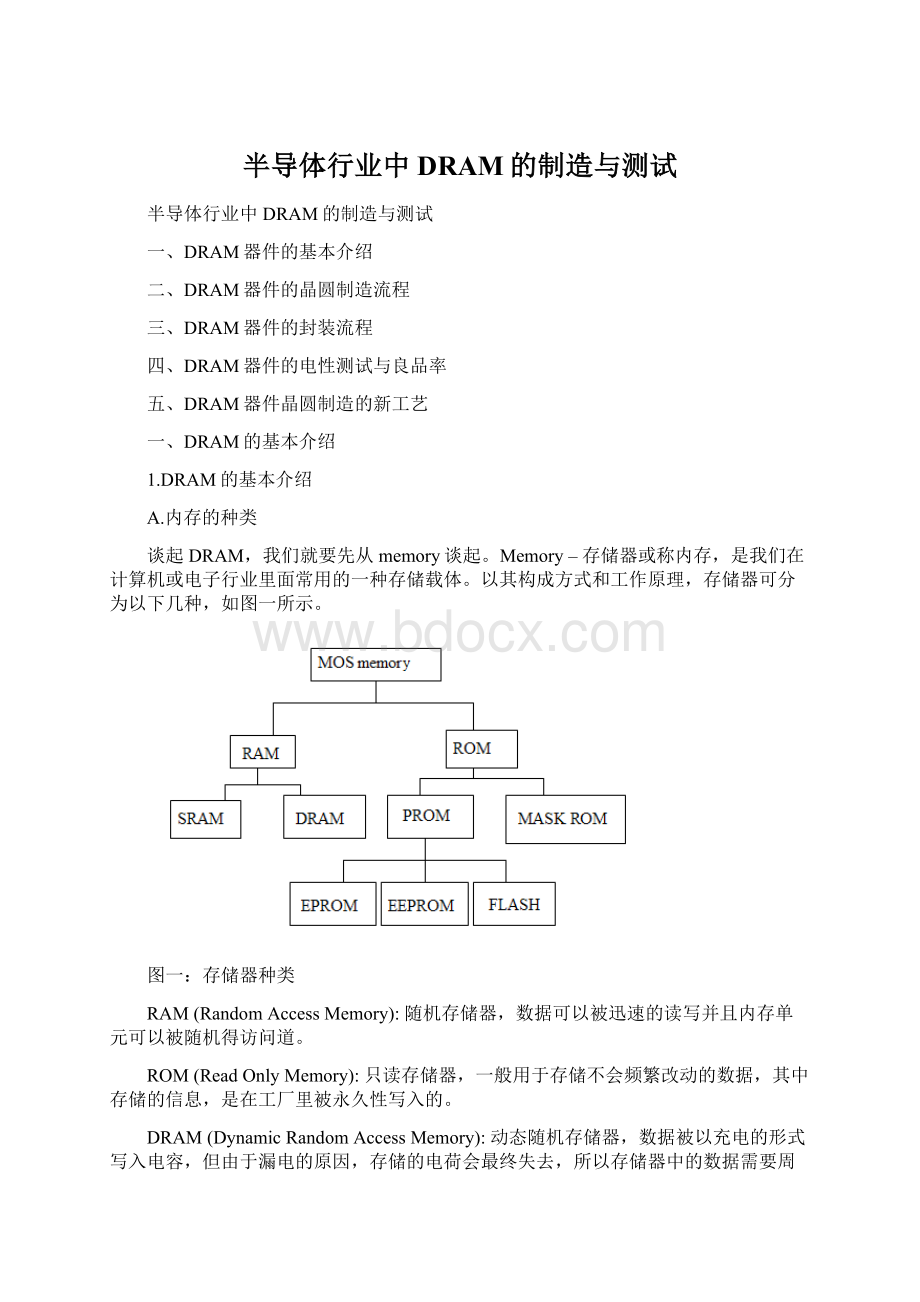

谈起DRAM,我们就要先从memory谈起。

Memory–存储器或称内存,是我们在计算机或电子行业里面常用的一种存储载体。

以其构成方式和工作原理,存储器可分为以下几种,如图一所示。

图一:

存储器种类

RAM(RandomAccessMemory):

随机存储器,数据可以被迅速的读写并且内存单元可以被随机得访问道。

ROM(ReadOnlyMemory):

只读存储器,一般用于存储不会频繁改动的数据,其中存储的信息,是在工厂里被永久性写入的。

DRAM(DynamicRandomAccessMemory):

动态随机存储器,数据被以充电的形式写入电容,但由于漏电的原因,存储的电荷会最终失去,所以存储器中的数据需要周期性地被更新,这也正是“动态”一词的来源。

一般来讲,一个最基本的存储单元由一个MOS管和电容所组成,而典型的DRAM需要5~50毫秒的数据更新周期。

SRAM(StaticRandomAccessMemory):

静态随机存储器,数据被存储在两个耦合的逻辑反向器中。

与DRAM相比,SRAM中的数据不需要被周期性的更新,而这也导致其具有低功耗的特点;典型的SRAM存储单元由6个MOS管所组成,但这也导致在同等的器件面积上,它所存储的数据量比DRAM少。

PROM(ProgrammableReadOnlyMemory):

可编程只读存储器

MaskROM(MaskReadOnlyMemory):

一种只读存储器,其中存储的信息是在晶圆的制造过程中,以掩模版的形式被复制在器件上。

EPROM(ElectricalProgrammableReadOnlyMemory):

电可编程只读存储器。

EEPROM(ElectricalErasableandProgrammableReadOnlyMemory):

电可编程/擦除只读存储器。

FLASH(FLASHElectricalErasableandProgrammableReadOnlyMemory):

闪存

B.DRAM市场的现状与发展

由于DRAM的特性,使其成为在计算机与通讯系统中使用最为广泛的半导体存储器形式。

而也因为其制造工艺的先进性,使其成为半导体制造工业的标杆,表一所给出的SIA(半导体产业协会)对半导体产品的产品参数所预测的“路线图”,就是以DRAM器件为代表所给出的。

产品年代

2001

2006

2012

线宽(nm)

150

100

50

存储器容量

1Gb

16Gb

64Gb

逻辑比特/cm2

380M

17B

芯片尺寸(mm2)

445

790

1580

最大连线水平

7

7-8

9

掩模层

23

24/26

28

缺陷密度(D/m)

875

490

250

芯片接口-I/O’s

1195

1970

3585

晶圆直径(mm)

300

300

450

表一:

半导体产业路线图–SIA

在半导体产业中,DRAM器件的销售利润额为370亿美元(2000年),占整个半导体市场份额的16%。

图二给出了DRAM市场利润额的变化图

图二:

DRAM市场利润额趋势图

由于DRAM制造工艺的不断发展,也使DRAM成为了一种低成本的内存器件,目前,其每个逻辑存储比特的制造成本已小于10-7美元,并且其制造成本还在以每年约26%的速率在继续下降。

图三给出了DRAM器件制造成本的下降趋势。

图三:

DRAM器件制造成本的下降趋势图

目前的DRAM生产技术已经发展到160nm工艺,每个存储单元的面积可以控制在以内。

当前主要的DRAM生产商是Samsung,Micro,LG-Hyundai,Hitachi,这几家生产商占到了DRAM市场份额的80%以上。

2.DRAM器件的工作原理

A.DRAM器件的基本结构

谈起DRAM器件的基本结构,我们要先从其最基本的存储单元(MemoryCell)说起,图四为DRAM存储单元逻辑示意图;图五为其存储单元晶圆剖面示意图。

从图四我们可以看出,每个DRAM存储单元是由一个MOS管,一个电容,一根字节线(WordLine或称行)和一根比特线(BitLine或称列)所组成的,而这就是典型的DRAM1T(Transistor)1C(Capacitor)存储单元结构(IBM公司于1968年发明)。

就是这样一个一个的存储单元组成了DRAM器件存储阵列,而存储阵列一般会占到整个DRAM器件面积的50~65%,其余的面积主要由外围电路所组成。

在每一个存储单元中,MOS管被字节线所控制,起到开关的作用,控制存储单元的读(Reading),写(Writing)与更新(refresh)。

在写操作中,电荷从比特线流入并被存储到电荷中;在读操作中,电荷从电容中流出并被反馈到比特线上。

从图五中也可以看出DRAM的基本存储单元是如何在晶圆的层叠结构中得以实现的。

图四:

DRAM存储单元逻辑示意图

图五:

DRAM存储单元晶圆剖面示意图

图六为DRAM器件存储阵列(MemoryArray)简易示意图,从左图可以看出在实际应用的DRAM器件中,使用的是一对比特线(BL/BL),这一对比特线与感应放大器(SA-SenseAmplifier)协作来进行DRAM器件的读操作(这一内容将在后续章节中详细说明)。

右图为DRAM器件存储阵列在晶圆上布局的简易示意图,纵向布局的为由多晶硅所构成的字节线,横向布局的为由钨所构成的比特线和有单晶硅所构成的活性区(AA-ActiveArea)。

从此图中的方框可以看出,如果设此器件的最小关键尺寸为F的话,一个DRAM存储单元所占的面积仅为A=4FX2F=8F2,可见,每个存储单元在器件表面上所占的面积是多么小,而这也正是DRAM器件较之其他存储器件存储密度大的原因。

图六:

DRAM器件存储阵列简易示意图。

图七所是的为在实际应用中的DRAM存储单元,其上图为通过电子扫描电镜,所照取的器件剖面图,其下图为DRAM存储单元逻辑俯视图。

通过其对应关系可以看出,外面用红色虚线勾勒出来的为存储单元的存储节点(即为电容),里面用黄色虚线勾勒出来的为由多晶硅所构成的MOS管的栅极。

从上图我们也可以清楚地看出DRAM器件中的隔离区(LOCOS-LocalOxide,局部氧化隔离区),由第一层金属层(Metal1-钨)所构成的比特线,由第二,三层金属层(Metal2,3-铝)所组成的互连线(interconnect)和四层多晶硅所组成的电容。

图七:

DRAM存储单元示意图

让我们从更近的角度来看DRAM器件的存储单元,图八为DRAM存储单元的放大示意图,器件内部的氧化物已被溶剂(BOE溶剂)去除掉,我们可以更清楚地看到上面的电容,中间的比特线和下面的字节线。

图八:

DRAM存储单元的放大示意图

下面我们再来看DRAM器件的存储阵列。

我们以IBM公司的256MbDRAM为例,图九所示为其实际器件俯视图与其逻辑示意图之间的对应关系;图十所示为其实际器件俯视图与实际器件剖面图之间的对应关系。

从中我们可以看出,DRAM器件的存储阵列主要就是由字节线和比特线组成的矩阵网络所串起的海量存储单元所构成的。

图九:

DRAM器件俯视图与其逻辑示意图之间的对应关系

图十:

DRAM器件俯视图与剖面图之间的对应关系

那么,DRAM器件的外围电路又是如何组成的呢?

图十一为DRAM器件的简易逻辑示意图,从中我们可以看出DRAM器件的外围电路主要是由行地址解码器(RowAddressDecoder)、列地址解码器(ColumnAddressDecoder)、行输入缓冲器(XInputBuffer)、列输入缓冲器(YInputBuffer)、写驱动器(WriteDriver)、输入/输出口(DeviceI/O&Buffer)和感应放大器(SenseAmplifier)所组成。

行、列地址解码器的作用是当外部发出指令要对某一存储单元进行读/写操作时,它们对外部指令中的行、列地址进行解码,以得出DRAM器件内部存储阵列的地址,进而控制字节线和比特线,将其打开,从而对指定的存储单元进行读/写操作。

感应放大器的功能将在后续章节中详细说明。

图十一:

DRAM器件简易逻辑示意图

B.DRAM器件的工作原理

在这一章节中,我们将主要从四方面介绍DRAM器件的工作原理,它们是DRAM器件的写操作,读操作,感应放大和数据更新,下面先让我们从DRAM器件的写操作开始。

DRAM器件的写操作工作原理相对容易理解,请见图十二,从图中我们可以看出,存储单元--电容的一个极板上始终都被加上Vcc/2的电压,而当要对某一存储单元进行写操作时,这一存储单元的字节线上会被加以电压Vccp(Vccp>Vcc+Vt),这一电压会被加到这一存储单元开关MOS管的栅极上,这一电压大于MOS管的开启电压,这样,MOS管导通,就可以对这一存储单元进行写操作了。

当要写入1时,比特线上会加以电压Vcc,而这一电压会通过导通的MOS管,由其源极传导到漏极并最终加到存储电容的另一极板上(如左图所示);与此类此,当要写入0时,则加以电压0v(如右图所示)。

存储单元中所储存的数据是0还是1,由电容两极板间的电压差方向所定。

当存储单元被执行写操作以后,其存储电容上所储存的电荷电量由公式Q=C*V=Ccell*Vcc/2。

我们会在下面的章节中说明,存储电容上所储存的电荷电量Q越大,其维持漏电的时间也就越长,而数据更新所需的周期也就越长,这样也就可以使器件减少功耗,而从上面的公式也可以看出,要想增大Q,增大电容的容值,是唯一实际可行的办法(增大Vcc反而会增加功耗),而在后面将要说明的DRAM器件的读操作中,增大电容容值,也会使得DRAM器件在读取数据时更加容易和准确。

在本文的第二章中,我们会介绍在DRAM器件晶圆的制造的过程中,在工程上是如何通过增大电容的极板面积从而实现增大其电容容值的。

图十二:

DRAM器件写操作示意图。

下面,我们将阐述DRAM器件的读操作和感应放大。

在DRAM器件进行读操作时,进行读操作的存储单元的字节线被打开,原先存储在电容中的电荷被释放出,由于此存储单元的开关MOS管已被字节线打开,这样,释放出的电荷会通过MOS管继而释放到比特线上,由于存在由比特线所产生的等效电容,所以,在电容电荷释放过程中,所产生的电压变化由以下公式得出。

DRAM器件就是根据这一电压变化的方向来判定其存储单元中所存储的数据是0还是1。

图十三:

DRAM器件读操作示意图

但是,还有一个问题,让我们举一个例子来说明:

假设我们的DRAM器件的工作电压为Vcc=,电容容值为Ccell=50fF,比特线的等效电容为CBL=300fF,电容中所存储的电荷电量Q=CV=dV*(Ccell+CBL)=(Vcc/2)*Ccell,这样,我们可以得出,在电容放电的过程中,电压的变化量为dV=2)*[50/(300+50)]=。

一般来讲,目前DRAM器件的dV也就是在80~200mv之间。

这样小的电压变化量,DRAM器件很难在读取数据的时候准确判断出存储的数据到底是0还是1,而这也就是我们需要在DRAM器件中加入感应放大器的原因。

感应放大器(SenseAmplifier)的工作原理请见图十四,其工作电路示意图请见左图,工作过程示意图请见右图。

简而言之,它的功能就是将DRAM器件进行读操作时所产生的“微小”的dv放大成工作电压Vcc。

举例说明,如果存储单元中所储存的数据为1,在进行读操作时,字节线的电压首先被拉高到Vccp,存储单元开关MOS管被打开,此存储单元处于读/写激活状态,然后一对比特线与Vcc/2电压断开,继而,在读出1时,BL线上产生了正向的dv电压,此电压导致右下角的NMOS管被开通,使得N节点上的负电压加在了BL线上和左上角PMOS管的栅极上并使其导通,最终,P节点上的Vcc电压就通过此MOS管加在了BL线上,这样,外部器件就可以容易而准确地根据一对比特线上的电压差是+Vcc还是-Vcc来判断出存储单元中储存的数据是0还是1。

图十四:

DRAM器件感应放大器工作原理示意图

最后,再让我们看一下DRAM器件的数据更新(Refresh)。

由于DRAM器件器件的数据存储主要是由电容所完成的,而由于电容和开关MOS管的漏电流,使得电容中所存储的电荷很快就会漏光,这样,就需要我们周期性地对每个存储单元进行数据更新以阻止这样的现象发生。

周期性的数据更新其实很简单,就是对存储单元进行一次读/写操作,把读出的数据原样再写回去。

目前,市场上大多数的DRAM器件的数据更新周期在5~50ms之间,一些新的DRAM器件甚至可以延长到100~200ms。

3.DRAM器件的芯片介绍

A.DRAM器件的管脚介绍

让我们先从简单的1KbDRAM器件开始对其芯片进行介绍。

图十五为1kbDRAM器件功能管脚示意图,其中所示的为DRAM器件工作所必需的一些管脚,如:

电源管脚(Vss,Vdd),片选管脚(CE),读/写控制管脚(R/W),数据输入(Din)和输出管脚(Dout)以及行、列地址输入管脚(R1~R5,C1~C5)。

因为其各有5个行、列地址管脚,所以它所能控制的内存大小为(25)2=1024b,即为1Kb。

图十六为其内部逻辑电路示意图,因其内部工作原理已在上一章中进行了讨论,在这里就不再赘述了。

图十五:

1kbDRAM器件功能管脚示意图

图十六:

1kbDRAM器件逻辑电路示意图

B.DRAM器件工作时序

图十七,十八和十九分别描述的是DRAM器件读,写和数据更新操作的工作时序,因其工作原理已在上一章中论述过,在此就不再重复了。

在这里需要说明的是其中的一些时域参数:

tRC(Readcycletime):

读操作周期

tAC(Accesstime):

访问时间

tWC(Writecycletime):

写操作周期

tAW(AddresstoWritedelaytime):

写激活与地址输入之间的时间延迟

tWP(Writepulsewidth):

写脉冲宽度

图十七:

DRAM器件读操作工作时序图

图十八:

DRAM器件写操作工作时序图

图十九:

DRAM器件数据更新工作工作时序图

二、DRAM器件的晶圆制造的工艺与流程

IC产品的晶圆制造工艺非常复杂,以目前市场上主流的64MbDRAM为例,它的生产工艺中需要4层多晶硅、3层金属互连层,需要8次CMP工艺,21层光照掩模,这样的一个DRAM器件在其晶圆制造过程中大约需要总共300多步工艺。

在业界中,为了以示区分,将IC产品的晶圆制造工艺分为了前段和后段:

前段主要包括了底层器件的制造工序;后段以金属互连层的制造工序为主,在本文中,我们也将按照前段、后段逐一加以论述。

在这一章中,为了论述方便,我们还加入了大量晶圆剖面示意图来说明DRAM器件的晶圆制造工艺,在这些示意图中,左图显示的是存储阵列的结构而右图显示的是外围电路的结构。

1.DRAM器件晶圆制造的前段工艺

首先,我们需要的单晶硅基材类型为(100)晶向,单位面积电阻为10+/的P型硅片,并且要在上面生长出7um的外延层(Epi)。

接着,会在晶圆上在900C的温度下生长出100A的二氧化硅层(生长这一层二氧化硅的目的是为了避免应力很大的SiN将下面的单晶硅晶格压坏),然后再在其上在760C的温度下淀积一层1500A的SiN,随后再在其上涂敷光阻以对SiN层进行刻蚀,如图二十所示。

在对SiN刻蚀后,再以其为掩模版,继续对硅片进行刻蚀,深度大约为3700A,以形成AA(活性区)之间的STI(ShallowTrenchIsolation,浅沟道隔离槽),如图二十一所示。

所最终形成的AA/STI如图二十二中的电子扫描电镜的照片所示。

图二十:

AA(ActiveArea)区域刻蚀Hardmask(SiN)的形成

图二十一:

STI(浅沟道隔离槽)的形成

图二十二:

AA/STI俯视图

下一组工艺的目的是向STI重点及二氧化硅以最终形成AA区域之间的隔离层。

首先是用HDP(HighDensityofPlasma,高密度等离子体)工艺在整片晶圆上淀积硅的氧化物,如图二十三所示。

然后,再使用CMP(ChemicalMechanicalPolish,化学机械抛光)工艺将多余的SiN和二氧化硅磨去,这样就最终完成了STI中氧化隔离物的充填,如图二十四所示。

图二十三:

HDP淀积后的STI

图二十四:

填充后的STI

下一组工序主要是通过Implant(离子注入)工艺以形成器件中的N井与P井。

在离子注入之前,为了防止大能量注入的离子对下面的单晶硅的晶格造成损伤,需要在晶圆上生长一层牺牲氧化物(SacrificeOxide)(800C,50A),这层氧化物会保护下面单晶硅的晶格,其会在离子注入以后被除去(顾名为牺牲氧化物)。

在牺牲氧化物生长完成后,以光阻为掩蔽物,依次进行外围电路的N井和P井的离子注入,如图二十五,二十六所示;和存储阵列的N井和P井的离子注入,如图二十七所示。

图二十五:

外围电路N井的离子注入(P1M150E3T00,磷离子注入,注入能量为1M电子伏特,注入密度为CM3,注入角度为垂直(0度角)注入)

图二十六:

外围电路P井的离子注入(B180K150E3T07,硼离子注入,注入能量为180K电子伏特,注入密度为CM3,注入角度为偏离法线角7度(7度角)注入)

图二十七:

存储阵列N井和P井的离子注入(P1M150E3T00,磷离子注入,注入能量为1M电子伏特,注入密度为CM3,注入角度为垂直(0度角)注入;B180K300E2T07,硼离子注入,注入能量为180K电子伏特,注入密度为CM3,注入角度为偏离法线角7度(7度角)注入)

下一组工序主要包括了形成MOS管栅极氧化物的工艺。

在淀积多晶硅之前需要先生长栅极氧化物,在800C的温度下,用湿法工艺生长一层77A厚的氧化物薄膜。

然后再在530C的温度下,淀积800A的多晶硅层,随后再在565C的温度下淀积1000A的WSi(硅和钨的合金)(淀积WSi的目的是为了减少以后Metal1和栅极连接时的连接电阻(ContactResistance)。

在其上再用PE(PlasmaEnhancement,增强型等离子体)工艺淀积SiON(400C,580A),这一层是做为后续光刻(Photo-Etch)曝光(Expose)工艺中的防反射层(ARC–AntiReflectionCoat)。

最后一层是在760C温度下,淀积1320A厚的SiN层,这一层的目的是保护下面的栅极,最终的结果如图二十八所示。

随后,还有两步退火工艺:

一步为在800C温度下,N2的环境中,60分钟的退火工艺,这一步是为了使多晶硅与WSi形成合金,以降低阻值;另一步是在1000C的温度下,N2的环境中,30秒的快速热退火工艺(RTA–RapidThermalAnneal),这一步工艺的目的是为了修复在前步离子注入工艺中所伤害的单晶硅晶格。

最后,为了形成栅极,需要用两步光刻工艺对以上各层进行刻蚀(第一步刻蚀SiN,SiON;第二步刻蚀WSi,Poly),所最终形成的栅极如图二十九所示。

从以上工艺中可以得知,在这种DRAM器件的晶圆制造工艺中,栅极是由四层所组成的(Poly+WSi+SiON+SiN),图三十给出了各层的厚度,它们统称为栅极堆栈(GateStack)。

图三十一给出了栅极形成后的俯视图,横向亮白的区域为活性区(AA),纵向黑色的为栅极。

图二十八:

栅极的淀积

图二十九:

栅极的形成

图三十:

栅极堆栈(GateStack)的组成图三十一:

AA与栅极的俯视图

下面的工序包括了MOS管源漏极形成的工艺。

首先使用在700C的温度下,N2的环境中,30秒的快速热退火工艺(RTA),这一步RTA工艺是为了修复在前步栅极刻蚀中所伤害的单晶硅的晶格。

下一步是使用离子注入工艺(P020K250E3T00,磷离子注入,注入能量为20K电子伏特,注入密度为CM3,注入角度为垂直(0度角)注入)形成轻掺杂的源漏极(LDD–LightlyDopenDrain),如图三十二所示。

随后的工艺是形成Spacer,Spacer对栅极堆栈形成绝缘保护,减少其应力,同时也是为了在后步源漏极离子注入中最终形成优化的源漏极轮廓产生作用。

其形成工艺如下:

首先在760C的温度下,在晶圆上淀积一层500A的SiN,然后再对其进行光刻,所最终形成的形状如图三十三所示。

再Spacer形成后,就可以为源漏极的最终形成进行重度掺杂了,首先用离子注入工艺对PMOS管的源漏极进行掺杂(BF025K500E5T00,硼氟离子注入,注入能量为25K电子伏特,注入密度为5X10E15/CM3,注入角度为垂直(0度角)注入);然后再对NMOS管的源漏极进行掺杂(As015K430E5T00,砷离子注入,注入能量为15K电子伏特,注入密度为CM3,注入角度为垂直(0度角)注入),所最终形成的源漏极如图三十四所示。

图三十二:

LDD(轻掺杂的源漏极)的形成

图三十三:

Spacer的形成。

图三十四:

源漏极的形成

下面的工序是在晶圆上淀积硼磷玻璃(BPSG–BoronPhosphorusSiliconGlass)。

首先在480C的温度下淀积8500A的硼磷玻璃,由于器件表面栅极的存在,使得淀积后的晶圆表面并不平整,为解决这一问题,需要在800C的温度下,N2的环境中,对晶圆表面进行60分钟的回流(Reflow)平整化,回流前后晶圆表面的变化请见图三十五。

在回流后,硼磷玻璃的厚度大致会减少到7800A左右,然后再用CMP工艺将其最终平整到5800A左右,请见图三十六。

图三十五:

回流前后硼磷玻璃表面的比较

图三十六:

淀积硼磷玻璃

下面的工艺是为了形成源极与电容、漏极与比特线(Metal1)之间的连接孔。

首先使用光刻工艺将源漏极上方的硼磷玻璃刻蚀掉(图三十七为刻蚀后的俯视图),然后再在530C的温度下在晶圆上淀积3000A的多晶硅,最后再利用CMP工艺将连接孔以外的多晶硅磨去,这样就最终形成了连接孔,如图三十八所示。

图三十七:

源、漏极与电容、比特线间连接孔刻蚀后的俯视图

图三十八:

源、漏极与电容、比特线间连接孔的形成

下面的一组工序是DRAM器件晶圆生产过程中最核心的工艺即存储单元电容的形成。

第一步是在晶圆表面继续淀积23500A的硼磷玻璃,随后还是回流平坦化工艺(800C温度,N2,20分钟),然后再利用光刻工艺对其进行光刻以为以后电容的形成留出空间,刻蚀后的深孔直径大约为,如图三十九所示,深孔刻蚀后的俯视图如图四十所示。

第二步是形成电容的一个极板:

首先在530C的温度下,在晶圆上淀积300A的多晶硅,这层多晶硅也会附着在深孔的周壁上,然后再在其上在568C的温度下,淀积530A的Rugged-Poly,这层Rugged-Poly也就是电容的第一个极板,而淀积Rugged-Poly的目的也正是向前文所论述到的那样,是为了增加电容极板的表面积,此时,