第13章PCI总线接口mpc83xx中文手册.docx

《第13章PCI总线接口mpc83xx中文手册.docx》由会员分享,可在线阅读,更多相关《第13章PCI总线接口mpc83xx中文手册.docx(91页珍藏版)》请在冰豆网上搜索。

第13章PCI总线接口mpc83xx中文手册

第十三章PCI总线接口

PCI总线接口遵守PCI本地总线规范Rev.2.3。

对PCI复杂特性的介绍已经超出了本手册的范围。

本章介绍PCI控制器,并提供PCI总线操作的基本说明。

特别着重介绍该设备是如何实现PCI规范的。

关于PCI总线的全面说明,整合PCI设备的系统的设计者应参考相应的规范。

注意

很多可用的PCI文献将一个16位数称为WORD(字),将一个32位数称为DWORD(双字)。

由于它与本手册使用的术语不一致,所以本章不使用术语“字”和“双字”,而使用位数或字节数指示确切的数。

13.1绪论

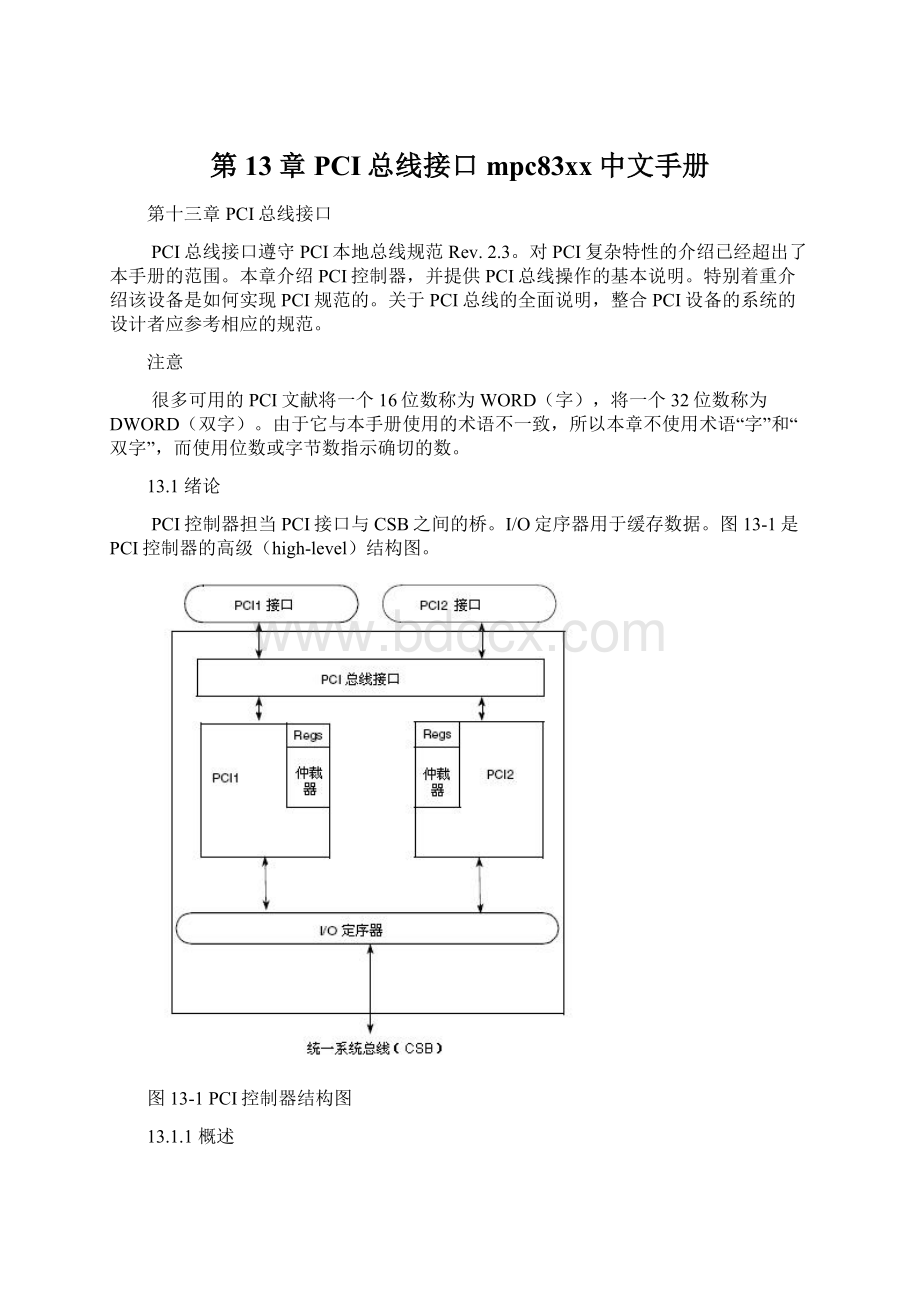

PCI控制器担当PCI接口与CSB之间的桥。

I/O定序器用于缓存数据。

图13-1是PCI控制器的高级(high-level)结构图。

图13-1PCI控制器结构图

13.1.1概述

MPC8349E包括两个PCI。

如果两个都使用,则它们都为32位的端口。

如果只使用PCI1,则可以将其配置为一个32位的端口或一个64位的端口。

本章的资料涉及32位和64位的端口,当PCI控制器作为32位端口操作时,不使用其中的某些信号。

注意,PCI1支持最多五个外部主设备,PCI2支持最多三个外部主设备。

PCI2未使用的请求信号在内部处于不活动状态,不影响仲裁器的操作。

PCI控制器通过PCI系统总线将处理器和存贮器系统与I/O组件连接起来。

该接口即作为发起者(主)设备,也作为目标(从)设备。

PCI控制器使用一条32位或64位复用的地址/数据总线,该总线可以按最高66MHz的频率运行。

接口提供地址和数据的奇偶校验,具有差错检测和报告功能。

该接口支持三个物理地址空间——64位地址的存贮器、32位地址的I/O和PCI配置空间。

注意,MPC8349E支持64位的地址/数据总线。

PCI1接口即可以作为PCI主机桥,称之为主机(hostmode)模式,也可以作为PCI总线上的外部设备,称之为代理模式(agentmode)。

更多信息参见13.4.4.4“主机模式配置访问”。

PCI2接口只支持主机模式。

注意,当PCI控制器处于代理模式时,可以从PCI总线配置PCI控制器。

提供了地址变换机制,在PCI总线和内部总线之间映射PCI存贮器窗口。

13.1.2特性

PCI控制器包括以下特性:

●遵循PCI规范Rev.2.3。

●64位和32位PCI接口支持

●PCI1支持主机和代理模式,PCI2只支持主机模式

●支持对所有PCI地址空间的访问

●支持64位双地址周期(DACDual-addresscycle)(仅在作为目标设备时)

●可从PCI访问内部配置寄存器

●片上仲裁,在PCI1上支持五个主设备,在PCI2上支持三个主设备

●仲裁器支持两级优先级的请求/准许信号对

●支持PCI到存贮器和存贮器到PCI流

●存贮器预取PCI读访问,支持延迟读事务

●支持处理器到PCI和PCI到存贮器写存储(writeposting)

●支持可选的接收事务监听

●用于主机和外设之间地址映射的地址变换单元

●支持奇偶校验

●PCI3.3V兼容

13.1.3操作模式

PCI控制器的操作模式在复位时由复位配置字高端(RCWH)确定,关于RCWH参见4.4.2节“复位配置字”。

表13-1汇总了这些模式。

表13-1PCI控制器模式

参数

说明

节/页

主机/代理配置

为PCI1接口选择主机模式或代理模式

4.4.2.11/4-33

PCI接口选择

选择一个64位的接口或两个32位的PCI接口

4.4.2.13

PCI仲裁器启用

启用片上PCI总线仲裁器

4.4.2.14

4.4.2.15

13.1.3.1主机/代理配置

PCI控制器即可以作为PCI主机桥(称之为主机模式),也可以作为PCI总线上的外部设备(称之为代理模式)。

注意,主机/代理模式选择在上电时确定,4.4.2.7节“PCI主机/主体配置”对此进行了总结。

当设备上电为主机模式时,所有进入的配置访问都被忽略(因此主设备中止)。

当设备上电为代理模式时,它应答进入的配置访问。

注意,在PCI代理模式中,在允许内向地址转换之前,PCI控制器忽略除内存映射寄存器之外的所有PCI存贮器访问。

注意,只有主PCI接口(PCI1)支持代理模式。

13.1.3.2单64位/双32位接口配置

可以把该接口配置为一个单64位的PCI接口或两个独立的32位的PCI接口。

关于PCI-64配置的引脚分配见表4-25。

PCI接口选择的初始值由RCWH[PCI64]中的值确定。

更多信息参见4.4.2.8节“64位PCI的配置”

13.1.3.3PCI仲裁器配置

可以把该接口配置为使用片上或片外PCI仲裁器。

PCI1的仲裁由RCWH[PCI1ARB]中的值确定,PCI2的仲裁由RCWH[PCI2ARB]中的值确定。

更多信息参见4.4.2.9节“PCI1仲裁器配置”。

13.2外部信号说明

表13-2列出了PCI信号的特性。

表13-2信号的特性

名称

功能

复位状态

上拉

CPCI1_HS_ENUM

CompactPCI1热交换计数器

高阻

需要

CPCI1_HS_ES

CompactPCI1热交换弹出开关

-

-

CPCI1_HS_LED

CompactPCI1热交换LED

有效

-

M66EN

66MHz允许

-

-

/PCI1_REQ64

PCI1请求64位传输

高阻1

需要

/PCI1_ACK64

PCI1应答64位传输

高阻

需要

PCI1_AD[63:

0]

PCI1地址/数据

高阻

-

PCI2_AD[31:

0]

PCI2地址/数据

高阻

-

PCI/n_C//BE[3:

0]

PCI总线命令/字节允许

高阻

-

PCI1_CBE[7:

0]

PCI1总线命令/字节允许

高阻

-

/PCIn_DEVSEL

PCIn设备选择

高阻

需要

/PCIn_FRAME

PCIn帧周期

高阻

需要

/PCI1_REQ[0:

4]

PCI1仲裁器请求

配置有关

输入时需要

/PCI2_REQ[0:

2]

PCI2仲裁器请求

配置有关

输入时需要

/PCI1_GNT[0:

4]

PCI1仲裁器准许

配置有关

-

/PCI1_GNT[0:

2]

PCI2仲裁器准许

配置有关

-

PCI1_IDSEL

PCI1初始化设备选择

-

-

/PCI1_INTA

PCI1中断A

高阻

需要

/PCIn_IRDY

PCIn发起者就绪

高阻

需要

PCIn_PAR

PCIn奇偶校验

高阻

-

PCI1_PAR64

PCI1奇偶校验高端DWORD

高阻

-

/PCIn_PERR

PCIn奇偶校验错

高阻

需要

/PCIn_RESET_OUT

PCIn复位输出

有效

-

/PCIn_SERR

PCIn系统错

高阻

需要

/PCIn_STOP

PCIn停止

高阻

需要

/PCIn_TRDY

PCIn目标设备就绪

高阻

需要

1注意,在PCI64位主机模式中,/PCI1_REQ64在/HESET无效后立即有效(低),并一直保持有效,直到/PCI1_RESET_OUT无效之后的一个PCI时钟周期为止。

图13-2列出了外部PCI信号。

图13-2PCI接口外部信号

表13-3包括外部PCI接口信号的详细说明。

表13-3PCI1和PCI2接口信号——详细信号说明

信号

I/O

说明

CPCI1_HS_ENUM

O

CompactPCI1热交换计数器。

作为紧凑型PCI系统中的计数请求,用于将热交换接口连接到主机。

该信号仅用于代理模式。

状态含义

有效——卡已插入并需要配置,或将拔出卡,需要从系统资源列表中删除。

无效——不需要动作。

时序

有效/无效——未规定时序。

CPCI1_HS_ES

I

CompactPCI1热交换弹出开关。

仅用于代理模式。

在紧凑型PCI系统中,该输入信号用于将热交换接口连接到弹出开关逻辑。

状态含义

有效——开关打开。

无效——开关关闭。

时序

有效/无效——未规定时序。

CPCI1_HS_LED

O

CompactPCI1热交换LED。

在紧凑型PCI系统中,用于将热交换接口连接到热交换LED。

该信号仅用于代理模式。

状态含义

有效——输出正驱动逻辑1,点亮热交换LED。

无效——输出正驱动逻辑0,关闭热交换LED。

时序

有效/无效——未规定时序。

M66EN

I

66MHz允许。

确定PCI接口的AC定时。

状态含义

当PCI1和PCI2的频率相同(OCCR[PCI1CR]=OCCR[PCI2CR])时:

有效——PCI1接口信号使用66MHz的PCIAC定时参数。

PCI2接口信号使用66MHz的PCIAC定时参数。

无效——PCI1接口信号使用33MHz的PCIAC定时参数。

PCI2接口信号使用33MHz的PCIAC定时参数。

当PCI1和PCI2的频率不相同(OCCR[PCI1CR]=0且OCCR[PCI2CR]=1或OCCR[PCI1CR]=1且OCCR[PCI2CR]=0)时:

有效——PCI1接口信号使用66MHz的PCIAC定时参数。

PCI2接口信号使用33MHz的PCIAC定时参数。

无效——PCI1接口信号使用33MHz的PCIAC定时参数。

PCI2接口信号使用66MHz的PCIAC定时参数。

时序

有效/无效——不变。

PCIn_AD[63:

0]

I/O

PCI地址/数据总线。

在地址周期内,这些信号包括一个物理地址。

在数据周期内,这些信号包括数据字节。

如果PCI_64为0,则不使用PCI_AD[63:

32]。

O

用于双向PCI地址/数据总线的输出。

状态含义

有效/无效——在PCI事务的地址周期内代表物理地址,在PCI事务的数据周期内,PCI地址/数据总线包含要写入的数据。

PCI_AD[7:

0]定义最低有效字节,PCIn_AD[63:

56]定义最高有效字节。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

I

用于双向PCI地址/数据总线的输入。

状态含义

有效/无效——在PCI事务的地址周期内代表要译码的地址,作为对设备选择的检查。

在PCI事务的数据周期内代表要接收的数据。

PCI_AD[7:

0]定义最低有效字节,PCIn_AD[63:

56]定义最高有效字节。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

PCI/n_C//BE[7:

0]

I/O

PCI总线命令/字节允许。

O

用于双向命令/字节允许的输出。

状态含义

有效/无效——在地址周期内,PCI_CBE[7:

0]定义总线命令。

字节允许为PCI总线在数据周期内确定哪些字节通道携带有意义的数据。

PCI_CBE[0]信号对应于最低有效字节。

如果PCI_64为0,则不使用PCI_CBE[7:

4]。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

I

用于双向命令/字节允许的输入。

状态含义

有效/无效——在地址周期内,PCI_CBE[7:

0]指示另一个主设备正在发送的命令。

在PCI总线数据周期内,PCI_CBE[7:

0]指示哪些字节通道有效。

如果PCI_64为0,则不使用PCI_CBE[7:

4]。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

/PCIn_DEVSEL

I/O

PCIn设备选择。

O

用于双向设备选择的输出。

状态含义

有效——PCIn控制器已经译码地址,是当前访问的目标。

无效——PCIn控制器已经译码地址,不是当前访问的目标。

定时

有效/无效——按PCI局部总线规范Rev2.3规定。

I

用于双向设备选择的输入。

状态含义

有效——某些PCI代理(不是本PCIn控制器)已经译码地址,是当前访问的目标。

无效——未选择PCI代理。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

/PCIn_FRAME

I/O

PCIn帧周期信号。

当前PCI主设备用它指示一次访问的开始及持续时间。

O

用于双向帧的输出。

状态含义

有效——PCIn控制器作为PCI主设备,正在启动一个总线事务。

当/PCI_FRAME有效时,数据传输才可以继续进行。

无效——如果/PCI_IRDY有效,则指示PCI事务正处于最后的数据周期;如果/PCI_IRDY无效,则指示PCI总线空闲。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

I

用于双向帧的输入。

状态含义

有效——另一个PCI主设备正在启动一个总线事务。

无效——事务正处于最后的数据周期或总线空闲。

定时

有效/无效——按PCI局部总线规范Rev2.3规定。

/PCIn_GNT0

I/O

PCIn仲裁器准许。

当仲裁器启用时,它为该PCIn控制器上的输出信号。

当仲裁器禁用时,它为输入信号。

注意:

/PCIn_GNT0是一个点到点的信号。

每个主设备都有其自己的准许信号。

O

用于双向仲裁器准许的输出。

状态含义

有效——PCIn控制器将PCI总线的控制权授予代理0。

无效——PCIn控制器未将PCI总线的控制权授予代理0。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

I

用于双向仲裁器准许的输入。

状态含义

有效——外部仲裁器准许PCIn控制器控制PCI总线。

无效——外部仲裁器未准许PCIn控制器控制PCI总线。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

/PCIn_GNT[1:

4]

O

PCIn仲裁器准许。

当仲裁器启用时,它为该PCIn控制器上的输出信号。

注意,/PCIn_GNTn是一个点到点的信号。

每个主设备都有其自己的准许信号。

状态含义

有效——PCIn控制器将PCI总线的控制权授予代理n。

无效——PCIn控制器未将PCI总线的控制权授予代理n。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

PCI1_IDSEL

I

PCI1初始化设备选择。

在代理模式中,用作PCI配置周期期间的片选。

在主机模式中,该信号应连到低。

状态含义

有效——PCI1控制器被选中进行参数配置的读写操作。

无效——PCI1控制器未被选中。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

/PCI1_INTA

O

PCI1中断A。

状态含义

有效——PCI1控制器向PCI主机通告中断。

无效——PCI1控制器当前未通告中断。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

/PCIn_IRDY

I/O

PCI发起者就绪。

当PCI控制器为PCI传输的发起者时,它就驱动该信号。

O

用于双向PCI发起者就绪的输出。

状态含义

有效——PCIn控制器作为PCI主设备,可以完成PCI传输的当前数据周期。

在写周期,PCIn控制器宣告/PCIn_IRDY有效指明数据已经载PCI1[63:

0]中。

在读期间,该PCIn控制器宣告/PCIn_IRDY有效,指示它准备好接收数据。

无效——在作为PCI主设备的该PCIn控制器可以完成当前数据周期之前,PCI目标设备需要等待。

在写期间,当无法向目标设备提供有效数据时,该PCIn控制器宣告/PCIn_IRDY无效,插入一个等待周期。

在读期间,当无法接受来自目标设备的数据时,该PCIn控制器宣告/PCIn_IRDY无效,插入一个等待周期。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

I

用于双向发起者就绪的输入。

状态含义

有效——另一个PCI主设备可以完成事务的当前数据周期。

无效——如果/PCIn_FRAME有效,则指示来自另一个主设备的一个等待周期。

如果/PCIn_FRAME无效,则指示PCI总线空闲。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

PCIn_PAR

I/O

PCIn奇偶校验。

O

用于双向奇偶校验的输出。

状态含义

有效——在地址和数据周期内,PCI_AD[31:

0]和PCI_CBE[3:

0]的奇校验。

无效——在地址和数据周期内,PCI_AD[31:

0]和PCI_CBE[3:

0]的偶校验。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

I

用于双向奇偶校验的输入。

状态含义

有效——在地址和数据周期内,奇校验由另一个PCI主设备或PCI目标设备驱动。

无效——在地址和数据周期内,偶校验由另一个PCI主设备或PCI目标设备驱动。

定时

有效/无效——按PCI局部总线规范Rev2.3规定。

PCI1_PAR64

I/O

高端DWORD奇偶校验。

保护数据的高32位和命令/字节允许的高4位的偶校验位。

O

用于双向高端DWORD奇偶校验的输出。

状态含义

有效——在地址和数据周期内,PCI_AD[63:

32]和PCI_C//BE[7:

4]信号的奇校验。

无效——在地址和数据周期内,对PCI_AD[63:

32]和PCI_C//BE[7:

4]信号的偶校验。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

I

用于双向高位DWORD奇偶校验的输入。

状态含义

有效——在读数据周期内,奇校验由另一个PCI主设备或PCI目标设备驱动。

无效——在读数据周期内,偶校验由另一个PCI主设备或PCI目标设备驱动。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

/PCIn_PERR

I/O

PCIn奇偶校验错。

O

用于双向奇偶校验错的输出。

状态含义

有效——作为PCI代理的PCIn控制器检测到一个数据奇偶校验错。

(在读时由PCI发起者驱动,在写时由PCI目标设备驱动。

)

无效——无错误。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

I

用于双向奇偶校验错的输入。

状态含义

有效——当该PCIn控制器提供数据时(在写期间该PCIn控制器作为PCI发起者,或在读期间作为PCI目标设备),另一个PCI代理检测到一个奇偶校验错。

无效——无错误。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

/PCIn_REQ0

I/O

PCIn总线请求。

当仲裁器启用时,为该PCIn控制器上的输入信号。

当仲裁器禁用时,为输出信号。

注意,/PCIn_REQ0是一个点到点的信号。

每个主设备都有其自己的请求信号。

O

用于双向总线请求的输出。

状态含义

有效——PCI控制器正在请求控制PCI总线,以执行一个事务。

无效——PCI控制器不要求使用PCI总线。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

I

用于双向总线请求的输入。

状态含义

有效——代理0正在请求控制PCI总线,以执行一个事务。

无效——代理0不要求使用PCI总线。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

/PCI2_REQ[1:

4]

I

PCIn总线请求。

当仲裁器启用时,为该PCIn控制器上的输入信号。

注意,/PCIn_REQ[n]是一个点到点的信号。

每个主设备都有其自己的请求信号。

下面是/PCIn_REQ[n]输入的状态含义。

状态含义

有效——代理n正在请求控制PCI总线,以执行一个事务。

无效——代理n不要求使用PCI总线。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

/PCI1_REQ64

I/O

64位事务请求。

指示当前主设备期望使用64位的传输来传输数据。

O

用于双向64位事务请求的输出。

状态含义

有效——PCI1作为PCI事务的主设备,期望使用所有64位。

无效——PCI1作为PCI事务的主设备,在服务数据传输时只使用32位的数据总线。

在PCI主机模式中,/PCI1_REQ64在/HRESET无效后立即有效(低),并一直保持有效,直到/PCI1_RESET_OUT无效之后的一个PCI时钟周期为止。

在PCI代理模式中,如果在/PORESET无效时采样的/PCI1_REQ64为高,将不再使用PCI总线的高阶位(PCI1_AD[63:

32]、PCI1_C//BE[7:

4]和PCI1_PAR64)。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

I

用于双向64位事务请求的输入。

状态含义

有效——PCI事务的主设备正在为事务的数据阶段请求使用完全64位的数据总线。

无效——PCI事务的主设备在事务的数据阶段期间只使用32位的数据总线。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

/PCI1_ACK64

I/O

PCI1应答64位传输。

指示当前目标设备在当前事务的数据阶段期间是否支持64位的传输。

如果/PCI1_64为0,则不使用该信号。

O

用于双向64位事务应答的输出。

状态含义

有效——PCI1作为PCI事务的目标设备,可以为事务的数据阶段使用完全64位传输。

无效——PCI1作为PCI事务的目标设备,在服务数据传输时只可以使用32位的数据总线。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

I

用于双向64位事务应答的输入。

状态含义

有效——PCI事务的目标设备可以为事务的数据阶段使用完全64位的数据总线。

无效——PCI事务的目标设备在事务的数据阶段期间只可以使用32位的数据总线。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

/PCIn_RESET_OUT

O

PCIn复位。

仅在主机模式中使用该信号。

在代理模式中,该信号应被断开。

状态含义

有效——PCI总线上的设备正处于复位状态。

无效——PCI总线上的设备正常操作。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

/PCIn_SERR

I/O

PCIn系统错误。

O

用于双向系统错误的输出。

状态含义

有效——检测到地址奇偶校验错、目标设备终止(当该PCIn控制器作为发起者时)、或其他系统错误(结果为灾难性错误)。

无效——无错误。

定时

有效/无效——按PCI局部总线规范Rev2.3规定。

I

用于双向系统错误的输入。

状态含义

有效——某个设备(非本PCIn控制器)已经检测到了一个灾难性错误。

无效——无错误。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

/PCIn_STOP

I/O

PCIn停止。

O

用于双向停止的输出。

状态含义

有效——作为PCI目标设备的PCIn控制器正在请求发起者停止当前事务。

无效——当前事务可以继续。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

I

用于双向停止的输入。

状态含义

有效——目标设备正在请求作为发起者的该PCI控制器停止当前事务。

无效——当前事务可以继续。

时序

有效/无效——按PCI局部总线规范Rev2.3规定。

/PCIn_TRDY

I/O

PCIn目标设备就绪。

O

用于双向目标设备就绪的输出。

状态含义

有效——作为PCI目标设备的PCIn控制器可以完成PCI事务的当前数据周期。

在读期间