乘法器.docx

《乘法器.docx》由会员分享,可在线阅读,更多相关《乘法器.docx(12页珍藏版)》请在冰豆网上搜索。

乘法器

乘法器

用时序电路实现有两种方法:

一种是被乘数累加法,将被乘数做乘数次的加法。

当乘数较大时,加法的次数较多;另一种方法是移位相加法。

做加法的次数少于等于乘数的位数,这是下面要介绍的。

1.算法:

设乘数和被乘数的位数≤r

(1)两个r位的数相乘,乘积为2r位。

(2)积=r个“部分积”只和。

(3)当乘数的第i位为0时,第i位的部分积为0。

当乘数的第i位为0时,第i位的部分积为乘数左移i–1次。

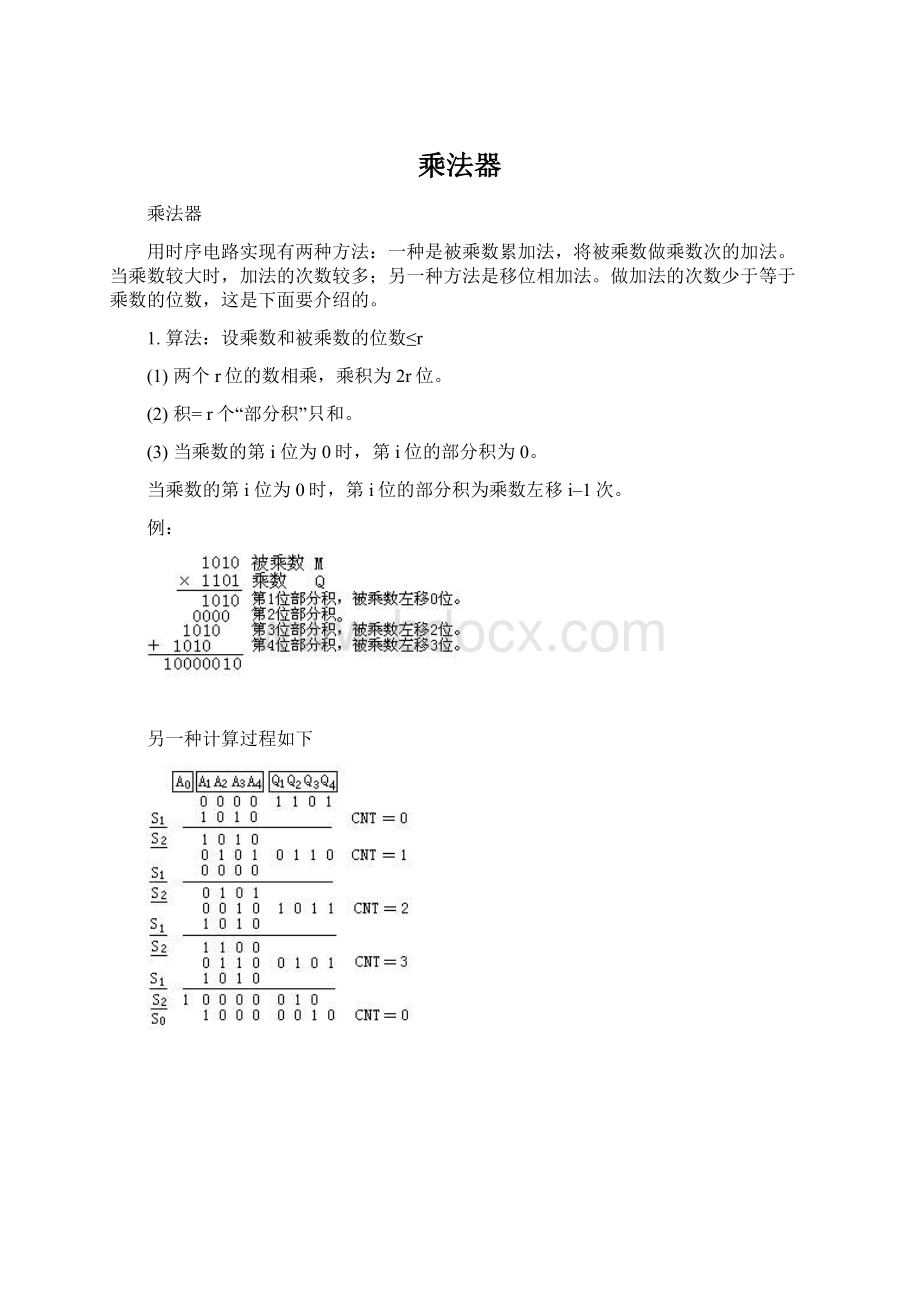

例:

另一种计算过程如下

2、处理器结构

根据算法可以得到乘法器的结构。

其中M是被乘数寄存器,Q是乘数寄存器、A是累加器,CNT是计数器。

在A0AQ中放部分积。

in1是乘数信号,in2是被乘数信号。

3、硬件描述语言

(1)系统描述

(2)寄存器M(mreg,具有并入功能)

当sl=0时保持;当sl=1时,在时钟触发时将输入信号存入,并送到加法器的一个入口。

(3)寄存器A、Q(areg、qreg具有并入功能、右移位功能、清零)

当m=00时保持、当m=01时右移、当m=10时清零、当m=11时并入。

图中e=q(0)

(4)计数器CNT(conut,有清零功能的模4计数器)

当cr=00时同步清零,当cr=01时同步计数,当cr=11时保持。

(5)1位寄存器A0(adreg,有清零功能)

当a=0时同步清零,当a=1时锁存。

(6)加法器(add)

(7)状态机(contr)

状态S0:

等待in1、in2信号就位,st为开始信号

当st=1时,sl=0、m1=00、m2=00、a=0、cr=00,done=0并保持在S0;

当st=0时,sl=1、m1=10、m2=11、a=0、cr=00,done=0进入S1状态。

状态S1:

当Q1=0时,sl=0、m1=00、m2=00、a=0、cr=11,done=0。

当Q1=1时,sl=0、m1=11、m2=00、a=1、cr=11,done=0。

在时钟触发后进入S2状态。

状态S2:

当q≠11时,sl=0、m1=01、m2=01、a=0、cr=01,done=0进入S1状态;

当q=11时,sl=0、m1=01、m2=01、a=0、cr=01,done=1进入S0状态。

其中done=0表示计算未完成,done=1表示计算已完成。

状态图如下和框图如下:

硬件描述语言如下:

顶层(系统结构)

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_Arith.ALL;

ENTITYmultiplierIS

PORT(

in1,in2:

INSTD_LOGIC_VECTOR(3DOWNTO0);

st,clk:

INSTD_LOGIC;

done:

OUTSTD_LOGIC;

product:

BUFFERSTD_LOGIC_VECTOR(7DOWNTO0));

ENDmultiplier;

ARCHITECTUREarc_multiplierOFmultiplierIS

SIGNALx1,y1,sum1,pp:

STD_LOGIC_VECTOR(3downto0);

SIGNALa1,b1,c1,d1,e1,s:

STD_LOGIC;

SIGNALm11,m21,cr1,qq1:

STD_LOGIC_VECTOR(1downto0);

COMPONENTmreg

PORT(

sl,clk:

INSTD_LOGIC;

in1:

INSTD_LOGIC_VECTOR(3downto0);

out1:

OUTSTD_LOGIC_VECTOR(3downto0));

ENDCOMPONENT;

COMPONENTqreg

PORT(

clk,dsr:

INSTD_LOGIC;

m:

INSTD_LOGIC_VECTOR(1DOWNTO0);

d:

INSTD_LOGIC_VECTOR(3DOWNTO0);

q:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

e:

OUTSTD_LOGIC);

ENDCOMPONENT;

COMPONENTcount

PORT(

clk:

INSTD_LOGIC;

cr:

INSTD_LOGIC_VECTOR(1DOWNTO0);

q:

OUTSTD_LOGIC_VECTOR(1DOWNTO0));

ENDCOMPONENT;

COMPONENTadreg

PORT(

clk,a,c:

INSTD_LOGIC;

b:

OUTSTD_LOGIC);

ENDCOMPONENT;

COMPONENTcontr

PORT(

clk,st,q1:

INSTD_LOGIC;

qq:

INSTD_LOGIC_VECTOR(1DOWNTO0);

sl,a,done:

OUTSTD_LOGIC;

m1,m2,cr:

OUTSTD_LOGIC_VECTOR(1DOWNTO0));

ENDCOMPONENT;

COMPONENTadd

PORT(

x,y:

INSTD_LOGIC_VECTOR(3downto0);

sum:

OUTSTD_LOGIC_VECTOR(3downto0);

cout:

OUTSTD_LOGIC);

ENDCOMPONENT;

BEGIN

u1:

mregportmap(s,clk,in1,x1);

u2:

qregportmap(clk,b1,m11,sum1,y1,d1);

u3:

qregportmap(clk,d1,m21,in2,pp,e1);

u4:

addportmap(x1,y1,sum1,c1);

u5:

countportmap(clk,cr1,qq1);

u6:

adregportmap(clk,a1,c1,b1);

u7:

contrportmap(clk,st,e1,qq1,s,a1,done,m11,m21,cr1);

product<=y1&pp;

ENDarc_multiplier;

寄存器mreg

LIBRARYIEEE;

USEIEEE.std_Logic_1164.ALL;

ENTITYmregIS

PORT(

sl,clk:

INSTD_LOGIC;

in1:

INSTD_LOGIC_VECTOR(3downto0);

out1:

OUTSTD_LOGIC_VECTOR(3downto0));

ENDmreg;

ARCHITECTUREarc_mregOFmregIS

BEGIN

PROCESS(clk)

BEGIN

IFclk'EVENTANDclk='1'THEN

IFsl='1'THEN

out1<=in1;

ENDIF;

ENDIF;

ENDPROCESS;

ENDarc_mreg;

寄存器qreg

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYqregIS

PORT(

clk,dsr:

INSTD_LOGIC;

m:

INSTD_LOGIC_VECTOR(1DOWNTO0);

d:

INSTD_LOGIC_VECTOR(3DOWNTO0);

q:

BUFFERSTD_LOGIC_VECTOR(3DOWNTO0);

e:

OUTSTD_LOGIC);

ENDqreg;

ARCHITECTUREarc_qregOFqregIS

SIGNALq_temp:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

PROCESS(clk)

BEGIN

IFclk'EVENTANDclk='1'THEN

CASEmIS

WHEN"00"=>q_temp<=q;

WHEN"01"=>q_temp<=dsr&q(3DOWNTO1);

WHEN"10"=>q_temp<="0000";

WHEN"11"=>q_temp<=d;

WHENothers=>NULL;

ENDCASE;

ENDIF;

ENDPROCESS;

q<=q_temp;

e<=q_temp(0);

ENDarc_qreg;

计数器conut

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYcountIS

PORT(

clk:

INSTD_LOGIC;

cr:

INSTD_LOGIC_VECTOR(1DOWNTO0);

q:

OUTSTD_LOGIC_VECTOR(1DOWNTO0));

ENDcount;

ARCHITECTUREarc_countOFcountIS

SIGNALcnt:

STD_LOGIC_VECTOR(1DOWNTO0);

BEGIN

PROCESS(clk)

BEGIN

IF(clk'EVENTANDclk='1')THEN

IFcr="00"THEN

cnt<="00";

ELSIFcr="01"THEN

CASEcntIS

WHEN"00"=>cnt<="01";

WHEN"01"=>cnt<="10";

WHEN"10"=>cnt<="11";

WHEN"11"=>cnt<="00";

WHENothers=>NULL;

ENDCASE;

ENDIF;

ENDIF;

q<=cnt;

ENDPROCESS;

ENDarc_count;

1位寄存器adreg

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYadregIS

PORT(

clk,a,c:

INSTD_LOGIC;

b:

outSTD_LOGIC);

ENDadreg;

ARCHITECTUREarc_adregOFadregIS

BEGIN

PROCESS(clk)

BEGIN

IFclk'EVENTANDclk='1'THEN

IFa='0'THEN

b<='0';

ELSE

b<=c;

ENDIF;

ENDIF;

ENDPROCESS;

ENDarc_adreg;

加法器add

LIBRARYIEEE;

USEIEEE.Std_Logic_1164.all;

ENTITYaddIS

PORT(

x,y:

INSTD_LOGIC_VECTOR(3downto0);

sum:

OUTSTD_LOGIC_VECTOR(3downto0);

cout:

OUTSTD_LOGIC);

ENDadd;

ARCHITECTUREarc_addOFaddIS

SIGNALg,p,c:

STD_LOGIC_VECTOR(3downto0);

BEGIN

p(0)<=x(0)XORy(0);

p

(1)<=x

(1)XORy

(1);

p

(2)<=x

(2)XORy

(2);

p(3)<=x(3)XORy(3);

g(0)<=x(0)ANDy(0);

g

(1)<=x

(1)ANDy

(1);

g

(2)<=x

(2)ANDy

(2);

g(3)<=x(3)ANDy(3);

c(0)<=g(0);

c

(1)<=g

(1)OR(p

(1)ANDg(0));

c

(2)<=g

(2)OR(p

(2)ANDg

(1))OR(p

(2)ANDp

(1)ANDg(0));

c(3)<=g(3)OR(p(3)ANDg

(2))OR(p(3)ANDp

(2)ANDg

(1))OR(p(3)ANDp

(2)ANDp

(1)ANDp(0));

cout<=c(3);

sum(0)<=x(0)XORy(0);

sum

(1)<=x

(1)XORy

(1)XORc(0);

sum

(2)<=x

(2)XORy

(2)XORc

(1);

sum(3)<=x(3)XORy(3)XORc

(2);

ENDarc_add;

状态机contr

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYcontrIS

PORT(

clk,st,q1:

INSTD_LOGIC;

qq:

INSTD_LOGIC_VECTOR(1DOWNTO0);

sl,a,done:

OUTSTD_LOGIC;

m1,m2,cr:

OUTSTD_LOGIC_VECTOR(1DOWNTO0));

ENDcontr;

ARCHITECTUREarc_contrOFcontrIS

SUBTYPEstate_typeISSTD_LOGIC_VECTOR(1DOWNTO0);

SIGNALsta:

state_type:

="00";

CONSTANTS0:

state_type:

="00";

CONSTANTS1:

state_type:

="01";

CONSTANTS2:

state_type:

="10";

BEGIN

con:

PROCESS(st,q1,qq)

BEGIN

CASEstaIS

WHENS0=>

IFst='1'THEN

sl<='0';m1<="00";m2<="00";a<='0';cr<="00";done<='0';

ELSE

sl<='1';m1<="10";m2<="11";a<='0';cr<="00";done<='0';

ENDIF;

WHENS1=>

IFq1='0'THEN

sl<='0';m1<="00";m2<="00";a<='0';cr<="11";done<='0';

ELSE

sl<='0';m1<="11";m2<="00";a<='1';cr<="11";done<='0';

ENDIF;

WHENS2=>

IFqq="11"THEN

sl<='0';m1<="01";m2<="01";a<='0';cr<="00";done<='1';

ELSE

sl<='0';m1<="01";m2<="01";a<='0';cr<="01";done<='0';

ENDIF;

WHENothers=>NULL;

ENDCASE;

ENDPROCESScon;

clo:

PROCESS(clk)

BEGIN

IFclk'EVENTANDclk='1'THEN

CASEstaIS

WHENS0=>

IFst='1'THEN

sta<=S0;

ELSE

sta<=S1;

ENDIF;

WHENS1=>sta<=S2;

WHENS2=>

IFqq="11"THEN

sta<=S0;

ELSE

sta<=S1;

ENDIF;

WHENothers=>NULL;

ENDCASE;

ENDIF;

ENDPROCESSclo;

ENDarc_contr;