EDA程序改错题.docx

《EDA程序改错题.docx》由会员分享,可在线阅读,更多相关《EDA程序改错题.docx(11页珍藏版)》请在冰豆网上搜索。

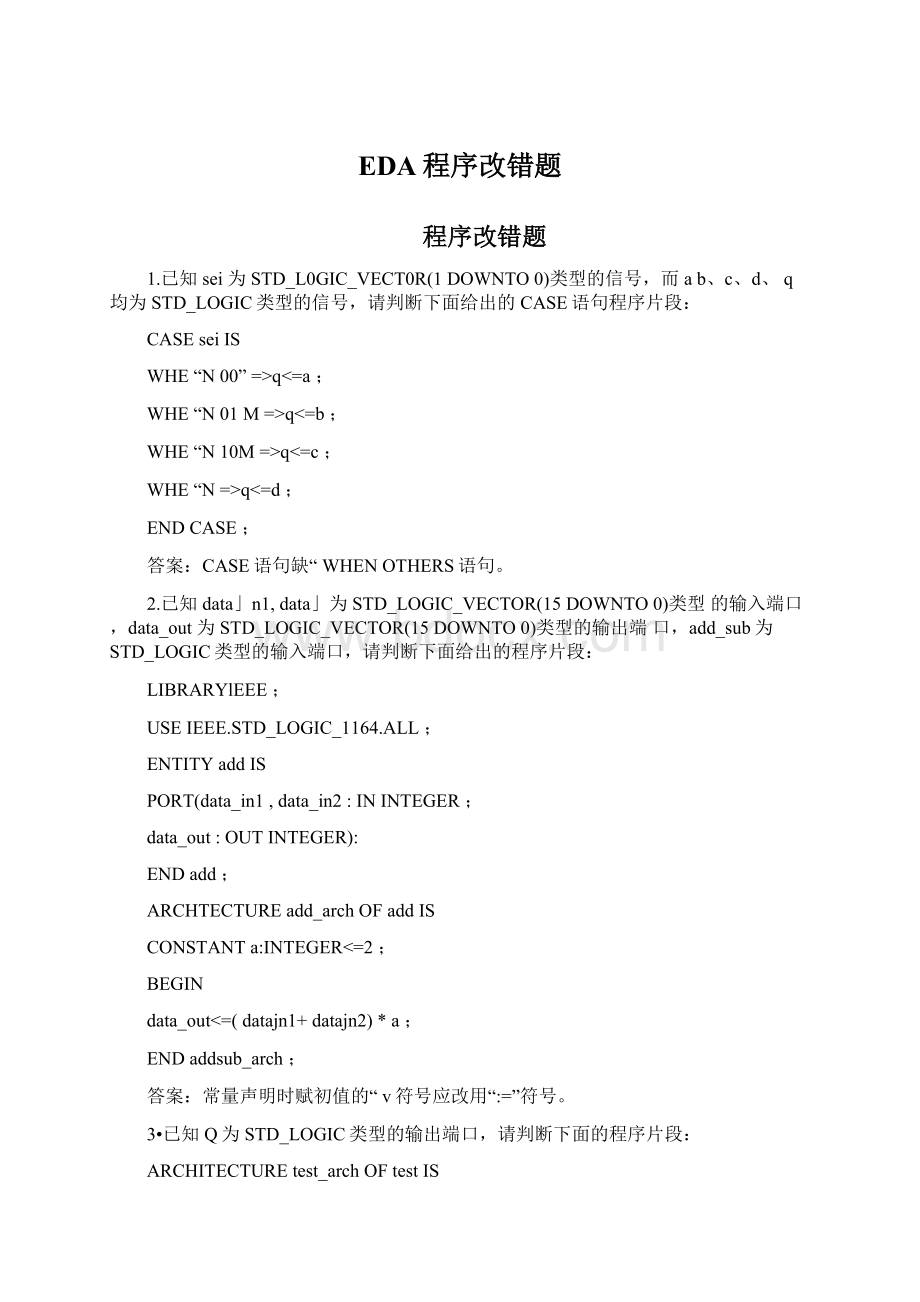

EDA程序改错题

程序改错题

1.已知sei为STD_L0GIC_VECT0R(1DOWNTO0)类型的信号,而ab、c、d、q均为STD_LOGIC类型的信号,请判断下面给出的CASE语句程序片段:

CASEseiIS

WHE“N00”=>q<=a;

WHE“N01M=>q<=b;

WHE“N10M=>q<=c;

WHE“N=>q<=d;

ENDCASE;

答案:

CASE语句缺“WHENOTHERS语句。

2.已知data」n1,data」为STD_LOGIC_VECTOR(15DOWNTO0)类型的输入端口,data_out为STD_LOGIC_VECTOR(15DOWNTO0)类型的输出端口,add_sub为STD_LOGIC类型的输入端口,请判断下面给出的程序片段:

LIBRARYlEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYaddIS

PORT(data_in1,data_in2:

ININTEGER;

data_out:

OUTINTEGER):

ENDadd;

ARCHTECTUREadd_archOFaddIS

CONSTANTa:

INTEGER<=2;

BEGIN

data_out<=(datajn1+datajn2)*a;

ENDaddsub_arch;

答案:

常量声明时赋初值的“v符号应改用“:

=”符号。

3•已知Q为STD_LOGIC类型的输出端口,请判断下面的程序片段:

ARCHITECTUREtest_archOFtestIS

BEGIN

SIGNALB:

STD_LOGIC;

Q<=B;

ENDtest_arch

答案:

信号SIGNAL的声明语句应该放在BEGIN语句之前。

4•已知A和Q均为BIT类型的信号,请判断下面的程序片段:

ARCHITECTUREarchtestOFtestIS

BEGIN

CASEAIS

WHEN<0,=>Q<=4;T

WHENT=>Qv=4:

0*

ENDCASE;

ENDarchtest;

答案:

CASE语句应该存在于进程PROCESS内。

三.判断改错题(3分X6题)(评分标准:

给出正确答案1分/题;答案基本正确0.5分/

题。

)

1・已知A和Q均为BIT类型的信号,请判断下面的程序片断:

ARCHITECTUREtestOFtestIS

BEGIN

CASEAIS

WHENV=>Q<=,1,:

WHENT=>Qv=O;

ENDCASE;

ENDtest;

【参考答案】:

CASE语句应该存在于进程PROCESS内。

2•已知start为STD_LOGIC类型的信号,sum是INTEGER类型的信号,请判断下面的程序片断:

PROCESS(start)

BEGIN

FORiIN1TO9LOOP

sum:

=sum+i;

ENDLOOP;

ENDPROCES;S

【参考答案】:

sum是信号,其赋值符号应该由改为“v=”。

3・已知Q为STD_LOGIC类型的输出端口,请判断下面的程序片断:

ARCHITECTUREtestOF

testIS

BEGIN

SIGNALB:

STD_LOGIC:

ENDtest;

【参考答案】:

信号SIGNAL的申明语句应该放在BEGIN语句之前。

4-已知A和B均为STD_LOGIC类型的信号‘请判断下面的语句:

【参考答案】:

不定态符号应该由小写的’X,改为大写的’X,。

5.已知A为INTEGER类型的信号,B为STD_LOGIC类型的信号,请判断下面的程

序片断:

ARCHITECTUREtestOFtestIS

BEGIN

B<=A;

ENDtest;

【参考答案】:

A和B的数据类型不一致,不能相互赋值。

6・已知sei是STD_L0GIC_VECT0R(1DOWNTO型信号,而a、b、c、d、q

均为

Gl

型信号

请判断下面给出的CAS语句

CASEseiIS

WHEN“00

=>

<=a

q

?

■

WHEN“01

=>

<=b

q

?

■

WHEN“1

=>

v—r

?

■

n”

、一wq

WHEN“11

=>

<=d

q

?

■

END

CASE;

乡专合条】-

CASE语句

“WHENOTHER语句。

四、判断下面程序中是否有错误,若有错误请改正;

1、SIGNALA,EN:

STD_LOGIC;PROCESS(A,EN)

VARIABLEB:

STD_LOGIC;

BEGIN

IFEN=411THEN

B<=A;

END;

ENDPROCESS;

2、RCHITECTUREONEOFSAMPLEISVARIABLEA,B,C:

INTEGER;BEGIN

Cv=A+B;

END;

五、判断下列程序是否有错误,如有则指出错误所在(10分)程序:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYzyt12IS

PORT(R,EN,CP:

INbit;

Q:

BUFFERSTD_LOGIC_VECTOR(0D0WNT03);

CO:

OUTSTD_LOGIC);

ENDzyt;

ARCHITECTUREc10OFzyt12

BEGIN

C0<=*1*WHEN(EN=*1*ANDQ="1011H)ELSE;

O;

PROCESS(R,CP)

BEGIN

IFR=TTHEN

Qv=”0000”;

ELSIF(CP'EVENTANDCPv=T)THEN

IFEN=VTHEN

Q<=Q;

ELSIFQ=H1011"THEN

Q<='00001;

ELSE

Q:

=Q+1;

ENDIF;

ENDPROCESS;

ENDone;

仔细阅读下列程序,回答问题

LIBRARYIEEE;-1

USEIEEE.STD_LOGIC_1164.ALL;-2

ENTITYLED7SEGIS-3

PORT(A:

INSTD_LOGIC_VECTOR(3DOWNTO0);一4

CLK:

INSTD_LOGIC;-5

LED7S:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));-6

ENDLED7SEG;-7

ARCHITECTUREoneOFLED7SEGIS一8

SIGNALTMP:

STD_LOGIC;一9

BEGIN一10

SYNC:

PROCESS(CLK,A)-11

BEGIN12

IFCLKEVENTANDCLK=TTHEN-13

TMP<=A;-14

ENDIF;-15

ENDPROCESS;-16

OUTLED:

PROCESS(TMP)-17

BEGIN18

CASETMPIS-19

WHEN“0000”=>LED7S<=H0111111"';-20

WHENH0001H=>LED7S<=H0000110M;-21

WHENH0010H=>LED7S<=H1011011H;-22

WHENH0011H=>LED7S<=H1001111H;-23

WHEN”01OCT=>LED7S<=K1100110";-24

WHEN”0101M=>LED7S<="1101101”;-25

WHEN”0110"=>LED7S<="1111101”;-26

WHEN”011T=>LED7S<=”0000111”;-27

WHEN"1000"=>LED7S<="1111111”;-28

WHENM1001n=>LED7S<='*1101111”;-29

ENDCASE;-30

ENDPROCESS;-31

ENDone;-32

1•在程序中存在两处错误,试指出,并说明理由:

第14行TMP附值错误第29与30行之间,缺少WHENOTHERS语句

2修改相应行的程序:

错误1行号:

9程序改为:

TMP:

STD_LOGIC_VECTOR(3DOWNTO0);

错误2行号:

29程序改为:

该语句后添加WHENOTHERS=>LED7S<="0000000

1、LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCNT4BIS

PORT(CLK,RST,ENA:

INSTD_LOGIC;

OUTY:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

COUT:

OUTSTD_LOGIC);

ENDCNT4B;

ARCHITECTUREbehavOFCNT4BIS

SIGNALCQI:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

PROCESS(CLK,RST,ENA)

BEGIN

IFRST=TTHENCQI<=0000:

ELSIFCLK'EVENTANDCLK=TTHEN

IFENA=n1”THENCQI<=CQI+1;

ENDIF;

ELSECQIv=”0000”;

ENDIF;

OUTYv=CQI;

ENDPROCESS;

COUTV=CQI(0)ANDCQI

(1)ANDCQI⑵ANDCQI(3);

ENDbehav;

2、LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCLK_6DIS

PORT(CLK,RST:

INSTD_LOGIC;

CLK_OUT:

OUTSTD_LOGIC);

ENDCLK_6D;

ARCHITECTUREONEOFCLK6DIS

VARIABLETEMP:

STD_LOGI(SIGNAL

BEGIN

PROCESS(CLK)

VARIABLECNT6D:

INTEGERRANGE0TO3;

CONSTANTSIGN:

INTEGERS;

BEGIN

IF(RST=“)THENTEMP<=©*1*,O

ELSIFCLKEVENTANDCLK-1,THEN(CLKEVENTANDCLK=T)

IF(CNT6D=SIGN)THEN

CNT6D:

=0;

TEMP<=NOTTEMP;

ELSECNT6D:

=CNT6D+1;

ENDIF;

ENDIF;

ENDPROCESS;

CLK_OUT<=TEMP;

ENDONE;

3、libraryieee;

useieee.std_logic_1164.all;

entityencoderis

port(b;_instd」ogic(7downto0);b:

instd」ogic_vector(7downto0)

y_outstd」ogic(2downto0));y:

outstd」ogic_vector(2downto0)

endencoder;

architectureoneofencoderis

begin

process(b)whenothers=>null;

endcase;

endprocess;

endone;

4、LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYcounterIS

PORT(reset:

INSTD_LOGIC;

clock:

INSTD_LOGIC;

num:

bufferintegerrange0to3;多一个“;n

);

END;

ARCHITECTUREbehavOFjishuISjishu改为COunter

Begin

Process(reset,clock)

Begin

Ifreset二⑴then

num<=0;

Elsifrising_edge(clock)then

Ifnum=3then

nuinv=0;

else

少endif;

numv二num+1;

endif;

endprocess;

end;

5、LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STDLOGICUNSIGNED:

STD_LOGIC_UNSIGNED.ALL

ENTITYLX32IS

PORT(CLK,CLR,OE:

INBIT;

D:

INSTD_LOGIC_VECTOR(7DOWNTO0);

Q:

OUTSTD_L0GIC_VECT0R(7DOWNTO0));

ENDLX3_2;

ARCHITECTUREstrucOFLX3_2IS

VARIABLEQ_TEMP:

STD_LOGIC_VECTOR(7DOWNTO0);SIGNAL

BEGIN

PROCESS(CLR)PROCESS(CLK)

BEGIN

IFCLR=OTHENQTEMPv-000000001;”00000000”

ELSIFCLK=TTHEN

Q_TEMP<=D;

ELSEQ_TEMPv=Q_TEMP;

ENDIF;

ENDPROCESS;

Q<=Q_TEMPWHENOE=TELSE

ENDstruc;

6・LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STDLOGICUNSIGNED;USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYLX3_2IS

PORT(A:

INSTD_L0GIC_VECT0R(3DOWNTO0);

STDLOGICVECTOR

LX32

B:

INSTD_LOGIC(3DOWNTO0);

GT丄T,EQ:

OUTSTD_LOGIC);

ENDLX3_2;

ARCHITECTUREoneOFLX82IS

BEGIN

PROCESS(A,B)

BEGIN

GTv=O;

LTv=O;

EQ<=0,;

IFA>BTHENGTv兰0”;O

ELSIFAELSEEQv=0”;O

ENDIF;

ENDPROCESS;

ENDone;

1、在程序中存在两处错误,试指出,并说明理由:

错误1原因:

case顺序语句必须放在进程语句Process内程序改为:

process(A)

beg

■

lncaseAis

错误2原因:

还有存在其他组合的可能

程序改为:

wlwhenothers=>nuII;

附:

自动化123江西理工大学王显聪