EDA应用技术教学大纲.docx

《EDA应用技术教学大纲.docx》由会员分享,可在线阅读,更多相关《EDA应用技术教学大纲.docx(11页珍藏版)》请在冰豆网上搜索。

EDA应用技术教学大纲

《EDA应用技术》教学大纲

一、课程概述

《EDA应用技术》是通信工程专业的一门专业课程,概述了EDA工程的理论基础、知识体系,阐述了EDA工具的开发、EDA工具应用于PCB设计、FPGA设计、ASIC设计、SOC设计的方法。

先修课程是数字电子技术、电路分析

二、课程目标

1.了解EDA工程的基本概念和理论基础。

2.初步熟悉和掌握EDA工程方法,涉及行为描述、SOC设计方法、IP复用、ASIC设计方法、虚拟机、测试平台设计方法、软硬件协同验证等。

3.掌握VHDL语法基础,以及程序设计方法。

4.了解电子产品设计开发过程以及专业EDA开发软件的应用。

5.EDA工程是一门实践性很强的课程,实验是一个很重要的教学环节,应特别重视培养提高实践动手能力。

三、课程内容和教学要求

这门学科的知识及技能要求分为知道、理解、掌握、学会四个层次。

这四个层次的一般涵义表述如下:

知道——是指对这门学科的基本知识、基本理论的认知。

理解——是指运用已了解的基本原理说明、解释一些现象、进行简单的电路设计。

掌握——是指利用掌握的理论知识对一些较复杂的电子产品进行设计开发。

学会——是指在具体设计中能灵活运用所学知识。

教学内容和要求表中的“√”号表示教学知识和技能的教学要求层次。

本标准中打“*”号的内容可作为自学,教师可根据实际情况确定要求或不布置要求。

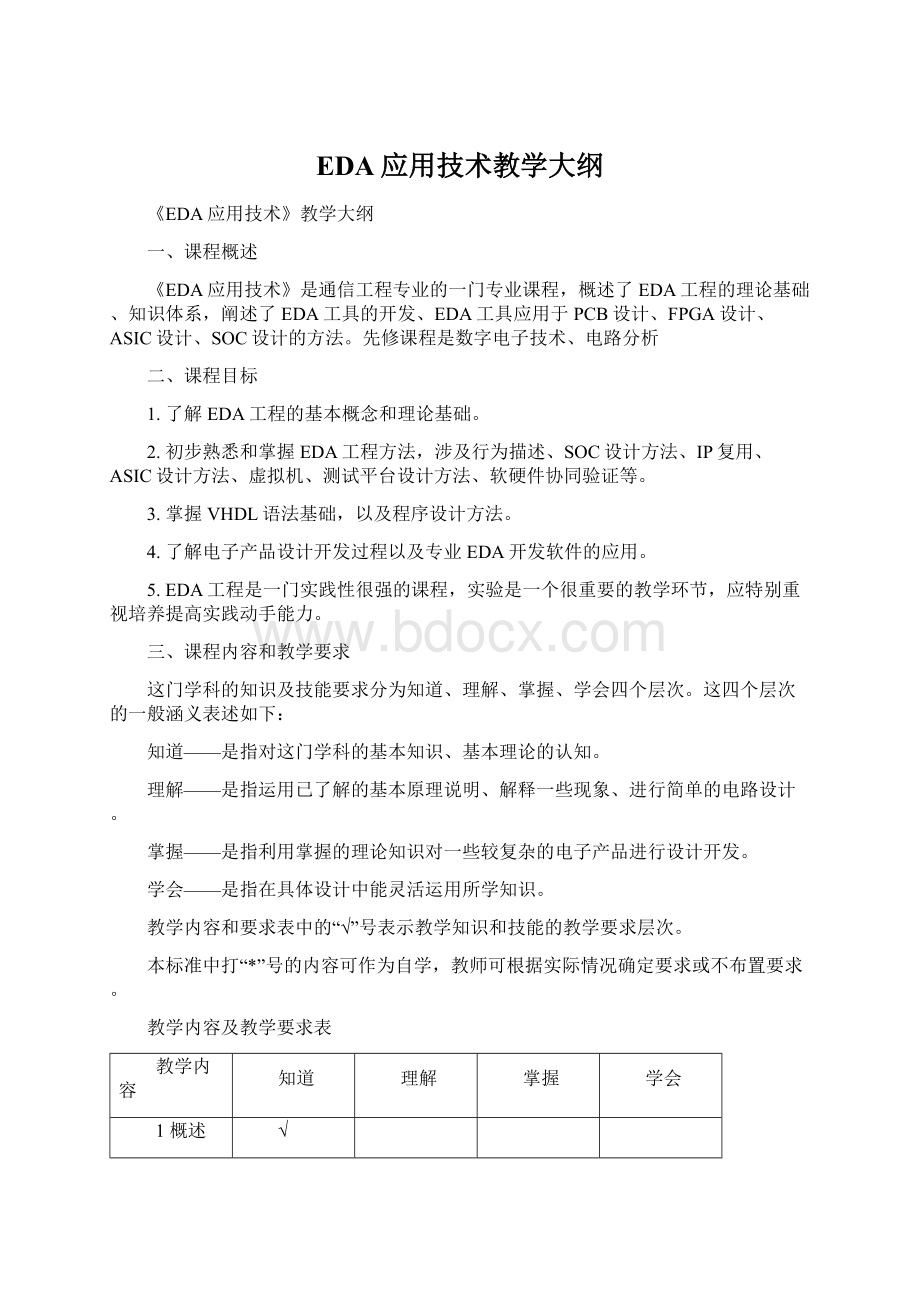

教学内容及教学要求表

教学内容

知道

理解

掌握

学会

1概述

1.1EDA技术及其发展

1.2EDA技术实现目标

1.3硬件描述语言VHDL

1.4VHDL综合

1.5基于VHDL的自顶向下设计方法

1.6EDA及传统电子设计方法的比较

1.7EDA的发展趋势

√

√

√

√

√

√

√

2 EDA设计流程及工具

2.1设计流程

2.2 ASIC及其设计流程

2.3常用EDA工具

2.4QuartusII简介

2.5IP核简介

√

√

√

√

3 FPGA/CPLD结构及应用

3.1概述

3.2简单PLD原理

3.3CPLD结构及工作原理

3.4FPGA结构及工作原理

3.5硬件测试技术

3.6FPGA/CPLD产品概述

3.7编程及配置

√

√

√

√

√

√

√

4 VHDL设计初步

4.1多路选择器的VHDL描述

4.2寄存器描述及其VHDL语言现象

4.4计数器设计

4.5一般加法计数器设计

√

√

√

√

5 QuartusII应用向导

5.1基本设计流程

5.2引脚设置和下载

5.3嵌入式逻辑分析仪使用方法

5.4原理图输入设计方法

√

√

√

√

6 VHDL设计进阶

6.1数据对象

6.2双向和三态电路信号赋值例解

6.3IF语句概述

6.4进程语句归纳

6.5并行语句例解

6.6仿真延时

√

√

√

√

√

√

7 宏功能模块及IP使用

7.1宏功能模块概述

7.2宏模块应用实例

7.3在系统存储器数据读写编辑器应用

7.4编辑SignalTapII的触发信号

7.5其他存储器模块的定制及应用

7.6流水线乘法累加器的混合输入设计

7.7LPM嵌入式锁相环调用

7.8IP核NCO数控振荡器使用方法

7.98051单片机IP软核应用

√

√

√

√

√

√

√

√

√

8 有限状态机设计

8.1一般有限状态机的设计

8.2Moore型有限状态机的设计

8.3Mealy型有限状态机的设计

8.4状态编码

8.5非法状态处理

√

√

√

√

√

9VHDL结构要素

9.1实体

9.2结构体

9.3子程序

9.4VHDL库

9.5VHDL程序包

9.6配置

9.7VHDL文字规则

9.8数据类型

9.9操作符

√

√

√

√

√

√

√

√

10VHDL基本语句

10.1顺序语句

10.2VHDL并行语句

10.3属性描述及定义语句

√

√

√

11设计优化和设计方法

11.1资源优化

11.2速度优化

11.3优化设置及时序分析

11.4ChipEditor应用

√

√

√

√

四、课程实施

(一)课时安排及教学建议

一般情况下,包括实验共安排54学时,其中讲授42学时,实验12学时。

分一学期完成。

具体课时安排如下:

课时安排如下:

教学内容

课时建议

教及学的方法建议

54课时

1概述

1.1EDA技术及其发展

1.2EDA技术实现目标

1.3硬件描述语言VHDL

1.4VHDL综合

1.5基于VHDL的自顶向下设计方法

1.6EDA及传统电子设计方法的比较

1.7EDA的发展趋势

2学时

讲述

2 EDA设计流程及工具

2.1设计流程

2.2 ASIC及其设计流程

2.3常用EDA工具

2.4QuartusII简介

2.5IP核简介

2学时

讲述

3 FPGA/CPLD结构及应用

3.1概述

3.2简单PLD原理

3.3CPLD结构及工作原理

3.4FPGA结构及工作原理

3.5硬件测试技术

3.6FPGA/CPLD产品概述

3.7编程及配置

4学时

讲述

4 VHDL设计初步

4.1多路选择器的VHDL描述

4.2寄存器描述及其VHDL语言现象

4.4计数器设计

4.5一般加法计数器设计

4学时

讲述、演示、实验

5 QuartusII应用向导

5.1基本设计流程

5.2引脚设置和下载

5.3嵌入式逻辑分析仪使用方法

5.4原理图输入设计方法

2学时

讲述、演示、实验

6 VHDL设计进阶

6.1数据对象

6.2双向和三态电路信号赋值例解

6.3IF语句概述

6.4进程语句归纳

6.5并行语句例解

6.6仿真延时

4学时

讲述

7 宏功能模块及IP使用

7.1宏功能模块概述

7.2宏模块应用实例

7.3在系统存储器数据读写编辑器应用

7.4编辑SignalTapII的触发信号

7.5其他存储器模块的定制及应用

7.6流水线乘法累加器的混合输入设计

7.7LPM嵌入式锁相环调用

7.8IP核NCO数控振荡器使用方法

7.98051单片机IP软核应用

6学时

讲述、演示、实验

8 有限状态机设计

8.1一般有限状态机的设计

8.2Moore型有限状态机的设计

8.3Mealy型有限状态机的设计

8.4状态编码

8.5非法状态处理

6学时

讲述、演示、实验

9VHDL结构要素

9.1实体

9.2结构体

9.3子程序

9.4VHDL库

9.5VHDL程序包

9.6配置

9.7VHDL文字规则

9.8数据类型

9.9操作符

4学时

讲述、演示、实验

10VHDL基本语句

10.1顺序语句

10.2VHDL并行语句

10.3属性描述及定义语句

4学时

11设计优化和设计方法

11.1资源优化

11.2速度优化

11.3优化设置及时序分析

11.4ChipEditor应用

4学时

讲述、演示、实验

合计:

54课时中含理论课42课时,实验`12课时;

(二)教学组织形式及教学方法要求

1.主要的教学组织形式是班级授课。

有时也可以采用分组教学。

或者几种组织方式灵活组合,尽量减轻学生的生理和心理疲劳。

2.注意教学方法的灵活性,组织学生讨论、指导阅读等。

培养学生发现问题、分析问题、解决问题的能力和探究意识。

3.注意组织学生参及课外小制作,培养学生的实际操作的兴趣和动手能力。

4.可以在多媒体课室上课。

借助声像呈示,提供给学生一个动态的、声情并茂的学习环境,让学生充分调动自己的视觉、听觉等感官,由多途径获得多方面的信息。

五、教材选用

《EDA技术应用》教材要在课程标准的统一要求下,实行多样化。

可以选用公认的水平较高的教材如教育部推荐教材,九五规划教材和面向21世纪教材。

如:

1、潘松,黄继业,EDA技术实用教程,科学出版社

2、潘松,王国栋,VHDL实用教程,电子科技大学出版社

六、课程评价

1.这门学科的评价依据是本课程标准规定的课程目标、教学内容和要求,该门课程采用实验(10%)、平时考核(30%)和集中考试(60%)相结合的形式进行。

2.集中考试说明

1)考试时间:

120分钟。

2)考试方式、分制及分数解释

采用闭卷、笔试的方式,以百分制评分,60分为及格,满分为100分。

3)题型比例

填空题15%;改错题20%;综合编程题65%。

4)样题及目标定位示例

A.填空题:

(着重考查学生对知识的理解程度)

例:

进程必须由()信号来启动。

B.改错题(着重考查学生对知识的理解、掌握程度)

例:

二输入及门电路的设计

LIBRARYIEEE;

USEIEEE.STD_LOGIC.1164.ALL;

ENTITYAND21IS;

PORT(A,B:

INSTD_LOGIC;

Y:

STD_LOGIC);

ENDAND21;

ARCHITECTUREONEOFAND21IS

Y:

=AANDB;

ENDONE;

C.综合编程(着重考查学生对知识的掌握和学会程度)

例:

设计一个四位十进制同步加法计数器,要求有异步复位功能

制定该课程标准小组成员:

审核者: