完整word版洗衣机控制器课程设计word文档良心出品.docx

《完整word版洗衣机控制器课程设计word文档良心出品.docx》由会员分享,可在线阅读,更多相关《完整word版洗衣机控制器课程设计word文档良心出品.docx(19页珍藏版)》请在冰豆网上搜索。

完整word版洗衣机控制器课程设计word文档良心出品

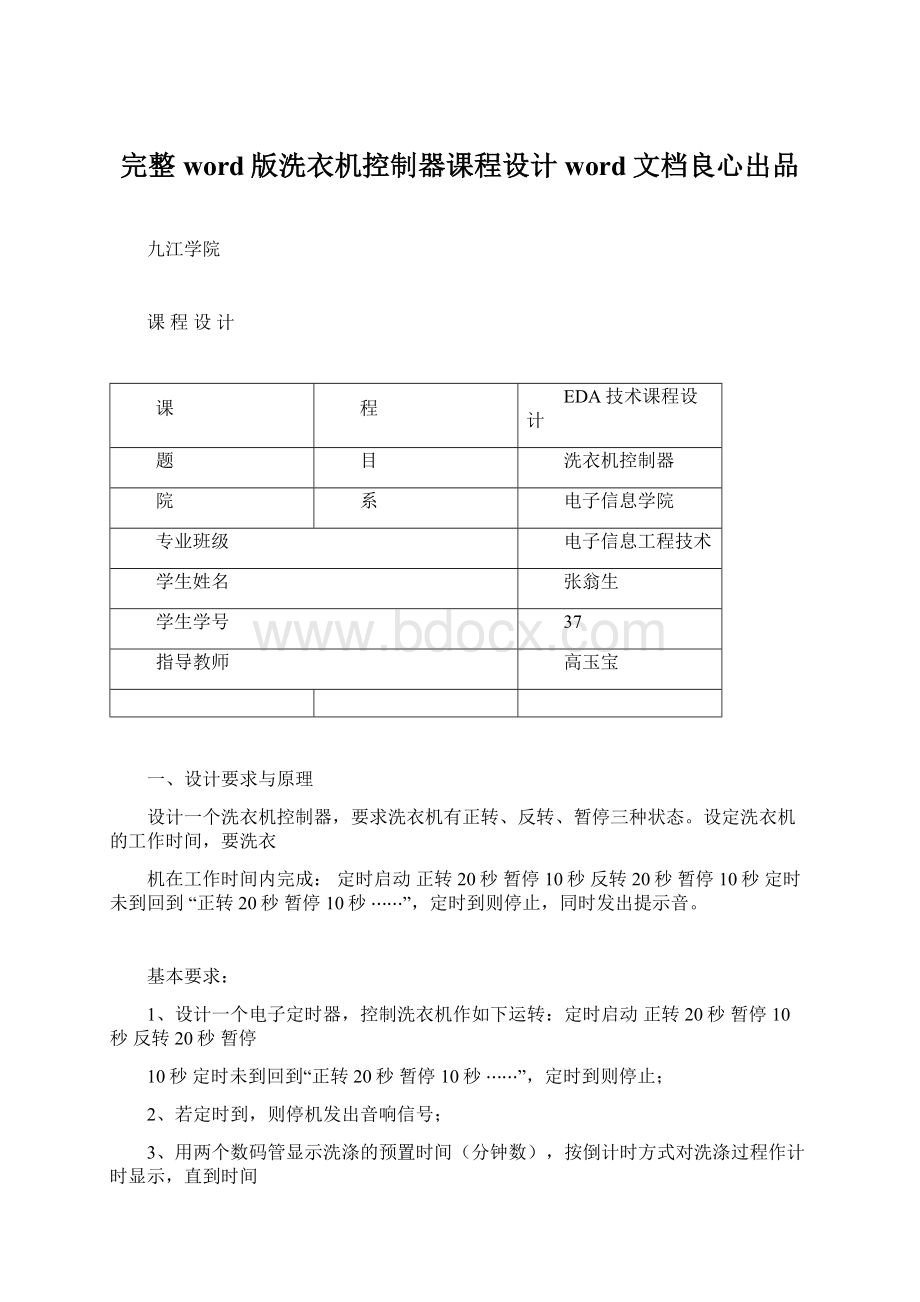

九江学院

课程设计

课

程

EDA技术课程设计

题

目

洗衣机控制器

院

系

电子信息学院

专业班级

电子信息工程技术

学生姓名

张翁生

学生学号

37

指导教师

高玉宝

一、设计要求与原理

设计一个洗衣机控制器,要求洗衣机有正转、反转、暂停三种状态。

设定洗衣机的工作时间,要洗衣

机在工作时间内完成:

定时启动正转20秒暂停10秒反转20秒暂停10秒定时未到回到“正转20秒暂停10秒⋯⋯”,定时到则停止,同时发出提示音。

基本要求:

1、设计一个电子定时器,控制洗衣机作如下运转:

定时启动正转20秒暂停10秒反转20秒暂停

10秒定时未到回到“正转20秒暂停10秒⋯⋯”,定时到则停止;

2、若定时到,则停机发出音响信号;

3、用两个数码管显示洗涤的预置时间(分钟数),按倒计时方式对洗涤过程作计时显示,直到时间

到停机;洗涤过程由“开始”信号开始;

4、三只LED灯表示“正转”、“反转”、“暂停”三个状态。

二、洗衣机的工作过程

首先用电路控制三只LED显示洗衣机正转、反转、暂停三种状态。

然后用电子定时器控制洗衣机设

定的工作时间,以及正传和反转运行时间的控制。

同时用两个数码管显示洗涤的预置时间(按分钟计数),

按倒计时方式对洗涤过程作计时显示,直到时间到停机;洗涤过程由“开始”信号开始;最后定时到则停止,

同时用蜂鸣器发出提示音。

通过各种开关组成控制电路,使洗衣机实现程序运转。

直至结束为止。

三、各模块图

洗衣机控制电路由定时输入模块,电机输出模块,电机时间控制模块,数字显示电路,倒计时模块以及报警器模块组成。

循

控制循环时间

按键控制模块

环

控

制

电

路

数字显示模块

,

使

其

在

倒计时模块

定时输入模块

三

个

状

态

转

报警电路

换

图一

四、各模块的VHDL代码与仿真结果

1、输入定时模块,

此模块是为了实现希望让洗衣机工作多少个分钟,有两个数码管显示工作时间,所以可以不同要求

输入要洗衣的时间,可以输入1~59分钟不等时间,人性化控制,与实际的洗衣机工作是一样的。

程序如下:

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entityshuruis

Port(shu:

instd_logic;

hshu:

instd_logic;

din:

instd_logic;

dout:

outstd_logic_vector(3downto0);

dout1:

outstd_logic_vector(3downto0));

endshuru;

architectureBehavioralofshuruis

signalcount:

std_logic_vector(3downto0);

signalcount1:

std_logic_vector(3downto0);

begin

process(shu,hshu,din)

begin

dout<=count;

dout1<=count1;

ifdin='0'then

dout<="1111";dout1<="1111";

elsifrising_edge(shu)then

ifcount="1001"then

count<="0000";

else

count<=count+1;

endif;

endif;

ifrising_edge(hshu)then

ifcount1="0110"then

count1<="0000";

else

count1<=count1+1;

endif;

endif;

endprocess;

endBehavioral;

仿真波形如下

2、产生1HZ频率的信号

此程序是将学校试验箱上提供的

48MHZ

的信号分频成

1HZ

频率的信号,这样可以一秒进行计数,程

序很简单,如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

entityfp48Mis

port(clk_48MHZ:

instd_logic;

clk_1HZ:

outstd_logic

);

endfp48M;

architecturebehavoffp48Mis

signalclk_1HZ_r:

std_logic;

signalcount:

std_logic_vector(24downto0);

begin

process(clk_48MHZ)

begin

ifclk_48MHZ'eventandclk_48MHZ='1'then

ifcount="1011011100011010111111111"then

count<=(others=>'0');

clk_1HZ_r<=notclk_1HZ_r;

elsecount<=count+1;

clk_1HZ<=clk_1HZ_r;

endif;

endif;

endprocess;

endbehav;

3、提供定时脉冲模块

此模块提供1分钟产生一个高电平和5秒产生一个高电平,这两个脉冲为后面的循环和控制60秒减一分钟有很多的作用,起到后面的链接作用,同时可以根据自己来设置各状态工作时间,这可以和后

面的循环控制一起来控制,程序如:

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitywashmachineis

Port(clk:

instd_logic;

c:

outstd_logic;

d:

outstd_logic);

endwashmachine;

architecturemiao20ofwashmachineis

signalcount:

std_logic_vector(2downto0);

signalshi:

integerrange0to60;

begin

process(clk)

begin

ifrising_edge(clk)then

ifshi=60then

shi<=0;c<='1';

elseshi<=shi+1;c<='0';

endif;

ifcount="100"then

count<="000";

d<='1';

else

count<=count+1;

d<='0';

endif;

endif;

endprocess;

endmiao20;

仿真波形如下:

4、循环控制模块

此模块是为了实现能够控制洗衣机正转、反转、暂停的功能,同时也可以和前一模块一起控制各个状态的工作时间。

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitydianjiis

Port(

cc:

instd_logic;

deng:

outstd_logic_vector(2downto0));

enddianji;

architecturediofdianjiis

signalcount:

std_logic_vector(3downto0);

signaldeng1:

std_logic_vector(2downto0);

begin

deng<=deng1;

process(cc)

begin

ifrising_edge(cc)then

ifcount="1010"then

count<="0000";

else

count<=count+1;

endif;

ifcount="0000"then

deng1<="011";

elsifcount="0100"then

deng1<="101";

elsifcount="0110"then

deng1<="110";

endif;

endif;

endprocess;

enddi;

仿真波形如下:

5、分钟的个位控制

根据课程设计要求,把工作状态及工作时间显示出来,按下KEY5键就可以显示工作时间的分钟个位

显示在数码管上,可以根据洗衣不同要求设置同时可以控制分钟的十位时间,当个位分钟为0时下一个分

钟个位脉冲过来分钟的十位就减1程序如下:

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entityfen_lis

Port(jian:

instd_logic;

reset:

instd_logic;

din:

instd_logic_vector(3downto0);

dout:

outstd_logic_vector(3downto0);

c:

outstd_logic);

endfen_l;

architectureBehaveoffen_lis

signalcount:

std_logic_vector(3downto0);

begin

dout<=count;

process(jian,reset,din)

begin

ifreset='0'then

count<=din;

c<='0';

elsifrising_edge(jian)then

ifcount="0000"then

count<="1001";

c<='1';

else

count<=count-1;

c<='0';

endif;

endif;

endprocess;

endBehave;

仿真波形如下:

6、分钟的十位控制

根据课程设计要求,把工作状态及工作时间显示出来,按下KEY5键就可以显示工作时间的分钟十位

显示在数码管上,可以根据洗衣不同要求设置,这和上面程序相似,当个位分钟为0时下一个分钟个位脉

冲过来分钟的十位就减1程序如下:

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entityfen_his

Port(jian:

instd_logic;

reset:

instd_logic;

din:

instd_logic_vector(3downto0);

dout:

outstd_logic_vector(3downto0);

c:

outstd_logic);

endfen_h;

architectureBehaveoffen_his

signalcount:

std_logic_vector(3downto0);

begin

dout<=count;

process(jian,reset,din)

begin

ifreset='0'then

count<=din;

c<='0';

elsifrising_edge(jian)then

ifcount="0000"then

count<="1001";

c<='1';

else

count<=count-1;

c<='0';

endif;

endif;

endprocess;

endBehave;

7、数码管显示模块

此模块是显示要洗衣的时间,这个时间是可以在前面的控制模块控制的,安下KEY5键就可以显示时

间。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_Arith.ALL;

USEIEEE.STD_LOGIC_Unsigned.ALL;

ENTITYxianshi_ledIS

PORT(

clk_2k:

INSTD_LOGIC;

d:

INSTD_LOGIC_VECTOR(7DOWNTO0);--输入要显示的数据

dig:

OUTSTD_LOGIC_VECTOR(7DOWNTO0);--数码管选择输出引脚

seg:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)--数码管段输出引脚

);

ENDENTITY;

ARCHITECTUREoneOFxianshi_ledIS

SIGNAL

seg_r:

STD_LOGIC_VECTOR(7DOWNTO0);--

定义数码管输出寄存器

SIGNAL

dig_r:

STD_LOGIC_VECTOR(7DOWNTO0);--

定义数码管选择输出寄存器

SIGNALdisp_dat:

STD_LOGIC_VECTOR(3DOWNTO0);

--定义显示数据寄存器

SIGNALcount:

STD_LOGIC_VECTOR(2DOWNTO0);

--定义计数寄存器

BEGIN

dig<=dig_r;

seg<=seg_r;

PROCESS(clk_2k)

BEGIN

IFRISING_EDGE(clk_2k)THEN

count<=count+1;

ENDIF;

ENDPROCESS;

PROCESS(clk_2k)

BEGIN

IFRISING_EDGE(clk_2k)THEN

CASEcountIS

WHEN"000"=>disp_dat<=d(7DOWNTO4);--第一个数码管

WHEN"001"=>disp_dat<=d(3DOWNTO0);--第二个数码管

whenothers=>null;

ENDCASE;

CASEcountIS--选择数码管显示位

WHEN"000"=>dig_r<="01111111";--选择第一个数码管显示

WHEN"001"=>dig_r<="10111111";--选择第二个数码管显示

whenothers=>null;

ENDCASE;

ENDIF;

ENDPROCESS;

PROCESS(disp_dat)

BEGIN

CASEdisp_datIS

WHEN

X"0"=>seg_r<=X"c0";--显示0

WHENX"1"=>seg_r<=X"f9";--

显示1

WHENX"2"=>seg_r<=X"a4";--

显示2

WHENX"3"=>seg_r<=X"b0";--

显示3

WHENX"4"=>seg_r<=X"99";--

显示4

WHENX"5"=>seg_r<=X"92";--

显示5

WHENX"6"=>seg_r<=X"82";--

显示6

WHENX"7"=>seg_r<=X"f8";--

显示7

WHENX"8"=>seg_r<=X"80";--

显示8

WHENX"9"=>seg_r<=X"90";--

显示9

WHENX"a"=>seg_r<=X"88";--

显示a

WHENX"b"=>seg_r<=X"83";--

显示b

WHENX"c"=>seg_r<=X"c6";--

显示c

WHENX"d"=>seg_r<=X"a1";--

显示d

WHENX"e"=>seg_r<=X"86";--

显示e

WHENX"f"=>seg_r<=X"8e";--

显示f

ENDCASE;

ENDPROCESS;

END;

8、提供数码管工作频率模块

由于数码管要工作在2KHZ的频率信号下有所需要将试验箱

48MHZ的信号分频分频成

2KHZ,此程序

和产生1HZ是一样的程序如下:

LIBRARY

IEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

entityfp2kis

port(clk_48MHZ:

instd_logic;

clk_2KHZ:

outstd_logic

);

endfp2k;

architecturebehavoffp2kis

signalclk_2KHZ_r:

std_logic;

signalcount:

std_logic_vector(14downto0);

begin

process(clk_48MHZ)

begin

ifclk_48MHZ'eventandclk_48MHZ='1'then

ifcount="10111011011111"then

count<=(others=>'0');

clk_2KHZ_r<=notclk_2KHZ_r;

elsecount<=count+1;

clk_2KHZ<=clk_2KHZ_r;

endif;

endif;

endprocess;

endbehav;

五、将各个模块连接及其目标器件选择

将各个模块的

VHDL

语言生产原理图模块器件,将各个模块连接如下图:

shuru

key

1_in

INPUT

shu

dout[3..0]

fen_l

PIN_C13

key

2_in

VCC

INPUT

hshu

dout1[3..0]

d[3..0]

PIN_D13

key

4_in

VCC

xianshi_led

INPUT

din

jian

dout[3..0]

VCC

PIN_P1

OUTPUT

dig[7..0]

inst7

reset

c

clk_2k

dig[7..0]

PIN_L6

din[3..0]

d[7..0]

d[7..0]

seg[7..0]

OUTPUT

seg[7..0]

PIN_K5

PIN_G3

inst1

PIN_J4

inst

PIN_J3

PIN_K4

key5_in

INPUT

fen_h

fp2k

PIN_J8

VCC

d[7..4]

PIN_L3

PIN_AD13

PIN_M3

jian

dout[3..0]

PIN_M4

fp48M

washmachine

clk_48MHZ

clk_2KHZ

PIN_K6

reset

c

PIN_J6

clk_48M_in

INPUT

clk_48MHZ

clk_1HZ

clk

c

din[3..0]

PIN_U10

PIN_N9

VCC

PIN_N2

d

inst2

inst3

PIN_L10

PIN_L9

inst11

inst4

OUTPUT

G_IN

PIN_P18

dianji

cc

deng[2..0]

OUTPUT

led_out[2..0]

PIN_P7

PIN_P9

PIN_R5

inst12

六、实训总结

这次EDA课程设计虽然只有一个星期但是还是学到了很多东西,老师给我们很多的题目让我们自己选

择一个做,我先看了下那几个题目,感觉自己可以尝试做几个,虽然老师说要我们去网