第六章DSP应用系统设计.docx

《第六章DSP应用系统设计.docx》由会员分享,可在线阅读,更多相关《第六章DSP应用系统设计.docx(19页珍藏版)》请在冰豆网上搜索。

第六章DSP应用系统设计

第六章DSP应用系统设计

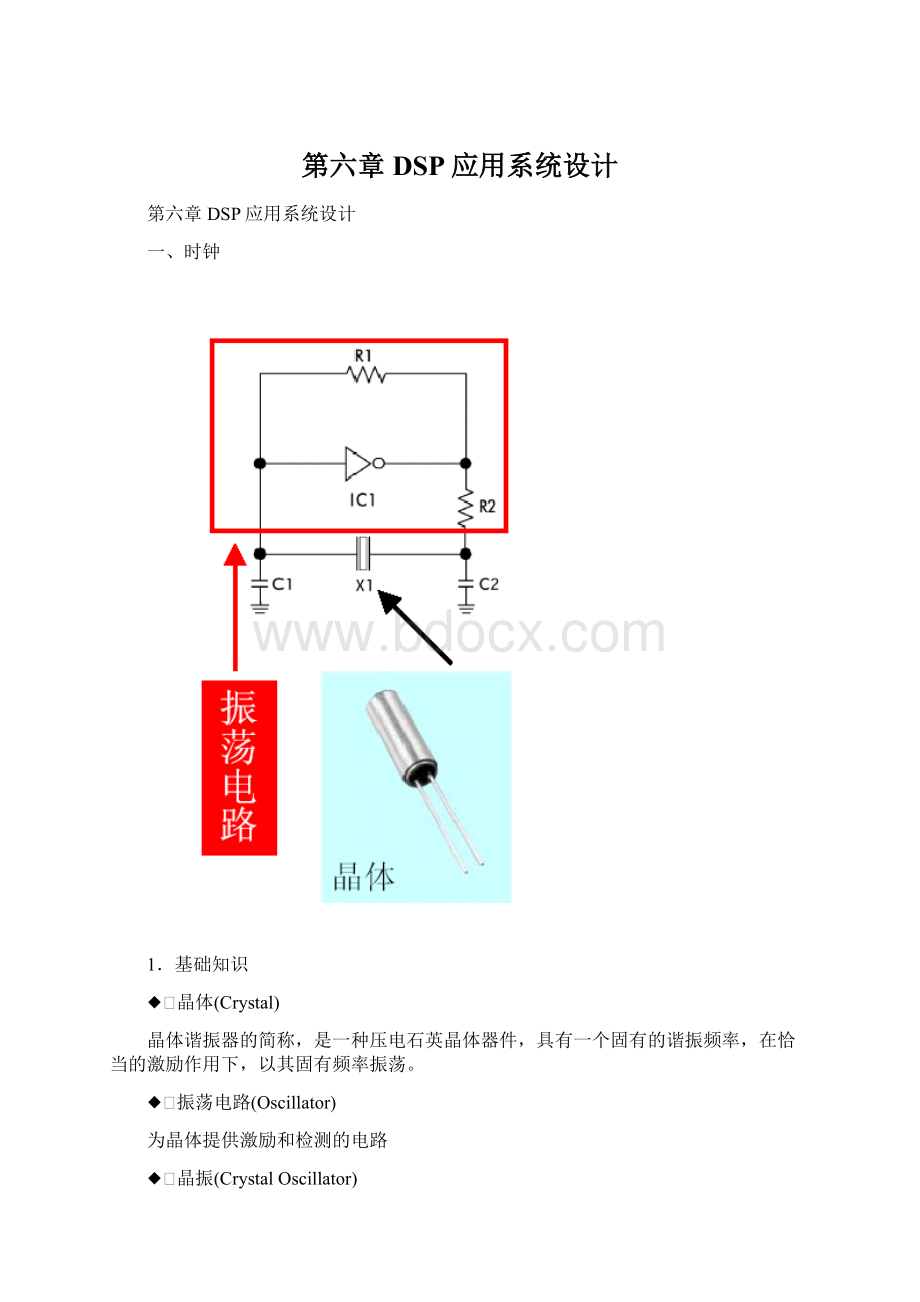

一、时钟

1.基础知识

◆晶体(Crystal)

晶体谐振器的简称,是一种压电石英晶体器件,具有一个固有的谐振频率,在恰当的激励作用下,以其固有频率振荡。

◆振荡电路(Oscillator)

为晶体提供激励和检测的电路

◆晶振(CrystalOscillator)

将晶体、振荡器和负载电容集成在一起,其输出直接为一方波时钟信号。

◆锁相环电路PLL(Phase-LockedLoops)

用于对输入时钟信号进行分频或倍频的电路晶体

2.哪些器件需要时钟

◆DSP

ØCPU时钟

ØEMIF时钟(仅C55x和C6000系列DSP)

◆串行通信器件

ØUART

ØUSB

Ø……

◆音频/视频器件

ØAudioCodec器件

ØVideoDecoder和Encoder器件

◆……

3.器件的时钟选项

◆大多数器件片内均包含振荡电路,只需外加晶体和2个负载电容即可产生所需的时钟信号。

也可禁止片内振荡电路,直接由外部提供时钟信号

◆TIDSP更提供多种灵活的时钟选项:

Ø片内/片外振荡器

Ø片内PLL

ØPLL分频/倍频系数可由硬件/软件配置

不同的DSP时钟可配置的能力可能不同,使用前应参考各自的数据手册

4.时钟电路

a.由晶体+内部振荡器产生

InternalOscillator

◆优点:

Ø电路简单:

只需晶体+2个电容

Ø价格便宜,占地小

Ø时钟信号电平自然满足要求

◆缺点:

Ø驱动能力差,不能同时供给其他器件使用

Ø频率范围小:

20KHz~60MHz

◆注意事项:

Ø负载电容:

配置正确的负载电容

ØC6000、C5510等DSP无OSC

b.由晶振(Oscillator)产生

◆优点:

Ø电路简单

Ø占地小

Ø频率范围宽:

1MHz~400MHz

Ø驱动能力强:

可提供多个器件使用

◆缺点:

Ø成本较高

Ø频率生产时已确定,多个独立的时钟需要多个晶振

◆注意事项:

Ø使用时要注意时钟信号电平,一般为5V或3.3V,要求1.8V电平的时钟不能选用,如VC5401、VC5402、VC5409和F281x

c.由可编程时钟芯片产生

◆优点:

Ø电路简单、占地小:

可编程时钟芯片+晶体+2个外部电容

Ø多个时钟输出,可产生特殊的频率值,适合于多时钟源的系统

Ø驱动能力强:

可提供多个器件使用

Ø频率范围宽:

最大可达200MHz

◆缺点:

Ø成本较高,但对于多时钟源系统来说,总体成本较低

◆注意事项:

Ø输出时钟信号电平一般为5V或3.3V

◆常用器件:

ØCY22381(3个独立的PLL、3个时钟输出引脚)$1.4

ØCY2071A(1个PLL、3个时钟输出引脚)

5、时钟信号电气指标

◆频率

◆信号电平

◆时钟上升时间和下降时间

◆高/低电平脉冲宽度

◆占空比

◆驱动能力

6.时钟电路选择原则

◆系统中要求多个不同频率的时钟信号时,首选可编程时钟芯片

◆单一时钟信号时,选择晶体时钟电路

◆多个同频时钟信号时,选择晶振

◆尽量使用DSP片内的PLL,降低片外时钟频率,提高系统的稳定性

◆C6000、C5510、C5409A、C5416、C5420、C5421和C5441等DSP片内无振荡电路,不能用晶体时钟电路

◆VC5401、VC5402、VC5409和F281x等DSP时钟信号的电平为1.8V,建议采用晶体时钟电路

7.时钟电路设计注意事项

◆用被动元件滤波方式给时钟电路供电,供电电源加10~100μF

钽电容旁路,每个电源引脚加0.01~0.1μF瓷片电容去耦

◆晶振、负载电容、PLL滤波器等应尽可能靠近时钟器件

◆在靠近时钟源的地方串接10–50Ω端接电阻,以提高时钟波形

的质量

二、复位电路

1.复位信号的作用

2.需要复位信号的电路

DSP存储器外围接口芯片可编程逻辑芯片……

3.典型DSP复位电路

简单的RC电路

复位芯片:

如TPS3305,TPS3308,IMP811/812

三、电源设计

1.DSP系统需要的电源种类

TIDSP上有5类典型电源引脚:

①CPU内核(CORE)电源引脚V=1.2—1.9V

②I/O电源引脚

③PLL电路电源引脚

④Flash编程电源引脚(仅C2000系列DSP有)

⑤模拟电路电源引脚(仅C2000、C55系列DSP有)

2.数字电源和模拟电源

3.电源滤波

◆旁路电容起电荷池的作用,以减少电源上的噪声

◆大容量电容用电解电容或陶瓷电容,小旁路电容一般采用陶瓷电容

◆通常每个电源引脚加一个旁路电容,以平滑电源的波动

◆滤波电容器引脚越短越好

4.供电方案及器件选型

5.上电次序

a.CPU内核先于I/O上电,后于I/O掉电

b.CPU内核与I/O供电应尽可能同时,二者时间相差不能太长(一般不能>1s,否则会影响器件的寿命或损坏器件)。

C.为了保护DSP器件,应在CPU内核电源与I/O电源之间加一肖特基二极管

6.电源监视与系统监视

a.SVS:

电源电压监视器件

b.主要功能:

监测电源电压,当不满足要求时,产生复位信号

c.辅助功能:

上电复位、手动复位、看门狗电路

7.常用的SVS器件

ØTPS3823-33:

具有电压监测、上电复位、手动复位和看门狗电路

ØTPS3809K33:

仅有电压监测和上电复位功能

8.电源电路实例

F2812DSK

四、存储器设计

1.异步存储器接口

ØSRAM、Flash、NvRAM……

Ø许多模拟/数字I/O也采用异步存储器接口形式

2.同步存储器接口

Ø同步静态存储器:

SBSRAM、ZBTSRAM

Ø同步动态存储器:

SDRAM

Ø同步FIFO

TIDSP外部存储器接口

存储器类型

C2000

C3X

C54

C55

C62/67

C64

异步存储器

●

●

●

●

●

●

SBSRAM

●

●

●

ZBTSRAM

●

●

SDRAM

●

●

●

同步FIFO

●

●

●

数据宽度

16

32

16

8

16

8

16

32

8

16

32

64

3.LF2407A存储器接口

LF2407A的外部数据存储器空间为8000~FFFFH,共32KB

电路说明:

a.2407A的外部程序存储器和数据存储器共用同一片SRAM

b.外部程序存储器的地址空间为0000~FFFFH

c.外部数据存储器的地址空间为8000~FFFFH

d.SRAM必需用3.3V电压供电

e.要注意SRAM的速度等级,一般选12ns为好。

f.使用中要注意程序空间的重叠问题

五、I/O口设计和电平转换

1.利用DSP本身的I/O口资源

特点:

充分利用了系统资源

例:

LF2407A

BIO,XF

EVA,EVB

SCI

CAN

SPI

ADC(用模拟输入判断数字电平)

2.CPLD扩展I/O口

特点:

系统芯片少,保密性强

3.利用小规模逻辑芯片扩展

输入:

74LVTH244,74LVC16244

输出:

74LVTH373

4.可编程逻辑器件在DSP应用系统设计中的应用

①为什么需要可编程逻辑电路?

Ø有许多复杂的时序逻辑用普通的门电路无法实现

Ø利用可编程逻辑电路设计可降低成本、减小体积和系统功耗

Ø可以提高系统设计的灵活性

Ø可有效提高产品的技术保密性

②怎样使用可编程逻辑电路?

Ø功能设计:

利用专门的工具软件如VHDL、VERILOJICHDL、ABEL等设计系统功能。

Ø性能仿真:

利用逻辑仿真软件对输入/输出波形进行波形分析和仿真测试,测试精度可达0.1ns。

Ø芯片编程:

利用专用工具将设计代码下载到可编程逻辑器件中。

③怎样选择可编程逻辑电路?

常用的可编程逻辑电路有如下几种类型:

FPGA-现场可编程逻辑器件,可达100万门(gate)

CPLD-复杂可变程器件,1000门~几万门

GAL-通用阵列逻辑,1000门以下

PAL-可编程阵列逻辑,1000门以下

④主要的供货厂商:

XINLINXALTERAActelLatticeAtmel

CYPRESS

六、电平转换

1.为什么需要电平变换

ØDSP系统中难免存在5V/3.3V混合供电现象

ØI/O为3.3V供电的DSP,其输入信号电平不允许超过电源电压3.3V

Ø5V器件输出信号高电平可达4.4V

Ø长时间超常工作会损坏DSP器件

Ø输出信号电平一般无需变换

2.电平变换的方法:

Ø总线收发器(BusTransceiver):

v常用器件:

SN74LVTH245A(8位)、SN74LVTH16245A(16位)

v特点:

3.3V供电,需进行方向控制,延迟:

3.5ns,驱动:

-32/64mA,输入容限:

5V

v应用:

数据、地址和控制总线的驱动

Ø总线开关(BusSwitch)

v常用器件:

SN74CBTD3384(10位)、SN74CBTD16210(20位)

v特点:

5V供电,无需方向控制,延迟:

0.25ns,驱动能力不增加

v应用:

适用于信号方向灵活、且负载单一的应用,如McBSP等外设信号的电平变换

Ø2选1切换器(1of2Multiplexer)

v常用器件:

SN74CBT3257(4位)、SN74CBT16292(12位)

v特点:

实现2选1,5V供电,无需方向控制,延迟:

0.25ns,驱动能力不增加

v应用:

适用于多路切换信号、且要进行电平变换的应用,如双路复用的McBSP

ØCPLD

v3.3V供电,但输入容限为5V,并且延迟较大:

>7ns,适用于少量的对延迟要求不高的输入信号

Ø电阻分压

v10KΩ和20KΩ串联分压,5V×20÷(10+20)≈3.3V

七、人机接口

1.键盘设计

简单按键

行列式键盘

2.显示器设计

LED、LCD七段数码管

点阵式液晶显示器

图像显示器:

CRTLCDELD

VFD(荧光真空管显示器)

八、通信接口设计:

SPI

特点:

I2C

CAN

UART

USB

◆C5509DSP片内集成有USB1.1功能

◆外部扩展USB器件

ØUSB器件按传输速率分为:

v低速:

1.5Mbps

v全速:

12Mbps(USB1.1)

v高速:

480Mbps(USB2.0)

ØUSB接口组成:

vUSB发生器:

实现USB的电气连接(物理层)

vUSB串行接口引擎SIE:

实现USB底层通信协议(链路层)

v微处理器:

编程实现各种应用(应用层)

Ø新设计的DSP系统一般选用USB2.0

ØCypress公司是全球最大的USB接口器件的供应商,其产品系列最全,开发最方便

ØCypress公司USB2.0器件按实现的功能可分为

vUSB收发器:

链路层和应用层全由与之配合的处理器实现

CY7C68000

vUSB智能引擎:

USB收发器+SIE,与之配合的处理器只需实现应用层

CY7C68001

vUSB控制器:

USB收发器+SIE+MCU,与之配合的处理器只需与MCU进行数据交换

CY7C68013

ØDSP系统中一般选用USB智能引擎或USB控制器

1394(firewire):

用于视频音频接口

Ethernet(网络)

九、A/DD/A

1.通用A/D、D/A

DSP应用系统中一般采用速度较高的A/D、D/A芯片,

2.专用A/D、D/A

视频编解码芯片:

SAA7111A,SAA7121,ADV7177

CCD/CIS专用数据采集芯片:

AD9848

十、功率接口设计

电机驱动:

主要是C2000系列

十一、HPI接口

1.HPI概念

◆什么是HPI

ØHost-PortInterface的缩写,即主机接口,是一种高速、异步并行接口(8/16/32位)

Ø外部主处理器通过HPI接口可以高速访问DSP的局部或全部存储空间

ØHPI接口是以主处理器为主,DSP为从的主-从结构

◆DSP中设置HPI接口的目的

Ø为主-从结构的多处理器系统提供简单、方便、廉价的信息交换平台

◆传统的双处理器接口

Ø异步/同步串口:

速度慢

Ø双端口RAM:

成本高,局部存储空间,信息量有限

Ø双向FIFO:

成本高,受FIFO深度限制,信息量有限

◆能与何种类型的主处理器直接接口

Ø数据/地址分时复用的主处理器

Ø数据/地址独立的主处理器

Ø读/写控制独立的主处理器

Ø读/写控制复合的主处理器

2.HPI接口信号

◆数据:

ØHD[n:

0]:

n=7、15、31,即数据总线宽度为8/16/32位

◆地址:

ØHCNTL[1:

0]:

用于选择3个寄存器HPIA、HPID和HPIC

ØHHWIL/HBIL:

当HPI数据总线宽度是DSP数据总线宽度的一半时,用于指示前、后2次传输,如果总线宽度相同时,无此信号

ØHR/W#:

用于指示HPI传输的方向

◆控制:

ØHDS[2:

1]#、HCS#:

数据选通

ØHAS#:

地址锁存

◆握手:

ØHRDY:

HPI接口数据就绪信号

ØHINT#:

DSP请求主机中断信号

3.HPI接口时序

◆HAS#信号

Ø用HAS#信号时,HAS#信号应先于HDS[2:

1]#、HCS#有效,其下降沿用于锁存HCNTL[1:

0]、HHWIL/HBIL和HR/W#信号

Ø不用HAS#信号时,应将其固定接高电平“1”

◆HDS[2:

1]#、HCS#

Ø组合产生内部选通信号HSTROBE#

Ø不用HAS#信号时,HCNTL[1:

0]、HHWIL/HBIL和HR/W#信号由HSTROBE#的下降沿锁存

Ø当HR/W#为高,即读HPI时,HSTROBE#的下降沿初试化读操作

Ø当HR/W#为低,即写HPI写,HSTROBE#的上升沿初试化写操作

4.HPI接口配置

◆TIDSP中只有C5000和C6000系列DSP中有HPI接口

◆C54x系列DSP:

8位HPI接口

◆C55x系列DSP:

16位HPI接口

◆C62x/C67x系列DSP:

16位HPI接口

◆C64x系列DSP:

32位HPI接口

◆HPI接口的数据总线可配置为通用的I/O口

十二、电磁兼容性设计(EMC)

1.磁兼容性的基本概念

EMC:

ElectromagneticCompatibility

EMC要解决的问题:

骚扰源是什么?

耦合路径是什么?

敏感电路是什么?

解决方法是什么?

2.典型的EMC设计手段

屏蔽:

屏蔽盒屏蔽线

滤波:

电源滤波信号滤波(模拟,数字)

隔离:

在信号通道上实现

隔离放大器

光电隔离器

无线收发器

PCB设计方案:

电路方案选择:

模拟VS数字

信号传输模式:

单端传送——RS-232

差分传送——RS-485

元器件选择:

模拟器件:

带宽—适用即可

CMRR,PSRR—越高抑制干扰能力越强

数字器件:

工作频率(Tr/Tf)—适用即可

噪声容限—优选CMOS器件

地线设计:

接地点—低频点、高频面接地

信号环路—尽量减小环路面积

布线优化设计

十三、信号完整性设计

信号完整性(SignalIntegrity):

指信号在传输线上的传输质量

信号频率F=1/(Tr×π)Tr=3nsF=106Mhz

影响信号完整性的主要原因:

反射(reflection)

串扰(crosstalk)

过冲(overshoot)

下冲(undershoot)

SI设计中要注意的问题:

1.电子器件的工作速度不是越高越好

2.要注意传输线的阻抗匹配

3.高速信号线要尽量的短,并且长度要保持一致

4.PCB设计中尽量减小串扰

十四、时序设计

参照数据手册(LF2407A)

十五、BOOT接口设计

1.什么是BOOT技术

2.什么DSP中要采用BOOT技术

十六、DMA功能的应用

参照数据和用户手册

十七、硬件设计时应注意的其它问题

1.未用的输入/输出引脚的处理

◆未用的输入引脚不能悬空不接,而应将它们上拉或下拉为固定的电平

Ø关键的控制输入引脚,如Ready、Hold等,应固定接为适当的状态

vReady引脚应固定接为有效状态

vHold引脚应固定接为无效状态

Ø无连接(NC)和保留(RSV)引脚

vNC引脚:

除非特殊说明,这些引脚悬空不接

vRSV引脚:

应根据数据手册具体决定接还是不接

Ø非关键的输入引脚

v将它们上拉或下拉为固定的电平,以降低功耗

◆未用的输出引脚可以悬空不接

◆未用的I/O引脚

Ø如果缺省状态为输入引脚,则作为非关键的输入引脚处理,上拉或下拉为固定的电平

Ø如果缺省状态为输出引脚,则可以悬空不接

2.特殊的逻辑用CPLD实现

Ø高集成度、高可靠性

Ø时序关系整齐,延迟一致

Ø易于修改,易于实现复杂的组合或时序逻辑

3.测试点

读/写控制、时钟、电源、地等重要信号应加测试点,或连接至连接器、或逻辑分析仪插头上,方便今后的硬件调试。

4.提供手动复位开关,方便今后的硬件调试。