简易数字信号传输性能分析仪设计报告 精品.docx

《简易数字信号传输性能分析仪设计报告 精品.docx》由会员分享,可在线阅读,更多相关《简易数字信号传输性能分析仪设计报告 精品.docx(25页珍藏版)》请在冰豆网上搜索。

简易数字信号传输性能分析仪设计报告精品

简易数字信号传输性能分析仪

摘要:

本题设计一个简易数字信号传输性能分析仪,CycloneIVFPGA芯片为核心,由FPGA内部50MHz时钟通过PLL锁相环电路分频得到10kbps-100kbps数据率10kbps为步进的数字信号和数据率10Mbps的伪随机信号。

通过必要的外设辅助电路(衰减电路、滤波电路、加法电路等)来模拟传输信道的幅频特性和噪声。

最终由数字信号分析电路提取出输入信号的同步时钟信号,并在模拟示波器上显示眼图。

关键词:

m序列数字信号眼图FPGA

一、系统整体设计

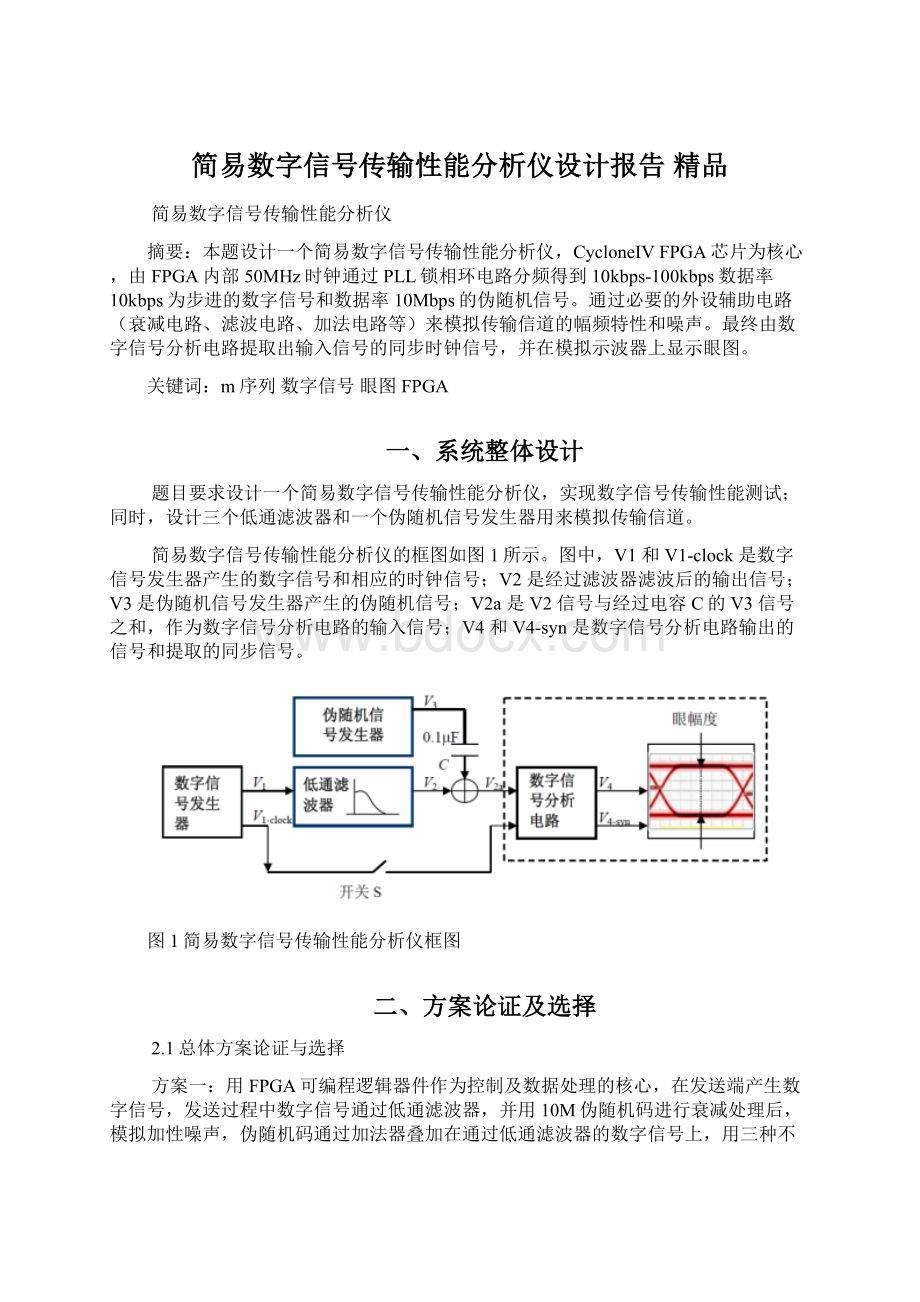

题目要求设计一个简易数字信号传输性能分析仪,实现数字信号传输性能测试;同时,设计三个低通滤波器和一个伪随机信号发生器用来模拟传输信道。

简易数字信号传输性能分析仪的框图如图1所示。

图中,V1和V1-clock是数字信号发生器产生的数字信号和相应的时钟信号;V2是经过滤波器滤波后的输出信号;V3是伪随机信号发生器产生的伪随机信号;V2a是V2信号与经过电容C的V3信号之和,作为数字信号分析电路的输入信号;V4和V4-syn是数字信号分析电路输出的信号和提取的同步信号。

图1简易数字信号传输性能分析仪框图

二、方案论证及选择

2.1总体方案论证与选择

方案一:

用FPGA可编程逻辑器件作为控制及数据处理的核心,在发送端产生数字信号,发送过程中数字信号通过低通滤波器,并用10M伪随机码进行衰减处理后,模拟加性噪声,伪随机码通过加法器叠加在通过低通滤波器的数字信号上,用三种不同的低通滤波器模拟三种不同的信道,在接收端进行一定的数字信号处理,最终输出用模拟示波器来判断传输性能。

其系统框图如图2。

图2方案一系统框图

方案二:

采用MSP430单片机为控制核心,其系统框图如图3。

对输入信号进行放大或衰减后,用外接触发电路产生触发信号,通过A/D转换将模拟信号转换成数字信号,再通过单片机将数据锁存至外部RAM,然后由单片机控制将数据送至D/A输出。

图3方案二系统框图

综合比较上述方案,方案二以MSP430为核心产生的信号频率不高,稳定性不强,无法达到题目“产生数据率10kbps-100kbps数字信号和数据率10Mbps伪随机信号”的要求。

方案一既可以满足题设基本要求,又能充分发挥扩展部分,使系统达到更强的可控性和稳定性的同时保证数据率误差低于1%的高精确度,电路简洁,易于操作,所以采取方案一。

2.2低通滤波器电路方案选择与论证

方案一:

采用无源滤波器。

无源滤波器由无源元件(电阻、电容、电感)组成,具有高频性能好、电路简单、功能可靠、无需直流供电,能够输出高压大电流等优点。

但无源滤波器带负载能力较差,不但通带放大倍数会因负载电阻而减小,而且通带截至频率也会因负载电阻而增大。

同时无源滤波器的体积和重量也比较大,其电感还会引起电磁干扰。

方案二:

采用有源滤波器。

有源滤波器由电阻、电容和有源器件(如集成运放)组成,具有电路体积小重量轻、通带内信号可放大、精度高、性能稳定、易于调试、负载效应小、可多级相连构成高阶滤波器等诸多优点。

但由于集成运放所限,有源滤波电路不适于高电压大电流负载,而只适用于信号处理。

根据题目具体要求,综合考虑上述两方案,系统只需对弱电信号进行处理,且对于信号处理的精确性要求较为苛刻,因此方案二更为适合,设计分析四阶巴特沃斯有源滤波器理论带外衰减可达80dB/十倍频,满足题目要求,有效滤除带外信号,所以本系统采用的是四阶巴特沃斯低通滤波器。

2.3衰减器电路方案选择与论证

方案一:

采用T型网络衰减器。

其输入阻抗与输出阻抗可以随意改变,更容易进行匹配,电阻使用数量少,容易调试。

但缺点是电阻阻值都相对较小,在不使用高精密电阻时误差相对较大。

方案二:

采用π型网络衰减器。

其输入阻抗与输出阻抗可以随意改变,更容易进行匹配,电阻使用数量少,容易调试。

同时电阻阻值适中,容易进行测试。

因此我们选择此方案。

2.4加法器电路方案选择与论证

方案一:

采用QuartusII软件中LPM模块中的加法模块进行信号求和。

在FPGA芯片中直接使用加法器求和简单方便。

但是FPGA中的加法器是数字信号加法器,使用范围比较窄,不适用本系统的模拟噪声加载到数字信号上。

方案二:

采用集成运放构成的加法电路进行信号求和。

此类加法器为多段输入,可用于模拟电路与数字电路,用途广泛,易于调节。

可将幅值低的模拟噪声信号直接加载到幅值高的数字信号上去。

所以我们选用此方案。

三、理论分析与参数计算

3.1低通滤波器的分析设计

滤波器是一种使用信号通过而同时抑制无用频率信号的电子装置,在信息处理、数据传送和抑制干扰等自动控制、通信及其它电子系统中应用广泛。

滤波一般可分为有源滤波和无源滤波,有源滤波可以使幅频特性比较陡峭,而无源滤波设计简单易行,但幅频特性不如有源滤波器,而且体积较大。

从滤波器阶数可分为一阶和高阶,阶数越高,幅频特性越陡峭。

高阶滤波器通常可由一阶和二阶滤波器级联而成。

采用集成运放构成的RC有源滤波器具有输入阻抗高,输出阻抗低,可提供一定增益,截止频率可调等特点。

其典型结构如图4。

图4有源低通滤波器典型结构

(1)

其中,Y1~Y5为导纳,考虑到Up=UN,根据KCL可求得:

式

(1)是二阶压控电压源滤波器传递函数的一般表达式,式中,Auf=1+RF/R6。

只要适当选择Yi(

),就可以构成低通、高通、带通等有源滤波器。

二阶有源低通滤波器特性分析设Y1=1/R1,Y2=sC1,Y3=0,Y4=1/R2,Y5=sC2,将其代入式

(1)中,得到压控电压源型二阶有源低通滤波器的传递函数为

(2)

其中,A0=Auf=1+RF/R6

。

式

(2)为二阶低通滤波器传递函数的典型表达式。

其中,

为特征角频率,Q称为等效品质因数。

运放选择:

本题要求设计的三个低通滤波器的截止频率分别为100kHz、200kHz、500kHz。

截止频率误差绝对值不大于10%。

设计要求的截止频率较高,因此要求运放的频带较宽,选用通频带较宽的运放,本设计选用运放NE5532,带宽为10MHz,适合用于波形发生电路脉冲放大电路等。

3.2伪随机m序列数字信号的产生

m序列是目前广泛应用的一种伪随机序列,对于一个n级反馈移位寄存器来说,最多可以有2n个状态,对于一个线性反馈移位寄存器来说,全“0”状态不会转入其他状态,所以线性移位寄存器的序列的最长周期为2n-1。

当n级线性移位寄存器产生的序列{ai}的周期为T=2n-1时,称{ai}为n级m序列。

当反馈函数f(a1,a2,a3,…an)为非线性函数时,便构成非线性移位寄存器,其输出序列为非线性序列。

输出序列的周期最大可达2n,并称周期达到最大值的非线性移位寄存器序列为m序列。

数字信号发生器产生的m序列:

,(m序列的波形图与仿真图见附图9)。

图5数字信号发生器产生的m序列

伪随机信号发生器产生的m序列:

,(伪随机信号的波形图与仿真图见附图11)。

图6伪随机信号发生器产生的m序列

3.3同步信号的提取设计

本系统采用自同步方式提取同步信号,利用曼彻斯特编码将时钟信号和数据一同包含到数据流中,在传输代码信息的同时,也将时钟同步信号一起传输到信号分析电路中,通过分析电路中的数字锁相环从接收信号中恢复出与发端频率相同的码元时钟信号。

这样即可保证数字信号分析电路解调时在最佳时刻进行抽样判决,从而达到消除噪声干扰所导致的解调接收信号的失真,使接收端能以较低的错误概率恢复出被传输的数字信息的目的。

3.4眼图的显示方法分析

眼图是一系列数字信号在示波器上累积而显示的图形,其形状类似于眼睛,故叫眼图。

在用模拟示波器观察传输的数据信号时,使用被测系统的定时信号,通过示波器外触发或外同步对示波器的扫描进行控制,由于扫描周期此时恰为被测信号周期的整数倍,因此在示波器荧光屏上观察到的就是一个由多个随机符号波形共同形成的稳定图形。

实时示波器眼图实现原理如图8。

图8实时示波器眼图实现原理

示波器测量的一般信号是一些位或某一段时间的波形,更多的反映的是细节信息。

而眼图则反映的是链路上传输的所有数字信号的整体特性。

眼图的结构图如图9。

图9眼图的结构图

1.最佳抽样时刻应是“眼睛”张开最大的时刻;

2.眼图斜边的斜率决定了系统对抽样定时误差的灵敏程度;斜率越大,对定时误差越灵敏;

3.眼图的阴影区的垂直高度表示信号的畸变范围;

4.眼图中央的横轴位置对应于判决门限电平;

5.过零点失真为压在横轴上的阴影长度,有些接收机的定时标准是由经过判决门限点的平

均位置决定的,所以过零点失真越大,对定时标准的提取越不利。

6.抽样时刻上、下两阴影区的间隔距离之半为噪声容限,噪声瞬时值超过它就可能发生错误判决。

四、电路与软件设计

4.1FPGA最小系统板

FPGA最小系统板采用的是Altera公司CycloneIVFPGA芯片。

用FPGA可编程逻辑器件作为控制及数据处理的核心,FPGA内部集成锁相环,可以把外部时钟倍频,核心频率可以到几百MHz,而单片机运行速度低的多。

在高速场合,单片机无法代替。

FPGA管脚多,容易实现大规模系统。

(见附图1)

4.2低通滤波器的电路

滤波器选择巴特沃斯四阶低通滤波器,使用滤波器设计软件FilterLab设计电路。

在软件中选择巴特沃斯四阶低通滤波并设置不同的频率值可得到100KHz、200KHz、500KHz的低通滤波器电路图(分别见附图2,附图3,附图4)。

软件直接给出各电阻电容参数,方便简洁。

软件给出的参数如下,经试验滤波效果完全达到要求。

当fc=100KHz时,R1=3.57k,R2=8.66k,R3=12.4k,R4=16.9k,C1=820p,C2=100p,C3=120p,C4=100p。

当fc=200KHz时,R1=1.78k,R2=4.32k,R3=6.19k,R4=8.45k,C1=820p,C2=100p,C3=120p,C4=100p。

当fc=500KHz时,1=732k,R2=1.69k,R3=2.49k,R4=3.4k,C1=820p,C2=100p,C3=120p,C4=100p。

4.3信号调理电路

4.3.1加法器电路

加法器是产生数的和的装置。

加法器是一种数位电路,其可进行数字的加法计算。

本系统采用的是直接耦合放大器构成的加法电路。

因为信号包含10MHz的方波,所以考虑其高次谐波分量,放大器需要采用高带宽的才能保证信号合成的质量,所以我们使用增益带宽积为100MHz的THS3091作为加法器用的放大器(电路图见附图5,测试波形见附表4)。

4.3.2衰减器电路

衰减器是在指定的频率范围内,一种用以引入一预定衰减的电路。

一般以所引入衰减的分贝数及其特性阻抗的欧姆数来标明。

用衰减器实现放大器的输入端、输出端电平的控制、分支衰减量的控制。

本系统采用的是π型衰减网络,通过使用电位器调节输入阻抗来调节衰减倍数(见附图6)。

4.3.3增益调节电路

系统要求0.2—4倍可调,TTL电平电压至少为3.75V,要求为0.2倍,所以需要先进行衰减再放大。

本系统我们选用了OP37高性能运放,以电位器作为比例放大的反馈电阻,实现增益的手动调节(见附图7)。

4.4显示和按键电路

系统显示部分使用LCD12864液晶显示屏进行显示,LCD12864可显示字符和汉字。

本系统中用来显示预置的m序列频率。

按键部分使用4×4矩阵键盘,16个按键可分别设置不同的数值和频率的加减确认等。

矩阵键盘具有按键多,占用的IO口少的特点。

(电路图略)

4.5直流稳压电源电路

直流稳压电源部分采用自制的线性稳压电源,变压器将市电220V交流电转化为18V的交流电,通过整流、滤波、稳压得到系统所需要的直流电。

主控FPGA核心板使用3.3V供电,显示屏使用5V供电,加法器与滤波器均使用±15V为芯片供电。

(见附图8)

4.6软件设计

4.6.1编程环境和开发工具

本设计利用VHDL语言编写程序,QuartusII9.0作为开发及仿真工具。

FPGA采用VHDL语言编程,VHDL语言能够成为标准化的硬件描述语言并获得广泛应用,VHDL语言主要具有以下优点:

(1)VHDL语言功能强大,设计方式多样,VHDL语言具有强大的语言结构,只需采用简单明确的VHDL语言程序就可以描述十分复杂的硬件电路。

同时,它还具有多层次的电路设计描述功能。

(2)VHDL语言具有强大的硬件描述能力。

VHDL语言具有多层次的电路设计描述功能,描述方式既可以采用行为描述、寄存器传输描述或者结构描述,也可以采用三者的混合描述方式。

(3)VHDL语言具有很强的移植能力VHDL语言很强的移植能力主要体现在:

对于同一个硬件电路的VHDL语言描述,它可以从一个模拟器移植到另一个模拟器上、从一个综合器移植到另一个综合器上或者从一个工作平台移植到另一个工作平台上去执行。

(4)VHDL语言的设计描述与器件无关。

采用VHDL语言描述硬件电路时,设计人员并不需要首先考虑选择进行设计的器件。

这样做的好处是可以使设计人员集中精力进行电路设计的优化,而不需要考虑其他的问题。

当硬件电路的设计描述完成以后,VHDL语言允许采用多种不同的器件结构来实现。

QuartusII是Altera公司继Max+plusII之后开发的一种针对其公司生产的系列CPLD/PGFA器件的综合性开发软件,该软件界面友好,使用便捷,功能强大,是一个完全集成化的可编程逻辑设计环境,是先进的EDA工具软件。

该软件具有开放性、与结构无关、多平台、完全集成化、丰富的设计库、模块化工具等特点,支持原理图、VHDL、VerilogHDL以及AHDL(AlteraHardwareDescriptionLanguage)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

4.6.2系统软件及流程图

本系统软件是通过FPGA产生m序列的数字信号及其时钟信号,其系统软件发送数据部分如图10所示,接收数据并显示部分如图11所示。

图10主控FPGA发送数据原理图

图11主控FPGA接收数据原理图

m序列随机发生部分的软件设计能够使FGPA生成作为传输信号和噪声的两种m序列伪随机信号。

其流程图如图12所示。

信号处理部分的软件主要实现对信号提取位同步信号的功能以便使示波器能够正常显示对应眼图。

其流程图如13所示。

图12m序列随机信号发生部分软件实现流程图

图13信号处理部分流程图

五、系统测试与测试结果

5.1测试仪器

表1测试使用的仪器设备

序号

名称、型号、规格

数量

备注

出厂编号

1

CALTEK模拟示波器

1

40MHz示波器

01042060

2

函数信号发生器

1

南京新联电子设备公司

001398

3

数字万用表UT58E

1

UNI-T

30500306

4

INSTEK数字示波器

1

40MHz数字示波器

EH120202

5

AgilentU3606万用表

1

五位半万用表/直流电源

90006

5.2眼图测试方案

在用模拟示波器观察传输的数据信号时,使用被测系统的定时信号,m序列通过示波器外触发和时钟信号内同步对示波器的扫描进行控制,由于扫描周期此时恰为被测信号周期的整数倍,因此在示波器荧光屏上观察到的就是一个由多个随机符号波形共同形成的稳定眼图(显示的眼图见附表3)。

5.3测试结果及分析

5.3.1低通滤波器特性测量

测试方法:

选择不同的滤波器,改变输入频率,测试输出幅值;(实际波形见附表1)

测试条件:

输入幅值峰峰值为3.3V;

测试时间:

2013年7月31日19:

23。

表2三个低通滤波器的频率测量表

测试电路

测试频率

幅值

100kHz低通率滤波器

50KHz

3.24V

100KHz

2.04V

1MHz

40mV

200kHz低通率滤波器

100KHz

3.12V

200KHz

2.12V

2MHz

38mV

500kHz低通率滤波器

250KHz

3.20V

500kHz

2.24V

5MHz

400mV

5.3.2数字信号发生器数据率测量

测试方法:

通过按键控制使数字信号数据率以10kbps步进,使用数字示波器测试输出

信号数据率;(受干扰前后波形对比见附表2)

测试条件:

改变数据率从10kbps—100kbps步进;

测试时间:

2013年7月31日19:

40。

表3数字信号发生器数据率测量

数字信号设定数据率

实际数据率测量值

误差绝对值

输出信号幅值

输出信号类型

10kbps

10.0kbps

0

3.32V

TTL

20kbps

20.0kbps

0

3.31V

TTL

30kbps

30.0kbps

0

3.30V

TTL

40kbps

40.0kbps

0

3.29V

TTL

50kbps

50.1kbps

0.1

3.30V

TTL

60kbps

60.1kbps

0.1

3.28V

TTL

70kbps

70.2kbps

0.2

3.33V

TTL

80kbps

80.0kbps

0

3.32V

TTL

90kbps

90.3kbps

0.2

3.31V

TTL

100kbps

100.3kbps

0.3

3.31V

TTL

5.3.3增益可调电路特性测试

测试方法:

选择不同的频率值,调节滑动变阻器使增益倍数从0.2—4可调;

测试条件:

输入幅值峰峰值为3.3V;

测试时间:

2013年7月31日20:

02。

表4增益可调电路的通带增益

测试频率

调节倍数

输出幅值

100KHz

0.2

661mV

1

3.30V

2.8

9.24V

4

13.21V

200KHz

0.2

662mV

1

3.31V

2.8

9.25V

4

13.22V

500KHz

0.2

660mV

1

3.30V

2.8

9.22V

4

13.20V

测试结果分析:

经测试,本设计能够实现赛题要求,测量结果在误差允许范围之内。

综上所述,本设计达到设计要求。

六、总结

设计采用FPGA最小系统为控制核心,实现了一款简易数字信号传输性能分析仪的设计。

通过测试,系统不但完成了基本要求,也完成了发挥部分的一部分要求。

经过几天的努力实践,不断的测试,不断的改进电路和程序,我们最终圆满完成了设计任务。

在设计过程中,我们不仅仅使自身水平得到了检验,更重要的是学到很多课本上没有的知识,使自己得到了进一步的提高。

同时也特别感谢段老师和查老师的精心指导和同学的帮助和支持,使我们这次设计能够顺利完成。

参考文献

[1]曾凡泰,陈美金,《VHDL程序设计》,清华大大学学出版社,2001年第2版

[2]黄智伟,《全国大学生电子设计竞赛训练教程》,电子工业出版式社,2010年第2版

[3]熊睿佳,胡万利,《伪随机m序列特性及C语言实现》,工程地球物理学报,2011年2月第8卷第1期

[4]桂静宜,《有源低通滤波电路的设计与分析》,电子科技,2010年10月第23卷第10期

[5]全国大学生电子设计竞赛组委会,《2011年全国大学生电子设计竞赛获奖作品选编》,北京理工大学出版社,2012年8月

附录:

1、附图部分

附图1FPGA核心板原理图

附图2100KHz低通滤波器电路

附图3200KHz低通滤波器电路

附图4500KHz低通滤波器电路

附图5加法器电路图

附图6π型衰减器电路

附图7增益调节电路

附图8电源供电电路

附图9数字信号V1的m序列波形图和仿真图

附图10时钟信号V1_clock的波形图

附图11伪随机信号序列V3的波形图和仿真图

2、附表部分

附表1低通滤波器测试波形图对比表

截止频率

Fo/KHz

滤波后信号V2

干扰后信号V2a

100

200

500

附表2不同幅度干扰对波形影响图

截止频率Fo/KHz

100KHz

200KHz

500KHz

干扰很小

干扰较大

干扰很大

附表3眼图的显示

滤波

干扰前

干扰后

100

200

500

根据眼图分析数字信号传输性能:

1、通过比较各个眼图,从图中可以看出经过100KHz低通滤波器斜边的斜率最小,经过200KHz低通滤波器斜边的斜率居中,经过500KHz低通滤波器斜边的斜率最大。

由此可知通过500KHz的传输系统对抽样定时误差最灵敏,经过100KHz的传输系统对抽样定时误差最不灵敏;

2、当加入模拟噪声后三种系统上下阴影区的高度均增大,此时的信号失真量随之加大,它是噪声和码间串扰叠加的结果。

3、通过比较各个眼图,从图中可以看出经过100KHz低通滤波器眼图张开度最大,经过200KHz低通滤波器眼图张开度居中,经过500KHz低通滤波器眼图张开度最小。

由此可知当最佳取样时刻选在眼图张开最大的时刻时,通过100KHz的传输系统信噪比最大,经过500KHz的传输系统信噪比最小。

附表4加法器测试数据和波形图

V1

V2

Vo

波形图

f1=100KHz

Vp-p=3.3V

f2=10MHz

Vp-p=100mv

f1=100KHz

Vp-p=3.44V

f2=10MHz

Vp-p=1V

f1=100KHz

Vp-p=4.40V

f2=1MHz

Vp-p=1V

f1=100KHz

Vp-p=4.32V

f2=100KHz

Vp-p=3V

f1=100KHz

Vp-p=5.72V

f1=10KHz

Vp-p=3.3V

f2=10MHz

Vp-p=1.5V

f1=10KHz

Vp-p=3.78V

f2=1MHz

Vp-p=1.5V

f1=10KHz

Vp-p=4.2V

3、制作过程遇到的问题与解决方案

a.低通滤波器部分

在设计低通滤波器时我们采用的是一阶RC有源低通滤波器,但是滤波效果达不到预期效果,后来改用二阶低通滤波,但是两个电阻和两个电容值选择了一样的,滤波效果还是达不到效果,最终使用了滤波器设计软件并采用四阶低通滤波,特殊的电阻使用电位器调节得到,制作的低通滤波器效果很好,能很好的完成题目的要求。

b.加法器部分

加法器的设计电路图来自模电书上的电路,之前没有考虑到噪声信号是10MHz,选用的OP37芯片带宽不够,所以加法器得到的波形是不正确的,后来改用高带宽的THS3091运放芯片能很好的完成加法电路功能,而且效果非常好。

c.FPGA核心板部分

该系统需要输出10Kbps—100Kbps的步进数字信号,所以计算得知50.4MHz是所有信号的公倍数,所以需要FPGA通过倍频和分频得到50.4MHz的时钟,CycloneII器件不能得到超过50MHz的时钟信号,所以只能采用CycloneIV的FPGA器件,因为器件的限