数字电路基础D0402同步触发器.docx

《数字电路基础D0402同步触发器.docx》由会员分享,可在线阅读,更多相关《数字电路基础D0402同步触发器.docx(7页珍藏版)》请在冰豆网上搜索。

数字电路基础D0402同步触发器

数字电路基础_D04-02同步触发器

4.2同步触发器

在数字系统中,为使各部件协调动作,常常要求某些部件同时动作。

为此需要引入控制信号,只有控制信号到达时,这些部件的输出才按输入信号状态而改变,这种控制信号习惯上叫同步信号。

在数字电路的分析中,通常将控制信号叫做时钟脉冲,简称时钟,用CP(ClockPulse)表示。

实际使用中,时钟信号必须是高频率稳定度的信号。

能被时钟信号控制的触发器统称为钟控触发器,后面介绍的触发器均为钟控触发器。

与基本RS触发器那样的直接置位、复位触发器是有区别的。

本节介绍钟控触发器的两种基本形式:

同步RS触发器和同步D触发器。

4.2.1同步RS触发器

1.电路结构及工作原理

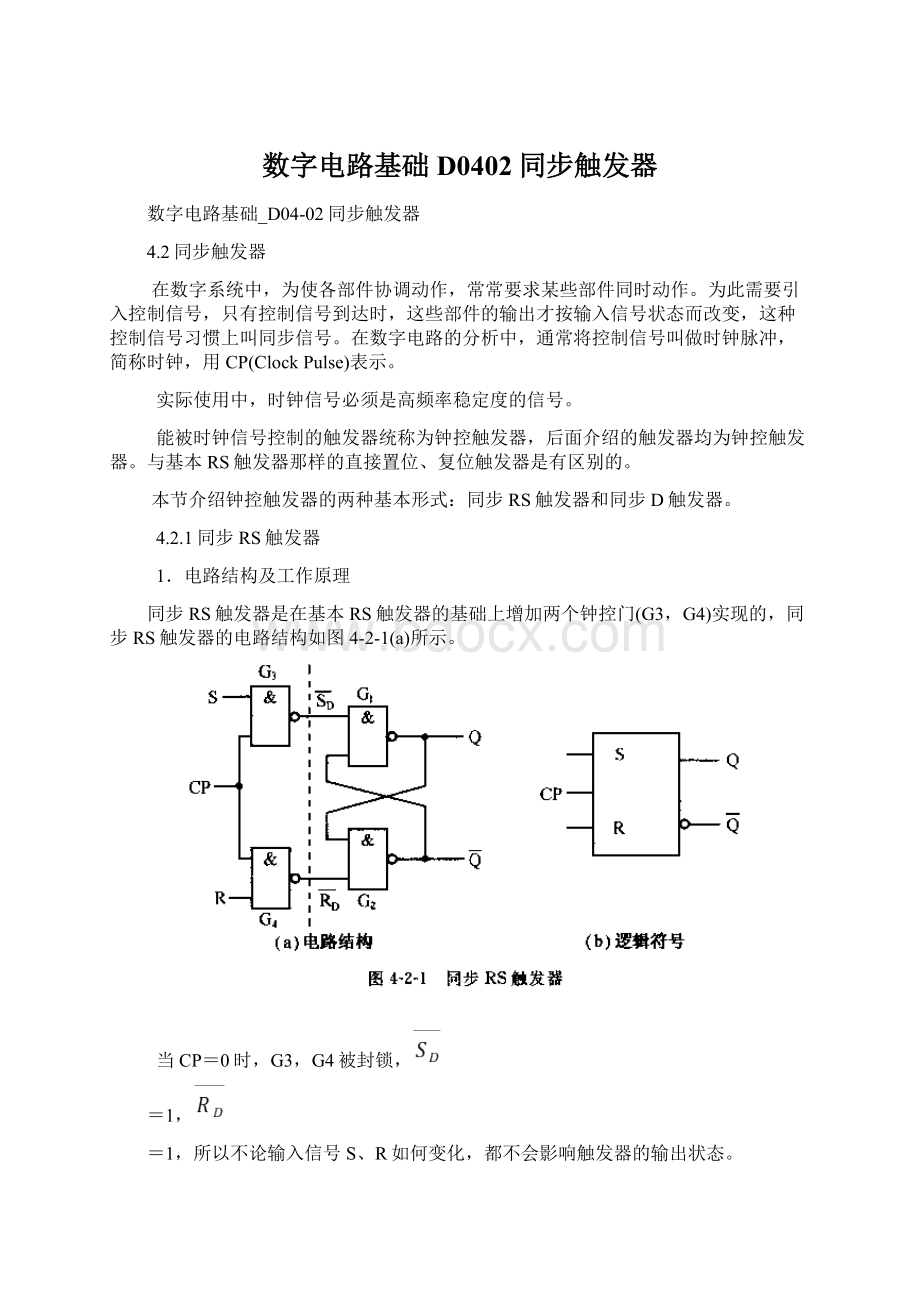

同步RS触发器是在基本RS触发器的基础上增加两个钟控门(G3,G4)实现的,同步RS触发器的电路结构如图4-2-1(a)所示。

当CP=0时,G3,G4被封锁,

=1,

=1,所以不论输入信号S、R如何变化,都不会影响触发器的输出状态。

当CP=l时,G3,G4开放,输入信号S、R通过门G3,G4作用到基本RS触发器的输入端,使触发器的输出状态随输入信号S、R的改变而变化。

可见同步RS触发器的翻转时刻由CP控制,CP上升沿至CP=1的整个期间可接收输入信号。

图4-2-1(b)所示是同步RS触发器的逻辑符号。

2.同步RS触发器逻辑功能的描述

(1)特性表及状态图

由于CP=l时,输入信号S、R分别与基本RS触发器的输入

,

反相,所以只要将表4-l-2的输入值取反,再加上钟控信号的作用,就可以得到同步RS触发器的特性表,如表4-2-l所示。

表中Qn是CP来到之前,触发器的原态;

是CP来到之后,触发器的次态;S、R是CP到达时,触发器的输入值。

且规定在CP=l期间S、R保持不变。

由表4-2-l可画出同步RS触发器的状态图,如图4-2-2所示。

(2)特性方程

同得到特性表的方法类似,在CP=1时,将输入信号

=

,

=

代人基本RS触发器的特性方程,就可以得到同步RS触发器的特性方程。

(4—2—1)

其中,SR=0为需满足的约束条件。

当然也可以由表4-2-l填得次态

“的卡诺图,进而得到同步RS触发器的特性方程。

(3)波形图

[例4—2—1]同步RS触发器;其输入CP、S、R的波形如图4-2-3所示,试画出输出Qn+1的波形。

设触发器的初始状态为“1”态,且忽略门的传输延迟时间。

解输出Q、Q非的波形如图4-2-3所示。

由图4-2-3可见同步RS触发器的翻转时刻由CP控制,CP上升沿至CP=l的整个期间可以接收输入信号,在CP=l期间,触发器的输出状态随输入信号的改变而变化。

即触发器的输出状态转换发生在CP=1期间,高电平起触发作用,故属于电平触发方式。

4.2.2同步D触发器

1.电路结构

为了从根本上避免同步,RS触发器的输入S、R同时为“l”的情况出现,可在同步RS触发器的输入S和R之间接一非门,信号只从S端输入,并改称S端为D端,如图4-2-4(a)所示。

这种单端输入的触发器称为同步D触发器(或称D锁存器)。

它的逻辑符号如图4-2-4(b)所示。

2.同步D触发器逻辑功能的描述

(1)特性表及状态图

由同步D触发器电路结构可知:

CP=0时,触发器保持现态不变。

CP=1时,若D=l,则Qn+1=1;若D=0,则Qn+1=0。

同步D触发器的特性表如表4-2-2所示。

对同步D触发器来说,CP=1时,将输人数据存人触发器;CP=0时,保持该数据不变。

只有下一个CP来到时,才能改变原存数据。

它也要求CP=l时D保持不变。

由表4-2-2可画出同步D触发器的状态图,如图4-2-5所示。

(2)特性方程

由特性表可以直接列出同步D触发器的特性方程。

Qn+1=D(4-2-2)

(3)波形图

[例4-2-2]同步D触发器,其输入CP、D的波形如图4-2—6所示,试画出输出Q的波形。

设触发器的初始状态为“0”态,且忽略门的传输延迟时间。

解:

输出Q的波形如图4-2-6所示。

由图可见,同步D触发器的翻转时刻由CP控制,CP上升沿至CP=l的整个期间可接收输入信号。

在CP=l期间,触发器的输出状态随输入信号的改变而变化。

即触发器的输出状态转换发生在CP=1期间,高电平起触发作用,故也属于电平触发方式。

4.2.3同步触发器的空翻现象

上述同步触发器在CP高电平期间,触发器都可以接收输入信号而翻转。

因此,同步触发器也称为电平触发型触发器。

这种触发器在CP=1期间,如果输入信号发生多次变化,输出状态也会发生多次翻转,如图4-2-7所示。

如果窄的正脉冲是干扰,就会使输出端作出错误的翻转。

这种在CP=1期间,因输入信号发生变化而引起输出状态的翻转,称为触发器的空翻。

由于空翻问题,同步RS触发器很难在实际中使用,但可用来构成主从式触发器等等。

同步D触发器只能用于数据寄存,而不能实现记数、移存等重要功能。

为了克服触发器的空翻现象,又产生了不同电路结构形式的触发器,如主从触发器、边沿触发器等等。