VHDL程序集锦.docx

《VHDL程序集锦.docx》由会员分享,可在线阅读,更多相关《VHDL程序集锦.docx(65页珍藏版)》请在冰豆网上搜索。

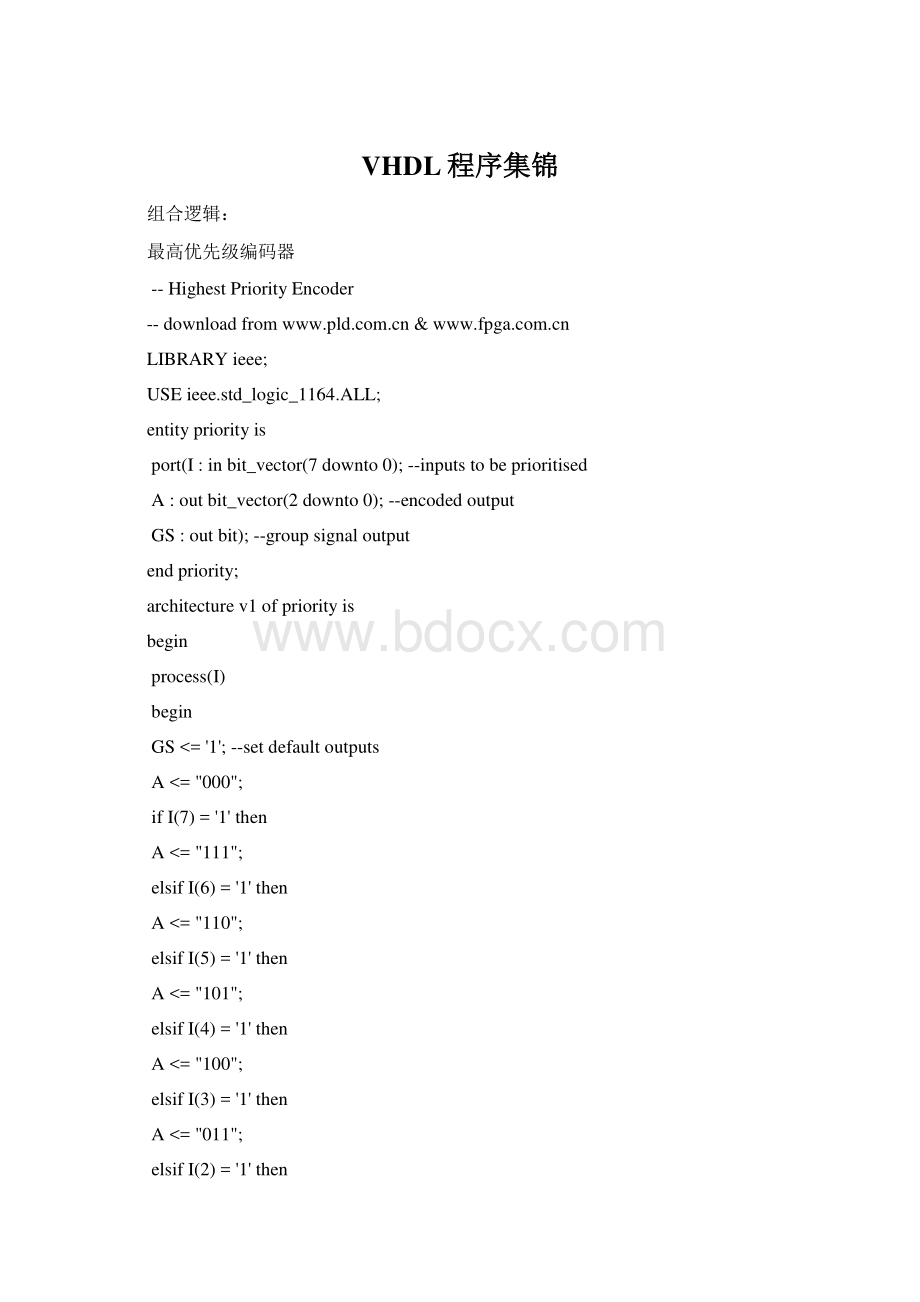

VHDL程序集锦程序集锦组合逻辑:

最高优先级编码器-HighestPriorityEncoder-downloadfrom&LIBRARYieee;USEieee.std_logic_1164.ALL;entitypriorityisport(I:

inbit_vector(7downto0);-inputstobeprioritisedA:

outbit_vector(2downto0);-encodedoutputGS:

outbit);-groupsignaloutputendpriority;architecturev1ofpriorityisbeginprocess(I)beginGS=1;-setdefaultoutputsA=000;ifI(7)=1thenA=111;elsifI(6)=1thenA=110;elsifI(5)=1thenA=101;elsifI(4)=1thenA=100;elsifI(3)=1thenA=011;elsifI

(2)=1thenA=010;elsifI

(1)=1thenA=001;elsifI(0)=1thenA=000;elseGS=0;endif;endprocess;endv1;8位相等比较器-8-bitIdentityComparator-uses1993stdVHDL-downloadfrom&libraryIEEE;useIEEE.Std_logic_1164.all;entityHCT688isport(Q,P:

instd_logic_vector(7downto0);GBAR:

instd_logic;PEQ:

outstd_logic);endHCT688;architectureVER1ofHCT688isbeginPEQ=0when(To_X01(P)=To_X01(Q)and(GBAR=0)else1;endVER1;三人表决器(三种不同的描述方式)-Three-inputMajorityVoter-Theentitydeclarationisfollowedbythreealternativearchitectureswhichachievethesamefunctionalityindifferentways.-downloadfrom:

&ENTITYmajISPORT(a,b,c:

INBIT;m:

OUTBIT);ENDmaj;-DataflowstylearchitectureARCHITECTUREconcurrentOFmajISBEGIN-selectedsignalassignmentstatement(concurrent)WITHa&b&cSELECTm=1WHEN110|101|011|111,0WHENOTHERS;ENDconcurrent;-StructuralstylearchitectureARCHITECTUREstructureOFmajIS-declarecomponentsusedinarchitectureCOMPONENTand2PORT(in1,in2:

INBIT;out1:

OUTBIT);ENDCOMPONENT;COMPONENTor3PORT(in1,in2,in3:

INBIT;out1:

OUTBIT);ENDCOMPONENT;-declarelocalsignalsSIGNALw1,w2,w3:

BIT;BEGIN-componentinstantiationstatements.-portsofcomponentaremappedtosignals-withinarchitecturebyposition.gate1:

and2PORTMAP(a,b,w1);gate2:

and2PORTMAP(b,c,w2);gate3:

and2PORTMAP(a,c,w3);gate4:

or3PORTMAP(w1,w2,w3,m);ENDstructure;-Behaviouralstylearchitectureusingalook-uptableARCHITECTUREusing_tableOFmajISBEGINPROCESS(a,b,c)CONSTANTlookuptable:

BIT_VECTOR(0TO7):

=00010111;VARIABLEindex:

NATURAL;BEGINindex:

=0;-indexmustbeclearedeachtimeprocessexecutesIFa=1THENindex:

=index+1;ENDIF;IFb=1THENindex:

=index+2;ENDIF;IFc=1THENindex:

=index+4;ENDIF;m=lookuptable(index);ENDPROCESS;ENDusing_table;加法器描述-AVarietyofAdderStyles-downloadfrom:

&-Single-bitadder-libraryIEEE;useIEEE.std_logic_1164.all;entityadderisport(a:

instd_logic;b:

instd_logic;cin:

instd_logic;sum:

outstd_logic;cout:

outstd_logic);endadder;-descriptionofadderusingconcurrentsignalassignmentsarchitecturertlofadderisbeginsum=(axorb)xorcin;couta,in2=b,out1=xor1_out);xor2:

xorgportmap(in1=xor1_out,in2=cin,out1=sum);and1:

andgportmap(in1=a,in2=b,out1=and1_out);or1:

orgportmap(in1=a,in2=b,out1=or1_out);and2:

andgportmap(in1=cin,in2=or1_out,out1=and2_out);or2:

orgportmap(in1=and1_out,in2=and2_out,out1=cout);endstructural;-N-bitadder-ThewidthoftheadderisdeterminedbygenericN-libraryIEEE;useIEEE.std_logic_1164.all;entityadderNisgeneric(N:

integer:

=16);port(a:

instd_logic_vector(Ndownto1);b:

instd_logic_vector(Ndownto1);cin:

instd_logic;sum:

outstd_logic_vector(Ndownto1);cout:

outstd_logic);endadderN;-structuralimplementationoftheN-bitadderarchitecturestructuralofadderNiscomponentadderport(a:

instd_logic;b:

instd_logic;cin:

instd_logic;sum:

outstd_logic;cout:

outstd_logic);endcomponent;signalcarry:

std_logic_vector(0toN);begincarry(0)=cin;couta(I),b=b(I),cin=carry(I-1),sum=sum(I),cout=carry(I);endgenerate;endstructural;-behavioralimplementationoftheN-bitadderarchitecturebehavioralofadderNisbeginp1:

process(a,b,cin)variablevsum:

std_logic_vector(Ndownto1);variablecarry:

std_logic;begincarry:

=cin;foriin1toNloopvsum(i):

=(a(i)xorb(i)xorcarry;carry:

=(a(i)andb(i)or(carryand(a(i)orb(i);endloop;sum=vsum;cout=carry;endprocessp1;endbehavioral;8位总线收发器:

74245(注2)-OctalBusTransceiver-ThisexampleshowstheuseofthehighimpedanceliteralZprovidedbystd_logic.-Theaggregate(others=Z)meansallofthebitsofBmustbeforcedtoZ.-PortsAandBmustberesolvedforthismodeltoworkcorrectly(hencestd_logicratherthanstd_ulogic).-downloadfrom:

&libraryIEEE;useIEEE.Std_logic_1164.all;entityHCT245isport(A,B:

inoutstd_logic_vector(7downto0);DIR,GBAR:

instd_logic);endHCT245;architectureVER1ofHCT245isbeginAZ);BZ);endVER1;地址译码(form68008)-M68008AddressDecoder-Addressdecoderforthem68008-asbarmustbe0toenableanyoutput-csbar(0):

X00000toX01FFF-csbar

(1):

X40000toX43FFF-csbar

(2):

X08000toX0AFFF-csbar(3):

XE0000toXE01FF-downloadfrom&libraryieee;useieee.std_logic_1164.all;entityaddrdecisport(asbar:

instd_logic;address:

instd_logic_vector(19downto0);csbar:

outstd_logic_vector(3downto0);endentityaddrdec;architecturev1ofaddrdecisbegincsbar(0)=X00000)and(address=X01FFF)else1;csbar

(1)=X40000)and(address=X43FFF)else1;csbar

(2)=X08000)and(address=X0AFFF)else1;csbar(3)=XE0000)and(address=XE01FF)else1;endarchitecturev1;多路选择器(使用select语句)-Multiplexer16-to-4usingif-then-elsif-elseStatement-downloadfrom&libraryieee;useieee.std_logic_1164.all;entitymuxisport(a,b,c,d:

instd_logic_vector(3downto0);s:

instd_logic_vector(1downto0);x:

outstd_logic_vector(3downto0);endmux;architecturearchmuxofmuxisbeginmux4_1:

process(a,b,c,d)beginifs=00thenx=a;elsifs=01thenx=b;elsifs=10thenx=c;elsex=d;endif;endprocessmux4_1;endarchmux;LED七段译码-DESCRIPTION:

BINtosevensegmentsconverter-segmentencoding-a-+-+-f|b-+-+-g-e|c-+-+-d-Enable(EN)active:

high-Outputs(data_out)active:

low-Downloadfrom:

http:

/-libraryIEEE;useIEEE.std_logic_1164.all;entitybin27segisport(data_in:

instd_logic_vector(3downto0);EN:

instd_logic;data_out:

outstd_logic_vector(6downto0);endentity;architecturebin27seg_archofbin27segisbeginprocess(data_in,EN)begindata_out1);ifEN=1thencasedata_iniswhen0000=data_outdata_outdata_outdata_outdata_outdata_outdata_outdata_outdata_outdata_outdata_outdata_outdata_outdata_outdata_outdata_outNULL;endcase;endif;endprocess;endarchitecture;多路选择器(使用ifelse语句)-Multiplexer16-to-4usingif-then-elsif-elseStatement-downloadfrom&libraryieee;useieee.std_logic_1164.all;entitymuxisport(a,b,c,d:

instd_logic_vector(3downto0);s:

instd_logic_vector(1downto0);x:

outstd_logic_vector(3downto0);endmux;architecturearchmuxofmuxisbeginmux4_1:

process(a,b,c,d)beginifs=00thenx=a;elsifs=01thenx=b;elsifs=10thenx=c;elsex=d;endif;endprocessmux4_1;endarchmux;双24译码器:

74139-Dual2-to-4Decoder-Asetofconditionalsignalassignmentsmodeladual2-to-4decoder-uses1993stdVHDL-downloadfrom:

&libraryIEEE;useIEEE.Std_logic_1164.all;entityHCT139isport(A2,B2,G2BAR,A1,B1,G1BAR:

instd_logic;Y20,Y21,Y22,Y23,Y10,Y11,Y12,Y13:

outstd_logic);endHCT139;architectureVER1ofHCT139isbeginY10=0when(B1=0)and(A1=0)and(G1BAR=0)else1;Y11=0when(B1=0)and(A1=1)and(G1BAR=0)else1;Y12=0when(B1=1)and(A1=0)and(G1BAR=0)else1;Y13=0when(B1=1)and(A1=1)and(G1BAR=0)else1;Y20=0when(B2=0)and(A2=0)and(G2BAR=0)else1;Y21=0when(B2=0)and(A2=1)and(G2BAR=0)else1;Y22=0when(B2=1)and(A2=0)and(G2BAR=0)else1;Y23=0when(B2=1)and(A2=1)and(G2BAR=0)else1;endVER1多路选择器(使用whenelse语句)-Multiplexer16-to-4usingif-then-elsif-elseStatement-downloadfrom&libraryieee;useieee.std_logic_1164.all;entitymuxisport(a,b,c,d:

instd_logic_vector(3downto0);s:

instd_logic_vector(1downto0);x:

outstd_logic_vector(3downto0);endmux;architecturearchmuxofmuxisbeginmux4_1:

process(a,b,c,d)beginifs=00thenx=a;elsifs=01thenx=b;elsifs=10thenx=c;elsex=d;endif;endprocessmux4_1;endarchmux;二进制到BCD码转换-DESCRIPTION:

BintoBcdconverter-Input(data_in)width:

4-Output(data_out)width:

8-Enable(EN)active:

high-Downloadfrom:

http:

/-libraryIEEE;useIEEE.std_logic_1164.all;entitybin2bcdisport(data_in:

instd_logic_vector(3downto0);EN:

instd_logic;data_out:

outstd_logic_vector(7downto0);endentity;architecturebin2bcdofbin2bcdisbeginprocess(data_in,EN)variabledata_in_TEMP:

std_logic_vector(2downto0);begindata_in_TEMP:

=data_in(3downto1);data_out0);ifEN=1thencasedata_in_TEMPiswhen000=data_out(7downto1)data_out(7downto1)data_out(7downto1)data_out(7downto1)data_out(7downto1)data_out(7downto1)data_out(7downto1)data_out(7downto1)data_out0);endcase;data_out(0)=data_in(0);endif;endprocess;endarchitecture;多路选择器(使用case语句)-Multiplexer16-to-4usingif-then-elsif-elseStatement-downloadfrom&libraryieee;useieee.std_logic_1164.all;entitymuxisport(a,b,c,d:

instd_logic_vector(3downto0);s:

instd_logic_vector(1downto0);x:

outstd_logic_vector(3downto0);endmux;architecturearchmuxofmuxisbeginmux4_1:

process(a,b,c,d)beginifs=00thenx=a;elsifs=01thenx=b;elsifs=10thenx=c;elsex=d;endif;endprocessmux4_1;endarchmux;二进制到格雷码转换-DESCRIPTION:

Bintograyconverter-Input(DATA_IN)width:

4-Enable(EN)active:

high-Downloadfrom:

http:

/-libraryIEEE;useIEEE.std_logic_1164.all;entityBIN2GARYisport(DATA_IN:

instd_logic_vector(3downto0);EN:

instd_logic;DATA_OUT:

outstd_logic_vector(3downto0);endentity;architecturebin2gary_archofBIN2GARYisbeginDATA_OUT(0)=(DATA_IN(0)xorDATA_IN

(1)andEN;DATA_OUT

(1)=(DATA_IN

(1)xorDATA_IN

(2)andEN;DATA_OUT

(2)=(DATA_IN

(2)xorDATA_IN(3)andEN;DATA_OUT(3)=DATA_IN(3)andEN;endarchitecture;双向总线(注2)VHDL:

BidirectionalBusdownloadfrom:

http:

/bidir.vhd(Tri-statebusimplementation)LIBRARYieee;USEieee.std_logic_1164.ALL;ENTITYbidirISPORT(bidir:

INOUTSTD_LOGIC_VECTOR(7DOWNTO0);oe,clk:

INSTD_LOGIC;inp:

INSTD_LOGIC_VECTOR(7DOWNTO0);outp:

OUTSTD_LOGIC_VECTOR(7DOWNTO0);ENDbidir;ARCHITECTUREcpldOFbidirISSIGNALa:

STD_LOGIC_VECTOR(7DOWNTO0);-DFFthatstores-valuefrominput.SIGNALb:

STD_LOGIC_VECTOR(7DOWNTO0);-DFFthatstoresBEGIN-feedbackvalue.PROCESS(clk)BEGINIFclk=1ANDclkEVENTTHEN-Createstheflipflopsa=inp;outp=b;ENDIF;ENDPROCESS;PROCESS(oe,bidir)-Behavioralrepresentation