QuartusII110学习与应用.docx

《QuartusII110学习与应用.docx》由会员分享,可在线阅读,更多相关《QuartusII110学习与应用.docx(13页珍藏版)》请在冰豆网上搜索。

QuartusII110学习与应用

◆菜单栏中,

ØAssignments(资源分配):

主要是对工程参数进行配置,如引脚分配、时序约束、参数设置等;

ØProcess(操作):

主要对当前工程执行各种设计流程,如综合、布局、布线、时序分析等。

ØTool:

用来调用Quaruts中集成的一些工具,如MegaWizardPlug-InManger(用来生产IP核和宏单元模块)、RTLView、Programmer等。

EDA工具应用

◆建立项目文件:

1.创建工程:

在新建工程时,一定要注意顶层文件名与module别名一致,否则编译会出现顶层文件未定义的错误。

当顶层文件包含有其他模块时候,需要先编译顶层文件中的各个模块,最后编译顶层模块。

就是说,只要建工程是命名的顶层文件名和实际的顶层文件模块名一样,就可以先编译工程中的其他模块而不会报上面的错误!

还有,一旦创建工程以后,就不要再更改工作所在文件夹名称,否则下次就会打不开此工程。

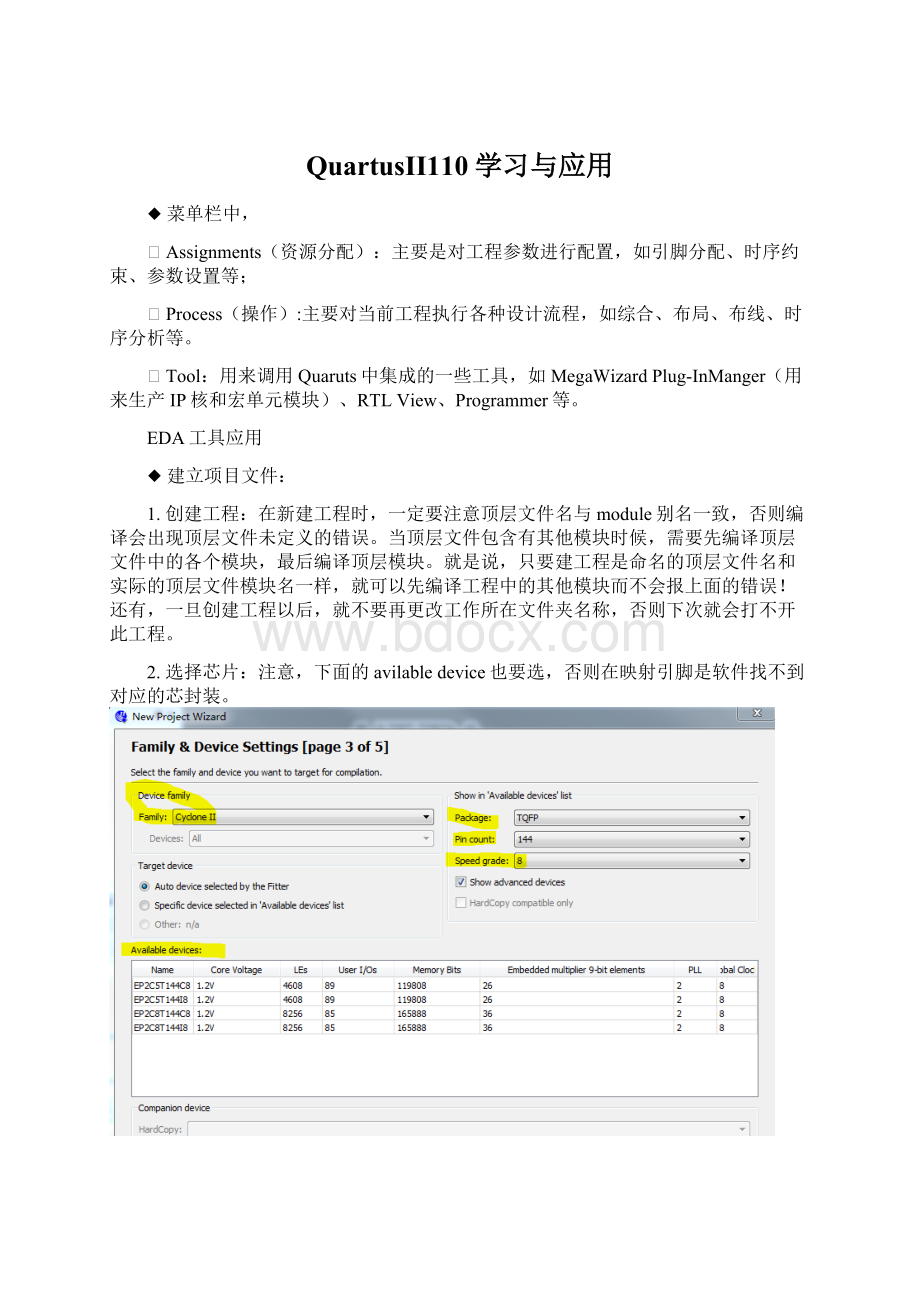

2.选择芯片:

注意,下面的avilabledevice也要选,否则在映射引脚是软件找不到对应的芯封装。

3.工具设置:

,(如果选择默认设置的话,就是使用Quartus自带的设计工具,当然可以选择第三方软件)

编辑和设计输入:

同样可以选择原理图输入、HDL输入、状态图输入以及混合输入等方式。

◆设计输入:

1.原理图输入:

2.HDL输入:

3.状态图输入:

◆逻辑编译检查:

:

◆软件仿真:

(Quartus9.1以后不再支持建立波形文件,用户需配合使用Modelsim进行仿真)。

Ø关于仿真:

(对于硬件描述语言对现代数字逻辑系统的描述层次,不同层次的仿真个有特点)

1.系统级:

称为ESL级,即从系统角度进行描述而忽略电路的实际构成。

2.行为级:

从电路的工作行为、功能的实现出发而不考虑具体电路构成的描述。

3.RTL级:

从信号的传输、寄存器的设置角度描述。

4.门级:

考虑最基本门级元件构成系统描述。

5.开关级(管子级):

从基础的MMOS开关、晶体管、电阻对电路进行描述。

·

6.物理级:

从基本电子物理模型,如载流子迁移或能级模型角度的描述(只在模拟电路建模是才用到)

ØQuartus9.1之前(利用Quartus中的门级仿真器,主要依据是基于HDL、模块原理图、状态机经由综合与适配的网表格式文件对应的仿真文件,仿真类型包括时序仿真和功能仿真。

):

1.建立仿真波形文件

2.设置仿真时间区域

3.添加仿真信号

4.编辑仿真信号

5.时序仿真

6.功能仿真

ØModelsim(又称之为行为仿真,是一种编译型仿真器,即直接对HDL源代码进行仿真,也就是直接针对未经综合的仿真验证能更直接、更迅速、更完整、更高效和更加符合一般意义上地了解HDL代码描述的电路行为,此类仿真同样能实现时序仿真和功能仿真):

1.建立仿真工程项目:

2.编译仿真文件:

编译前:

右击选CompileALL编译后:

3.装载仿真模块和仿真库:

,右击图示编译后生成的实体,选择Simulatewithoutoptimization(优化)启动仿真。

4.执行仿真:

a)选中clk信号,选主菜单下objects中的clock进行时钟信号设置。

b)选中其它信号,选主菜单下objects中的force进行Value设置。

c)在objects窗口中:

,右击,选ADD下选ToWave下SignalsinDesign打开Wave波形窗口:

d)在命令栏中输入run5000

,(run必须小些,后面的仿真时间与run空格隔开,没runx一次都是在原来的基础上添加xns的仿真时间)

◆全程综合编译:

(检错,逻辑综合,机构综合,输出配置,时序分析,查看报表)

1.全程编译前约束项目的设置:

(选芯片,器件工作方式,配置或编程方式,器件端口状态)

a)点击assignments选device后可以对芯片进行重新选择:

b)选择配置器件的工作方式:

c)选择配置器件和编译方式:

d)引脚映射:

,在选择引脚的时候,可以从第一个引脚开始由上而下进行,双击第一个引脚,在列表里面选好引脚,然后回车,注意是用回车,然后删掉PIN后面的数字,然后对照电路板原理图手动修改引脚编号,重复此过程修改后面的引脚编号,数度要快些。

另外,不同颜色标识表明属于不同的IO块。

e)选择目标器件引脚端口状态:

将不使用的引脚设置为输入状态(即高阻态):

2.再次编译,这次编译不仅仅是逻辑检查,还添加了上述约束项目的:

◆RTL图观察器使用:

:

1.Tools下面NetlistViewers下拉菜单中三个选项:

RTLViewer;TechnologyMapViewer;StateMachineViewer;点击相应项目可以观察相应的图:

(双击该模块,可逐层了解各层次电路结构)

也可以通过上面工具栏查看各层次电路结构:

2.对于较为复杂的RTL电路图,可以右击该模块,在弹出的菜单中选择来宁波七:

Filter下面sources或destinations命令,由此产生相应的简化电路。

◆下载:

,或者Tool下面的programmer。

Ø

Ø

ØJTAG下载说明:

1.选择下载模式:

2.添加硬件:

,

3.添加文件:

AddFile:

,JTAG下载的是.SOF文件。

,这里打勾说明添加文件正确。

ØAS下载说明:

1.File下面ComvertProgrammingFiles···

2.选择器件:

VHDL编程心得:

Ø关于端口说明:

1.标点符号要在英文半角状态下输入。

2.顶层模块端口声明一定要和最后端口映射一一对应而且位宽也要一一对应:

:

外部端口

内部连线,线名自定。

3.关于位宽选取,可以批量取:

Q28<=Q_28;也可以单独取:

Q8<=(Q(27),Q(26),Q(25),Q(24),Q(23),Q(22),Q(21),Q(20));

Ø关于进程:

进程(Process)是VHDL中最为重要的部分,大部分设计都会用到Process结构,因此掌握

Process的使用显得尤为重要。

以下是初学和使用Process经常会出错的例子。

1.多余时钟的引入

在设计时往往会遇到这种情况,需要对外部某个输入信号进行判断,当其出现上跳或下跳沿

时,执行相应的操作,而该信号不像正常时钟那样具有固定占空比和周期,而是很随机,需

要程序设计判断其上跳沿出现与否。

这时,很容易写出如下程序:

①process(Ctl_a)--Ctl_a即为该输入信号

②begin

③ifCtl_a’eventandCtl_a=’1’then

④……;--执行相应操作

⑤endif;

⑥endprocess;

由于出现第③行这类语句,综合工具自动默认Ctl_a为时钟,某些FPGA更会强行将该输入

约束到时钟引脚上。

而设计者的初衷只是想将其作为下位机的状态输入以进行判断。

上面的

程序容易造成多时钟现象,增加设计的难度。

解决的办法可以如下,将Ctl_a增加一级状态

Ctl_areg寄存,通过对Ctl_a和Ctl_areg状态判断上跳与否,改正程序如下:

①process(clk)

②begin

③ifclk’eventandclk=’1’then

④Ctl_areg<=Ctl_a;--产生相邻状态

⑤ifCtl_areg=’0’andCtl_a=’1’then--上跳判断

⑥……;--执行相应操作

⑦endif;

⑧endif;

⑨endprocess;

程序中第④行用以产生两个相邻状态,第⑤行对前后状态进行判断是否有上跳现象发生。

其

中,需注意的是clk的时钟频率应明显快于Ctl_a信号的变化频率,以保证正确采样。

2.输出多驱动

误用Process经常会引起输出多驱动源的发生,即在两个以上的进程内对同一信号赋值操作。

以下程序就出现了这类情况:

⑴Proc_a:

process(clk)

⑵begin

⑶ifclk’eventandclk=’1’then

⑷Dout<=Din_A;

⑸endif

⑹endprocess;;

⑺

⑻Proc_b:

process(sel_en)

⑼begin

⑽ifsel_en=’1’then

⑾Dout<=Din_B;

⑿endif;

⒀endprocess;

进程Proc_a和Proc_b中都出现了对Dout的赋值语句,设计者原本的想法是,只要合理控

制好clk和sel_en输入,使其不发生冲突,即clk上升沿时sel_en不为’1’;sel_en为’1’

时,不出现clk的上升沿,这样Proc_a,Proc_b两个进程就不会发生冲突。

但综合时,综合

工具会将所有可能情况全部罗列进去,包括第⑶行和第⑽行同时成立的情况,此时对于Dout

就有Din_A和Din_B两个输入驱动,Dout不知接收哪一个,因此该程序无法综合,改正的

方法是只要将两个进程合并成一个即可。

由于进程在VHDL中的重要性,对此专门做了一个总结如下:

(1)一个进程中不允许出现两个时钟沿触发,(Xilinx公司CoolRunner系列CPLD支持单

个时双钟的双触发沿除外)

(2)对同一信号赋值的语句应出现在单个进程内,不要在时钟沿之后加上else语句,如

ifclk’eventandclk=’1’then-else…的结构,现有综合工具支持不了这种特殊的触发

器结构

(3)当出现多层IF语句嵌套时,最好采用CASE语句替代,一是减少多层嵌套带来的延时,

二来可以增强程序的可读性

(4)顺序语句如IF语句、CASE语句、LOOP语句、变量赋值语句等必须出现在进程、函

数或子程序内部,而不能单独出现在进程之外

(5)进程内部是顺序执行的,进程之间是并行运行的;VHDL中的所有并行语句都可以理

解为特殊的进程,只是不以Process结构出现,其输入信号和判断信号就是隐含的敏感表