数字逻辑与数字集成电路实验一.docx

《数字逻辑与数字集成电路实验一.docx》由会员分享,可在线阅读,更多相关《数字逻辑与数字集成电路实验一.docx(9页珍藏版)》请在冰豆网上搜索。

数字逻辑与数字集成电路实验一

实验一 基本逻辑门逻辑功能测试及应用

一、实验目的

1、掌握基本逻辑门的功能及验证方法。

2、学习TTL基本门电路的实际应用。

3、掌握逻辑门多余输入端的处理方法。

二、实验原理

数字电路中,最基本的逻辑门可归结为与门、或门和非门。

实际应用时,它们可以独立使用,但用的更多的是经过逻辑组合组成的复合门电路。

目前广泛使用的门电路有TTL门电路。

TTL门电路是数字集成电路中应用最广泛的,由于其输入端和输出端的结构形式都采用了半导体三极管,所以一般称它为晶体管-晶体管逻辑电路,或称为TTL电路。

这种电路的电源电压为+5V,高电平典型值为3.6V(≥2.4V合格);低电平典型值为0.3V(≤0.45合格)。

常见的复合门有与非门、或非门、与或非门和异或门。

有时门电路的输入端多余无用,因为对TTL电路来说,悬空相当于“1”,所以对不同的逻辑门,其多余输入端处理方法不同。

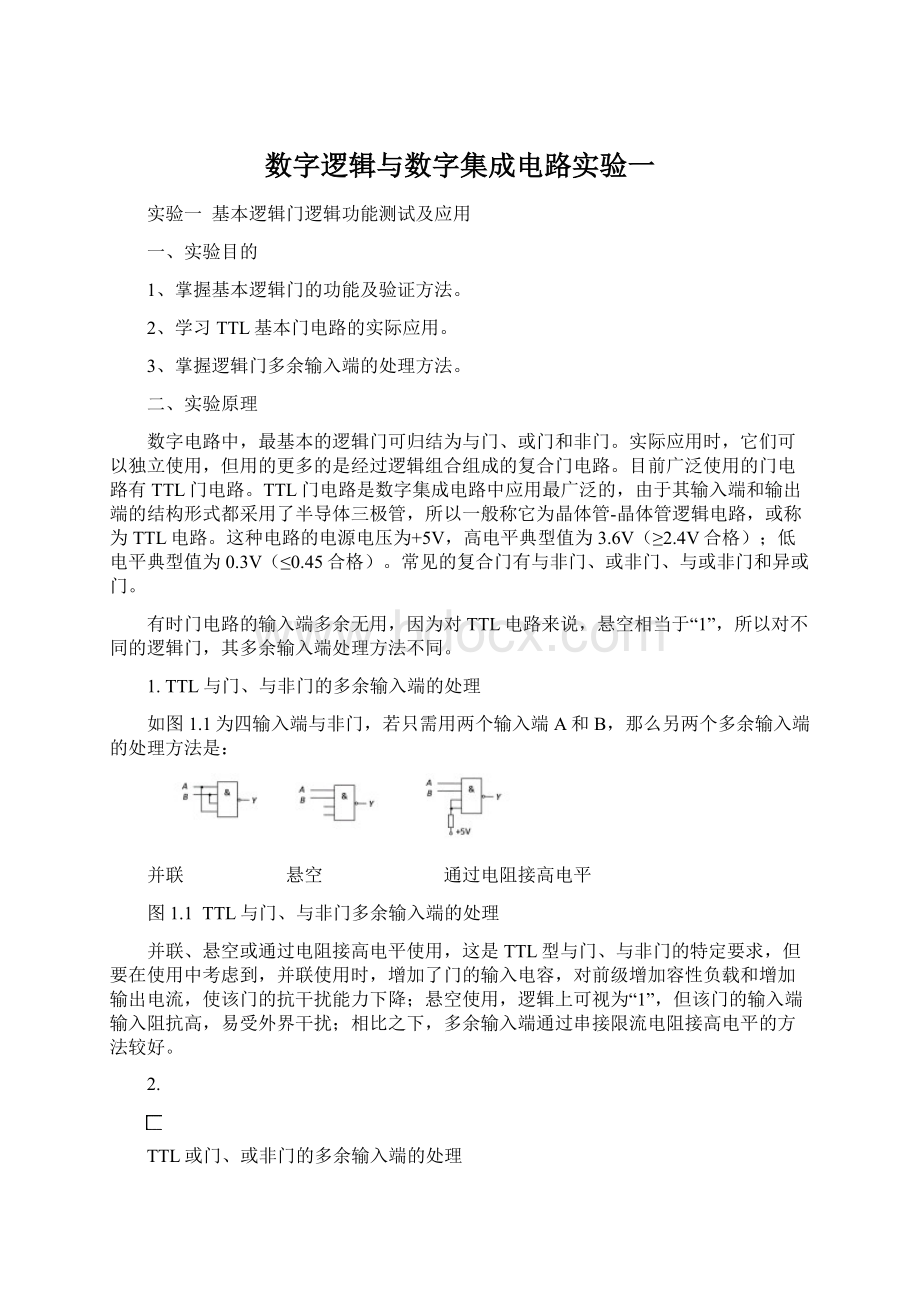

1.TTL与门、与非门的多余输入端的处理

如图1.1为四输入端与非门,若只需用两个输入端A和B,那么另两个多余输入端的处理方法是:

并联 悬空 通过电阻接高电平

图1.1 TTL与门、与非门多余输入端的处理

并联、悬空或通过电阻接高电平使用,这是TTL型与门、与非门的特定要求,但要在使用中考虑到,并联使用时,增加了门的输入电容,对前级增加容性负载和增加输出电流,使该门的抗干扰能力下降;悬空使用,逻辑上可视为“1”,但该门的输入端输入阻抗高,易受外界干扰;相比之下,多余输入端通过串接限流电阻接高电平的方法较好。

2.

TTL或门、或非门的多余输入端的处理

如图1.2为四输入端或非门,若只需用两个输入端A和B,那么另两个多余输入端的处理方法是:

并联、接低电平或接地。

并联 接低电平或接地

图1.2 TTL或门、或非门多余输入端的处理

3.异或门的输入端处理

异或门是由基本逻辑门组合成的复合门电路。

如图1.3为二输入端异或门,一输入端为A,若另一输入端接低电平,则输出仍为A;若另一输入端接高电平,则输出为A,此时的异或门称为可控反相器。

图1.3 异或门的输入端处理

在门电路的应用中,常用到把它们“封锁”的概念。

如果把与非门的任一输入端接地,则该与非门被封锁;如果把或非门的任一输入端接高电平,则该或非门被封锁。

由于TTL电路具有比较高的速度,比较强的抗干扰能力和足够大的输出幅度,在加上带负载能力比较强,因此在工业控制中得到了最广泛的应用,但由于TTL电路的功耗较大,目前还不适合作大规模集成电路。

三、实验仪器与器材

1、THD-2型数字电路实验箱

2、器材:

74LS00 四-2输入与非门×2

74LS20 二-4输入与非门 ×1

74LS54 四-2-3-3-2输入与或非门 ×1

74LS86 四-2输入异或门×1

四、实验内容与步骤

1、TTL与非门的逻辑功能及应用

芯片的引脚号查法是面对芯片有字的正面,从缺口处的下方(左下角),逆时针从1数起。

芯片要能工作,必须接电源和地。

本实验所用与非门集成芯片为74LS00四-二输入与非门,其引脚排列如图1.4所示。

图1.4 74LS00引脚排列

(1)测试74LS00四-2输入与非门的逻辑功能

选中74LS00一个与非门,将其输入端A和B分别接至电平输出器插孔,由电平输出控制开关控制所需电平值,扳动开关给出四种组合输入。

将输出端接至发光二极管的输入插孔,并通过发光二极管的亮和灭来观察门的输出状态。

如图1.5所示,其逻辑函数式为:

,将观测结果填入表1.1中。

输入

输出

AB

Y

10

01

10

11

表1.1与非门逻辑功能测试表

图1.5 与非门逻辑功能测试图

(2)用74LS00实现或逻辑:

,写出转换过程逻辑函数式,画出标明引脚的逻辑电路图,测试其逻辑功能,将观测结果填入表1.2中。

表1.2或逻辑功能测试表

输入

输出

AB

Y

00

01

10

11

解:

(3)用74LS00实现表1.3所示的逻辑函数。

写出设计函数式,画出标明引脚的逻辑电路图,并验证之。

输入

输出

输入

输出

ABC

Y

ABC

Y

000

001

010

011

0

0

0

1

100

101

110

111

0

0

1

1

表1.3数据表

解:

2、TTL与或非门的逻辑功能及应用

(1)测试74LS54四-2-3-3-2输入与或非门的逻辑功能,74LS54引脚排列如图1.6所示。

图1.6 74LS54引脚排列

逻辑表达式为:

现要求测试的逻辑函数式为:

。

接线如图1.7所示,用开关改变输入变量A、B、C、D的状态,给出十六种组合输入,通过发光二极管观测输出端Y的状态,将观测结果填入表1.4中。

表1.4与或非逻辑功能测试表

输入

输出

输入

输出

ABCD

Y

ABCD

Y

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

图1.7与或非门逻辑功能测试图

3、TTL异或门的逻辑功能及应用

(1)测试74LS86四-2输入异或门的逻辑功能

74LS86引脚排列如图1.8所示。

图1.8 74LS86引脚排列

接线如图1.8所示,用开关改变输入变量A、B的状态,通过发光二极管观测输出端Y的状态,将观测结果填入表1.5中。

表1.5异或门逻辑功能测试表

输入

输出

AB

Y

00

01

10

11

图1.8 异或门逻辑功能测试图

4.设计一个三变量的多数表决电路。

执行的功能是:

少数服从多数,多数赞成时决议生效。

用与非门实现。

解:

(1)逻辑设计

在这个逻辑问题中,设A、B、C为输入变量,分别代表参加表决的逻辑变量,变量为1表示赞成,为0表示反对;设Y为输出变量,表示表决结果,为1表示通过,为0表示不通过。

列出真值表如表1.6。

表1.6三变量表决电路真值表

输入

输出

ABC

Y

000

001

010

011

100

101

110

111

0

0

0

1

0

1

1

1

图1.9 三人表决电路图

根据真值表1.6写出Y的与或表达式,即:

实验仅提供与非门,如实现上述逻辑,则必须化简为“与非”的形式,即:

(2)拟订实验线路并进行验证

画出接线图如图1.9。

输入端A、B、C分别接三个逻辑开关,输出端Y接逻辑电平指示灯。

将测试结果与真值表1.6对照验证。

五、实验报告要求

1.列写实验任务的设计过程,画出设计的电路图。

2.对所设计的电路进行实验测试,记录测试结果,将实验结果填入各相应表中,书写到实验记录中。

3.总结各门电路的逻辑功能和TTL门电路的多余输入端的处理方法。

4.通过本次实验总结TTL的特点及使用的收获和体会。

六、实验预习要求

1、详细阅读附录,了解数字集成电路的基本功能及使用方法。

2、复习教材中基本门电路的逻辑功能和结构原理。

3、了解在使用TTL时,与非门和与或非门多余输入端分别如何处理?

4、按实验内容要求设计逻辑电路,写出逻辑函数式。

注意事项:

对于与或非而言,如果一个与门中一条或几条输入引脚不被使用,则需将它们接高电平;如果一个与门不被使用,则需将此与门的至少一条输入引脚接低电平。