实验二一位全加器实验.docx

《实验二一位全加器实验.docx》由会员分享,可在线阅读,更多相关《实验二一位全加器实验.docx(11页珍藏版)》请在冰豆网上搜索。

实验二一位全加器实验

实验二一位全加器实验

【实验环境】

1.Windows2000或WindowsXP

2.QuartusII、GW48-PK2或DE2-115计算机组成原理教学实验系统一台,排线若干。

【实验目的】

1、熟悉原理图和VHDL语言的编写。

2、验证全加器功能。

【实验原理】

设计一个一位全加器,能完成两个二进制位的加法操作,考虑每种情况下的进位信号,完成8组数据的操作。

【实验步骤】

1.1建立工程项目

1.1.1启动QuartusⅡ

1.1.3原理图设计

新建项目后,就可以绘制原理图程序了。

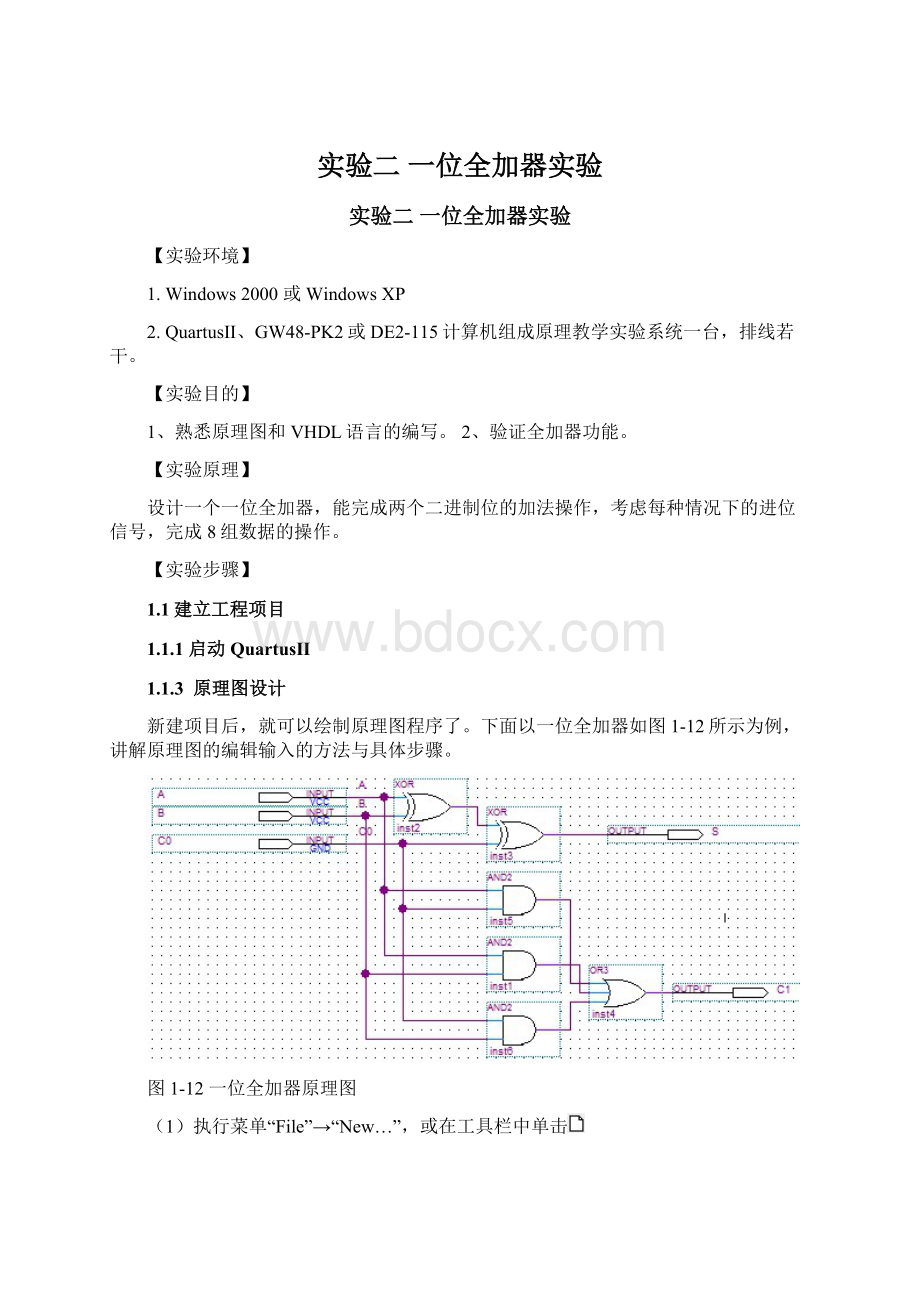

下面以一位全加器如图1-12所示为例,讲解原理图的编辑输入的方法与具体步骤。

图1-12一位全加器原理图

(1)执行菜单“File”→“New…”,或在工具栏中单击

图标,弹出如图1-13所示的“New”对话框。

在此对话框的“DesignFiles”项中选择“BlockDiagram/SchematicFile”,在单击“OK”按钮,QuartusⅡ10.0的主窗口进入如图1-14所示的原理图工作环境界面。

图1-13“New”对话框

(2)在如图1-14所示的原理图工作环境界面中单击

图标或在原理图编辑区的空白处双击鼠标或在原理图编辑区的空白处右键单击在弹出的菜单中选择“Insert”中的任意一个,弹出如图1-15所示的元件输入对话框,在“Name”栏中直接输入所需元件名或在“Libraries:

”的相关库中找到合适的元件,再单击“OK”按钮,然后在原理图编辑区中单击鼠标左键,即可将元件调入原理图编辑区中。

为了输入如图1-12所示的原理图,应分别调入and2、xor2、or3、input、output。

对于相同的器件,可通过复制来完成。

例如3个and2门,器操作方法是,调入一个and2门后,在该器件上单击鼠标右键,在弹出的菜单中选择“Copy”命令将其复制,然后在合适的位置上右键,在弹出的菜单中选择“Paste”命令将其粘帖即可。

图1-14原理图工作环境界面

图1-15元件输入对话框

(3)将光标指向元件的引脚上,光标变成“十”字形状,按下鼠标左键并拖动,就会有导线引出,连接到另一端的元件上后,松开鼠标左键,即可绘制好一根导线,按此方法绘制好全部导线,如图1-16所示。

图1-16导入元件和绘制导线(注意:

用鼠标拖出的导线只能最多转一个弯)

图1-17修改引脚名对话框

(4)双击或右键单击“pin_name”输入引脚,将弹出如图1-17所示的对话框。

在此对话框的“Gerneral”页的“Pinname(s)”项中输入引脚名,如:

S,然后单击“确定”按钮,即可将“pin_name”输入引脚名改为“S”。

按此方法依次修改其他引脚。

修改后如图1-16所示。

(5)执行菜单命令“File”→“Save…”,或在工具栏中单击

图标,弹出“SaveAS”对话框,在此对话框中输入文件名并单击“保存”按钮即可(此时最好不要更改存储路径)。

2.1顶层VHDL文件设计

2.1.1创建工程和编辑设计文件

首先建立工作库,以便设计工程项目的存储。

任何一项设计都是一项工程(Project),都必须首先为此工程建立一个放置与此工程相关的所有文件的文件夹,此文件夹将被EDA软件默认为工作库(WorkLibrary)。

在建立了文件夹后就可以将设计文件通过QuartusII的文本编辑器编辑并存盘,详细步骤如下:

1、新建一个文件夹。

利用资源管理器,新建一个文件夹,如:

e:

\eda。

注意,文件夹名不能用中文。

2、输入源程序。

打开QuartusII,选择菜单“File”“New”,在New窗中的“DeviceDesignFiles”中选择编译文件的语言类型,这里选“VHDLFiles”(如图2-1所示)。

然后在VHDL文本编译窗中键入VHDL程序(如图2-2所示)。

图2-1选择编辑文件的语言类型

图2-2编辑输入设计文件(顶层设计文件ADD1.VHD)

图2-3利用“NewPrejectWizard”创建工程

图2-4创建工程文件及顶层文件

图2-5将所有相关的文件都加入进此工程

3、文件存盘。

选择“File”“SaveAs”,找到已设立的文件夹e:

\syadd1,存盘文件名应该与实体名一致,即add1.vhd。

3.1编译及下载

4.1.1建立仿真文件

执行菜单命令“File”→“New…”,或在工具栏中单击

图标,弹出图2-13所示的“New”对话框。

在此对话框的“Verification/DebuggingFiles”项中选择“VectorWaveformFile”,再单击“OK”按钮,QuartusⅡ的主界面窗口进入如图2-28所示的波形文件编辑环境界面。

图2-28波形文件编辑环境界面

在波形文件编辑方式下,执行菜单命令“Edit”→“Insert”→“InsertNodeorBus…”,或在波形编辑窗口右边“Name”下的空白处单击鼠标右键,在弹出的菜单中选择“InsertNodeorBus”命令,即可弹出如图2-29所示的插入节点或总线对话框。

在图2-29所示的对话框中,单击“NodeFinder…”按钮,弹出如图2-30所示的“NodeFinder”对话框,在“Filter”栏中选择“Pins:

all”,单击“List”按钮,这时在窗口左边的“NodesFound:

”(节点建立)框中将列出该设计项目的全部信号节点。

若在仿真中需要观察全部信号的波形,则单击窗口中间的

按钮;若在仿真中只需观察部分信号的波形,则首先用鼠标单击信号名→单击窗口中的

按钮,或直接双击信号名,选中的信号则进入到窗口右边的“SelectedNodes:

”(被选择的节点)框中;如果需要删除“SelectedNodes:

”框中的节点信号,也可以用鼠标将其选中→单击窗口中的

按钮,或直接双击信号名;

按钮是将“SelectedNodes:

”框中的节点信号全部删除。

节点信号选择完毕后,单击“OK”按钮即可。

图2-29插入节点或总线对话框

图2-30“NodeFinder”对话框(注意:

前面设置时要选择一个设备,否则没有Pins:

all项)

4.1.2仿真设置工具

QuartusⅡ默认的仿真时间域是1μs。

如果需要更长的时间观察仿真结果,需设置仿真时间。

执行菜单命令“Edit”→“EndTime…”,弹出如图2-31所示对话框,在“Time:

”栏中输入合适的仿真时间即可。

在波形编辑界面内,左排按钮是用于设置输入信号的,使用时,只要先用光标在波形输入上拖一需要改变的区域,然后单击左排相应按钮即可。

或右键要设置值的节点信号,弹出如图2-32所示快捷菜单,单击“Value”→“ConutValue”弹出如图2-33所示对话框,按如图2-35所示设置。

还可以通过右键弹出菜单“Properties”设置信号节点波形以何种进制显示。

最后,执行菜单命令“File”→“Save…”,或在工具栏中单击

图标,弹出“SaveAs”对话框,在此对话框中输入文件名,并按下保存即可(注意:

最好和编译的文件同名如:

add1)。

图2-31设置仿真时间域对话框图2-34信号节点属性设置框

图2-35设置了输入信号的波形编辑器

图2-32设置节点值快捷菜单

4.1.3功能仿真

执行菜单命令“Processing”→“StartSimulation”,弹出如图2-36所示的仿真工具对话框,选择“Functional”功能仿真,单击对话框中的

图标按钮,弹出“打开”对话框,找到保存的add1.vwf波形文件打开。

然后单击“GenerateFunctionalSimulationNetlist”按钮,生成功能仿真网络表。

最后,单击

按钮,进行功能仿真。

单击

查看生成的功能仿真波形图,如图2-37所示。

分析波形,主要分析输入和输出的逻辑关系。

从如图2-37所示中的波形可以看出,当A=”1”,B=”0”,C0=”1”时,S=“0”,C1=”1”,即S为A、B、C0的和,C1为进位。

4.1.4时序仿真

5.实验总结和心得

通过这次试验,我熟悉原理图和VHDL语言的编写,明白了一位全加器的原理。

虽然原理很简单,但一开始还是遇到了困难,没能得到结果。

最后经过自己的检查和老师的帮助得到了正确的实验结果。