EDA开发实践B实验指导书n.docx

《EDA开发实践B实验指导书n.docx》由会员分享,可在线阅读,更多相关《EDA开发实践B实验指导书n.docx(61页珍藏版)》请在冰豆网上搜索。

EDA开发实践B实验指导书n

1. 8‐3编码器及QuartusII的基础

一、实验目的

1.学习组合逻辑电路,学习编码器的功能与定义,学习VHDL语言

2.熟悉利用Quartus II开发数字电路的基本流程和Quartus II软件的相关操作

二、实验内容

编写8‐3编码器的VHDL代码,编译下载后通过拨动拨码开关观察LED灯的变化,来验证8‐3编码器是否成功。

三、实验原理

在数字系统中,常常需要将某一信息(输入)变换为某一特定的代码(输出)。

把二进制码按一定的规律排列,例如8421码、格雷码等,使每组代码具有一特定的含义(代表某个数字或是控制信号)称为编码。

具有编码功能的逻辑电路称为编码器。

编码器有若干个输入,在某一时刻只有一个输入被转换为二进制码。

例如8线‐3线编码器和10线‐4线编码器分别有8输入、3位输出和10位输入、4位输出。

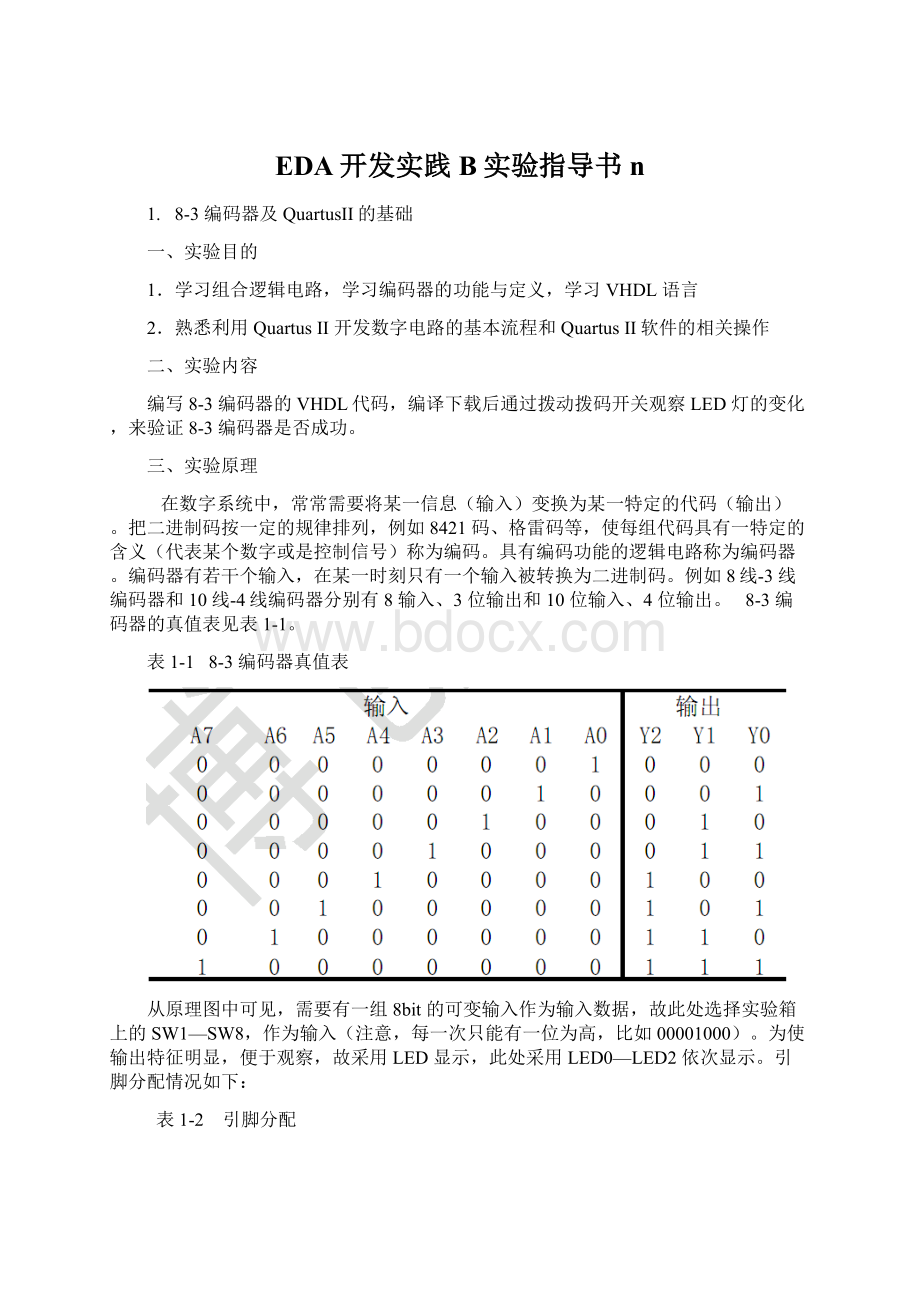

8‐3编码器的真值表见表1‐1。

表1‐1 8‐3编码器真值表

从原理图中可见,需要有一组8bit的可变输入作为输入数据,故此处选择实验箱上的SW1—SW8,作为输入(注意,每一次只能有一位为高,比如00001000)。

为使输出特征明显,便于观察,故采用LED显示,此处采用LED0—LED2依次显示。

引脚分配情况如下:

表1‐2 引脚分配

四、实验步骤

1.选择“开始”→“所有程序”→“Altera”→“Quartus II 9.0” →“Quartus II 9.0(32‐Bit)”,启动软件。

图1‐2 Quartus II启动界面

2.选择“File” →“New Project Wizard”,出现“Introduction”页面,如图1‐4所示,该页面介绍所要完成的具体任务。

图1‐3 选择 New Project Wizard

图1‐4 新建工程向导

3.单击“Next”按钮,进入工程名称的设定、工作目录的选择。

图1‐5 指定工程路径、工程名和顶层实体名

4.如图1‐5所示。

在对话框中第一行选择工程路径;第二行输入工程名,第三行输入顶层文件的实体名(注意:

工程名必须与顶层实体名相同,工程目录可以随意设置,但必须是英文的目录,工程名跟顶层实体名必须也是英文开头。

不要将文件夹设在计算机已有的安装目录中,更不要将工程文件直接放在安装目录中。

文件夹所在的路径名和文件夹名不能用中文,不能用空格,不能用括号,也不能以数字开头)这里输入encoder8_3;单击“Next”按钮,出现如图1‐6所示的对话框。

图1‐6 新建工程文件添加对话框

在图所示的对话框中,可以为工程添加先期已经输入的设计文件,制定用户自定义的元件库的路径,这里没有事先输入好的文件,也没有自定义的元件库,单击“Next”按钮进入下一步,出现如图1‐7所示的对话框。

图1‐7 新建工程器件选择对话框

在图所示的对话框中,我们根据本实验箱所选的芯片型号,在Family下拉菜单中选择Cyclone II 系列。

然后在Filters下的Package下拉菜单中选择封装形式FBGA,Pin count下拉菜单中选择管脚数672,Speed grade下拉菜单中选择速度级别8;然后在Available devices中选择EP2C35F672C8器件。

点击“Next”进入下一步。

5.单击“Next”进入图1‐8所示的对话框,用户指定在Quartus II之外的用于设计输入、综合、仿真、时序分析的第三方EDA工具对话框,这里都不选,直接单击“Next”进入工程信息对话框.

图1‐8在Quartus II里面新建工程

最后单击“Finish”完成工程建立。

图1‐9新建工程完毕

6.新建设计文件,选择“File|New” ,在New对话框中选择Device Design Files下的VHDL File,单击OK,完成新建设计文件。

如图1‐10所示。

图1‐10在Quattus II里面新建文件

7.在新建设计文件中输入VHDL程序,源代码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

entity encoder8_3 is

port

(

DIN :

in std_logic_vector(7 downto 0);

DOUT:

out std_logic_vector(2 downto 0)

);

end encoder8_3;

architecture rt1 of encoder8_3 is

begin

process(DIN)

begin

case DIN is

when“10000000”=> DOUT <= “111”;

when“01000000”=> DOUT <= “110”;

when“00100000”=> DOUT <= “101”;

when“00010000”=> DOUT <= “100”;

when“00001000”=> DOUT <= “011”;

when“00000100”=> DOUT <= “010”;

when“00000010”=> DOUT <= “001”;

when“00000001”=> DOUT <= “000”;

whenothers=>:

DOUT <= “zzz”;

endcase;

end process;

endrt1;

本例只有一个设计文件,即为顶层设计文件,它的实体名一定要与顶层设计文件名encoder8_3一致,然后保存到工程文件夹Project下,命名为encoder8_3,即为顶层设计文件。

如图1‐11所示。

图1‐11保存文件

8. 管脚分配。

在附录A中有详细的管脚分配说明,这里采用第二种方法即使用qsf文件的方法。

在这里,还是把这个过程详细的说明一遍。

管脚分配是FPGA设计的一项必须做的工作,我们在设计完FPGA芯片里面的内容后需要把设计的顶层的接口与FPGA片外的管脚连接起来,只有这样我们的设计才能运行。

从第七步可以得知,设计中的顶层接口就是DIN[7:

0]和DOUT[2:

0],一共11个。

就是说这11个接口要与FPGA片外的引脚相连。

8‐3编码器是通过8路编码,观察3路的输出。

所以DIN[7:

0]要与平台上的8个拨码开关相连,DOUT[2:

0]要与平台3个LED灯相连。

这样8个拨码开关的编码通过3个LED灯观察到。

在建立QuartusII工程的时候,会自动建立一个与工程名一样的qsf文件。

打开工程中的qsf文件,如图1‐12。

会看到工程的信息。

图1‐12 qsf文件内容

我们把FPGA所有的固定好的管脚做成一个FPGA2C35_pins.txt文件,要用到那个管脚都可以到这个记事本文件中查找。

打开FPGA2C35_pins.txt文件,找到拨码开关和LED灯的地方。

如图1‐13。

把8个sw全部复制到qsf文件中,同样把LED前3个复制到qsf文件。

图1‐13 FPGA2C35_pins.txt中拨码开关的位置

然后把sw名字改为DIN, LED_DOWN名字改为DOUT。

改好后的qsf文件如图1‐14.

图1‐14 改好后的qsf文件

然后把这个qsf文件保存关闭。

9. 未使用的管脚置成三态。

高阻

平台核心板上的FPGA共有672个管脚,但是只是使用其中的2个,还有大量未使用管脚,我们需要对这些未使用的管脚进行设置,这一步是非常重要的。

QuartusII默认使用的输出接地(意思是设置为低电压,也可以称为逻辑0),如果不进行设置的话,这些管脚都处于工作状态,一方面FPGA的耗电量增加芯片会发烫,这样会降低FPGA芯片的寿命;另一方面,处于工作状态的管脚可能相互影响。

双击图1‐15界面中的 CycloneII :

EP2C35F672C8 . 弹出如图1‐16的界面,

图1‐15 打开FPGA设置

图1‐16 进入FPGA设置

在图1‐16中点击 Device and Pin Options, 弹出图1‐17的界面。

找到 Unused Pins栏,设置成Asinput tri‐stated. 点击确定,回到图1‐16 ,再点击OK返回QuartusII。

图1‐17 置成 input tri‐stated

10.选择“Processing→Start Compilation”,或者单击工具栏中的Start Compilation按钮进行全程编译,也可以在“Processing”菜单中选择“Start”子菜单中的分布编译操作。

图1‐18 编译工程

11.编译的时候,Quartus II会给出编译进度,“Compilation Report”窗口会给出编译结果,编译 结果会随着编译进度随时更新。

Message窗口会给出编译过程的具体情况,包括“information,warning,error”等。

“information”多是完成的一些编译的进展描述;可能会出现很多warning但并不影响编译的进行;如果出现error,那么设计是不成功的,用户需要改正这些错误,然后重新 编译。

可以对错误进行定位,选中错误信息,右击,在弹出的菜单中选择Locate来实现对错误的定位。

编译成功以后,会出现如下图所示的提示。

图1‐19 编译结果提示

12. 下载配置FPGA。

连接好USB‐Blaster,具体的安装步骤在附录C中,然后把平台电源打开,这里需要的注意的是USB‐Blaster不能带电插拔。

在QuartusII中点击选择Tools‐Programmer或者单击工具栏上的

,弹出如图1‐20的界面。

如果USB‐Blaster连接正确会在 Hardware Setup的右侧出现 USB‐Blaster[USB ‐0] . 确认Program/Configure下面的勾打上。

下载的文件是QuartusII编译生成的encoder8_3.sof 。

点击 Start开始下载 。

图1‐20 下载界面

如果发现蜂鸣器在响,说明第9步的操作有问题,FPGA的管脚没有设置成输入三态。

任意操作SW1—SW8(注意,每一次只能有一位为高,比如00001000),观察LED灯的变化,分析是否与Verilog HDL或VHDL编写的一致。

2. 3‐8译码器及QuartusII的仿真

一、实验目的

1.学习组合逻辑电路,学习译码器的功能与定义,学习VHDL语言。

2.熟悉利用Quartus II开发数字电路的基本流程和Quartus II软件的相关操作。

3. 掌握利用QuartusII做时序和功能仿真

二、实验内容

编写3‐8译码器的Verilog代码和VHDL代码,首先在QuarutsII中做仿真,观察仿真结果与设计源码是否一致,再通过编译并下载到平台上验证。

三、实验原理

译码是编码的逆过程,它的功能是将特定含义的二进制码进行辨别,并转换成控制信号,具有译码功能的逻辑电路成为译码器。

译码器可分为两种类型,一种是将一系列代码转换成与之一一对应得有效信号。

这种译码器可以称为唯一地址译码器,它常用于计算机中对存储器单元地址的译码,即将每一个地址代码换成一个有效信号,从而选中对应的单元。

另一种是将一种代码转换成另一种代码,

所以也称为代码变换器。

在本实验中我们先介绍二进制唯一地址译码器,在下一实验中,我们介绍代码变换器。

3线‐8线译码器的真值表见表2‐1,

表2‐1 3‐8译码器真值表

实验箱上的SW1—SW3作为控制信号输入,SW4—SW6作为片选信号输入,LED1—LED8显示输出译码值。

引脚分配情况如下:

表2‐2 引脚分配

四、实验步骤

1.新建工程,取名decoder3_8,如下图所示。

图2‐1 指定工程的目录、工程名和顶层实体名

2.新建VHDL设计文件,选择“File|New” ,在New对话框中选择Device Design Files下的VHDL File,单击OK,完成新建设计文件。

3.在新建设计文件中输入VHDL程序,源代码如下:

4、输入完毕,点击 Start Complication 。

对QuartusII工程编译,如果有错误返回上一步检查错误,重新编译直到没有错误为止。

5、新建QuartusII的仿真文件。

点击 File菜单下的New,弹出如图2‐2 。

选择Vector Waveform File, 点击OK。

弹出图2‐3的界面,在左侧栏中双击空白的地方,会弹出图2‐4的界面。

图2‐2 新建仿真文件

图2‐3 仿真文件

图2‐4 插入符号

点击图2‐4中的Node Finder, 弹出图2‐5。

图2‐5 添加信号

在图2‐5中添加仿真信号,Filer:

选择Pins:

all ,点击List,在左侧栏中会出现设计源码中所有的信号都列出来,在这个列表中选择要仿真的信号,选中某一个信号后点击“>”,就会添加到右侧栏中。

点击“》”是把所有信号都添加,这里添加DIN、DOUT、G1、G2和G3,如图2‐5。

然后点击OK返回。

在图2‐4点击OK。

那么会看到选择后的信号出现在图2‐3中。

仿真设计中需要给定输入观察输出的结果,这里DIN、G1、G2和G3是输入,DOUT是输出,分别给定DIN、G1、G2和G3赋初值,右键点击DIN,选择Value菜单中的Count Value,也就是把DIN的初值赋为自动增一的变量,如图2‐6 。

同样把G1赋为Forcing High ,G2和G3赋为Forcing Low 。

图2‐6 为输入赋初值

赋初值后,如图2‐7所示。

然后保存vwf文件,要把 Add to Current project前面的勾打上。

再重新编译QuartusII工程。

结束后点击图2‐8中的 Start Simulation 。

图2‐7 为输入赋初值

图2‐8 开始仿真

图2‐9 仿真结果

等待片刻后出现图2‐9的界面,图中显示的是仿真的结果。

根据VHDL源码分析查看仿真结果与源码中是否一致。

6、管脚分配。

下面把设计下载到FPGA中验证,与实验一和实验二一样,先进行管脚分配,具体步骤这里不再重复,不清楚的读者请查看前两个实验和附录A。

把G1、G2和G3分配给拨码开关的前三个sw0,sw1和sw2 ,DIN分配给拨码开关的sw3、sw4和sw5,DOUT分配给8个LED。

注意管脚分配完毕后一定要把Qsf文件保存退出。

7、未使用的管脚设置三态。

双击QuartusII左上角的CycloneII :

EP2C35F672C8 。

然后点击device and Pins Options,选择Unused Pins栏,设置As Input tri‐stated。

8、编译QuartusII工程,结束后连接好USB‐Blaster和平台的电源之后,在QuartusII中点击Programmer下载生成的.sof文件。

9、观察结果。

拨动SW0—SW5 ,观察LED的变化。

验证是否与源码和仿真的结果一致。

3. 半加器与全加器及图形设计方法

一、实验目的

1.学习半加器和全加器的设计,进一步了解、熟悉和掌握FPGA开发软件Quartus II的使用方法

2.学习Verilog HDL和VHDL的编程方法

3.巩固QuartusII的仿真和图形设计方法。

二、实验内容

编写半加器和全加器的Verilog 代码和VHDL代码并仿真,编译下载验证。

三、实验原理

算术运算式数值系统的基本功能,更是计算机中不可缺少的组成单元。

1、半加器

半加法和全加法是算术运算电路中的基本单元,它们是完成1位二进制相加的一种组合逻辑电路。

一位加法器的真值表见表3‐1;由表中可以看见,这种加法没有考虑低位来的进位,所以称为半加。

半加器就是实现表3‐1中逻辑关系的电路。

表3‐1 半加器的真值表

2、全加器

全加器能进行加数、被加数和低位来的进位信号相加,并根据求和结果给出该位的 进位信号。

根据它的功能,可以列出它的真值表,如表3‐2所示。

表3‐2 全加器的真值表

3、半减法和全减法

半减法和全减法与加法器一样是算术运算电路中的基本单元。

半减器和全减器的设计方法和设计加法器相同,但是实际上,为了简化系统结构,通常不设计减法器,而是将减法运算变为加法运算来出来,使运算器即能实现加法器运算,又能实现减法器运算。

一般采用加补码的方法代替减法运算。

图3‐1 设计原理框图

从原理图中可见,需要有两个数据输入位还有一个低位进位,数据输入我们采用实验箱上的SW1和SW2,进位采用SW3,LED1显示和输出,LED2显示进位输出。

引脚分配情况

表3‐3 引脚分配

四、实验步骤

1.新建工程,取名为adder,如下图所示。

图3‐2 指定工程的目录、工程名和顶层实体名

2.新建VHDL设计文件,选择“File|New” ,在New对话框中选择Device Design Files

下的VHDL File,单击OK,完成新建设计文件。

3.在新建设计文件中输入VHDL程序,源代码如下:

4、为设计源码生成图形设计文件。

在QuartusII中点击File菜单,在Create/Update 中点击 Create Symbol file for Current project ,如图3‐3 。

这时QuartusII会检查VHDL源码是否有错误,没有错误的话就会为这个设计源码生成一个带外围接口的图形。

5、在QuartusII新建图形设计文件。

点击File菜单下的New ,选择Block Diagram/Schematic File ,如图3‐4 。

点击OK。

图3‐4 新建图形设计文件

6、在新建的图形设计文件中会看到有很多小点,在随意的一个地方双击鼠标左键,会弹出如图3‐5的界面,打开Project会出现一个adder,在右侧栏同时会显示它的顶层图形。

这个图形就是在第4步,QuarutsII为源码生成的图形设计。

7、点击OK,用鼠标把图形符号拖动到刚才新建的带小点的文件中,从这个图形符号可以看出,VHDL源码中port部分全部显示出来,左边的是输入接口,右侧的是输出接口。

现在需要做的是把这些输入和输出接口与FPGA片外的管脚连接在一起,首先要把这些输入输出接口从FPGA片内引出来。

还是在空白处双击鼠标左键,弹出3‐5的界面,在Name框里输入input ,会出现input引脚的界面,如图3‐6.

图3‐6 添加输入引脚

8、点击OK把input引脚添加到图形设计中,采用同样方法添加其他9个intput和output引脚。

连接adder的外围接口和intput引脚。

按住鼠标左键,从input引脚的末端拖出一条线直到adder对应的信号,每个引脚都是同样操作,完成后如图3‐7所示。

然后双击input引脚,修改名称,如pin_name修改为A 。

9、生成“Symbol”文件,新建“Block Diagram/Schematic File”文件,在文件中添加刚刚生成的“Symbol”以及输入输出管脚,最后完整的系统顶层模块图如图3‐3所示。

图3‐7 顶层模块图

10、保存文件,使用qsf或者tcl进行管脚分配(相应的文件在本工程里面都可以找到)。

11、对该工程文件进行全程编译处理,若在编译过程中发现错误,则找出并更正错误,直至编译成功为止。

12、新建“Vector Waveform File”文件进行波形仿真。

其中A,B为输入数据,Ci低位进位。

图3‐8 利用vector file仿真数据选择器的波形

13、下载完成后,通过 SW1—SW3控制着输入的电平,观察实验结果。

4. 寄存器及SignalTapII的使用

一、实验目的

1.学习时序逻辑电路的设计,进一步了解、熟悉和掌握FPGA开发软件Quartus II的使用方法

2.了解寄存器的工作原理和设计思路

3.学习嵌入式逻辑分析仪SignalTapII的使用

二、实验内容

在实验寄存器功能后,增加SignalTapII嵌入式逻辑分析仪的使用。

最终下载到平台上用 SignalTapII观察FPGA内部信号的波形。

三、实验原理

寄存器是计算机和其他数字系统中用来存储代码或数据的逻辑部件。

它的主要组成部分是触发器。

一个触发器能储存一位二进制代码,所以要存储n位二进制代码的寄存器需要n个触发器组成。

寄存器和数据锁存器功能是相同的,不同的区别在于锁存器是电平信号控制,属于电平敏感性,而寄存器一般是由同步时钟信号控制。

两者使用场合不一样,主要取决于控制方式及控制信号和数据之间的时序关系:

若数据有效滞后于控制信号有效,则只能使用锁存器;若数据提前于控制信号,并要求同步操作,而可以选择寄存器来存放数据。

本实验就是设计一个8 位的数据寄存器,该寄存器可以对8位信号并行输入的数据进行同步寄存。

另外,该寄存器还有一个异步清零端,低电平有效。

其功能表如表4‐1所示;设计原理框图如图4‐1所示。

表4‐1 8位数据寄存器功能表

图4‐1 设计原理框图

从原理图中可见,需要有一组8bit的可变输入作为输入数据和1bit清零使能位。

数据输入我们采用实验箱上的SW1—SW8,BTN1作为CLR清零使能位。

LED1‐