eda编程.docx

《eda编程.docx》由会员分享,可在线阅读,更多相关《eda编程.docx(15页珍藏版)》请在冰豆网上搜索。

eda编程

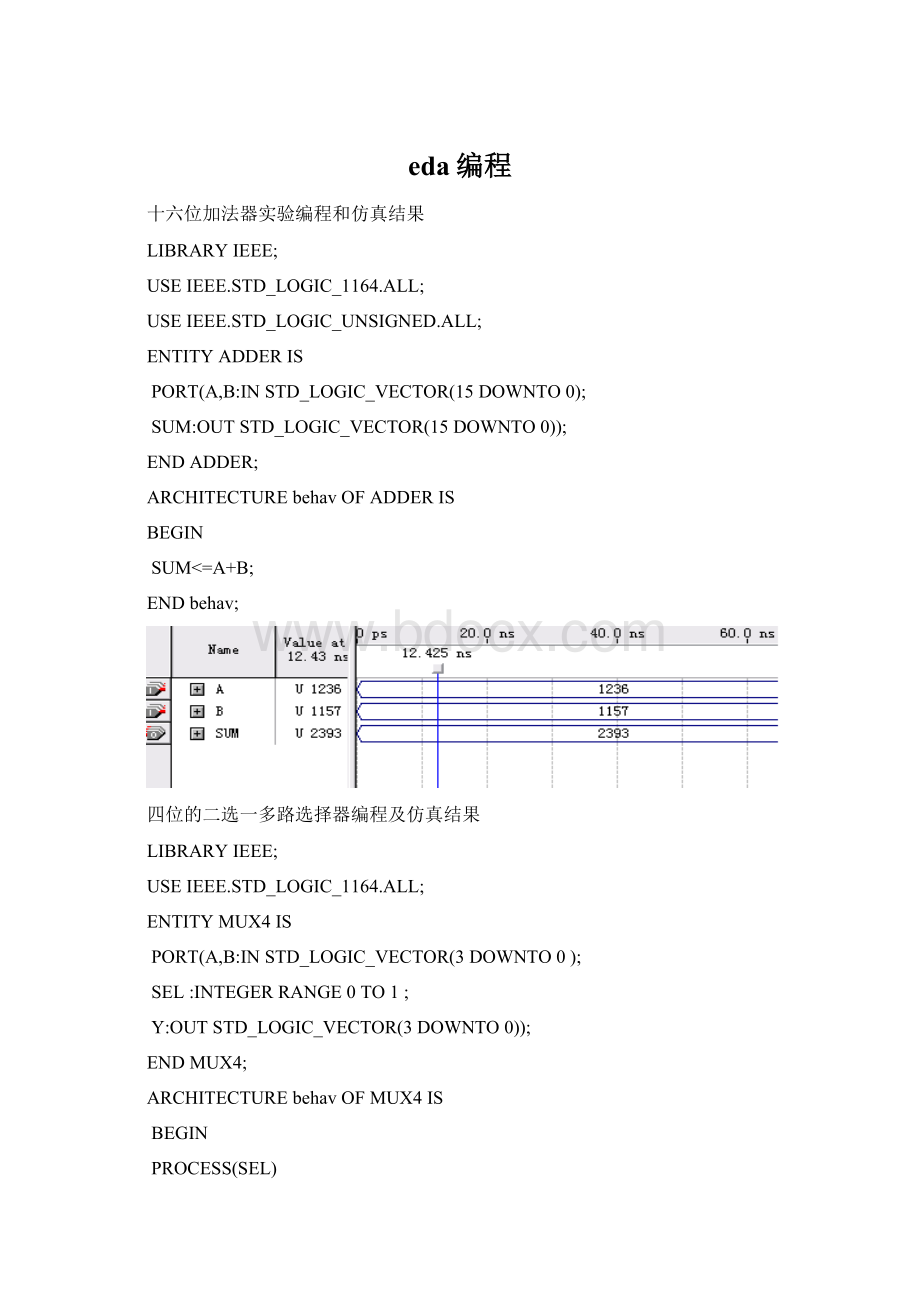

十六位加法器实验编程和仿真结果

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYADDERIS

PORT(A,B:

INSTD_LOGIC_VECTOR(15DOWNTO0);

SUM:

OUTSTD_LOGIC_VECTOR(15DOWNTO0));

ENDADDER;

ARCHITECTUREbehavOFADDERIS

BEGIN

SUM<=A+B;

ENDbehav;

四位的二选一多路选择器编程及仿真结果

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYMUX4IS

PORT(A,B:

INSTD_LOGIC_VECTOR(3DOWNTO0);

SEL:

INTEGERRANGE0TO1;

Y:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDMUX4;

ARCHITECTUREbehavOFMUX4IS

BEGIN

PROCESS(SEL)

BEGIN

IFSEL=0THENY<=A;

ELSEY<=B;

ENDIF;

ENDPROCESS;

ENDbehav;

七段数码管译码器编程及仿真结果

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYLED7IS

PORT(INPUT:

INSTD_LOGIC_VECTOR(2DOWNTO0);

A,B,C,D,E,F,G:

OUTSTD_LOGIC);

ENDLED7;

ARCHITECTUREbehavOFLED7IS

BEGIN

PROCESS(INPUT)

BEGIN

CASEINPUTIS

WHEN"000"=>A<='1';B<='1';C<='1';D<='1';E<='1';F<='1';G<='0';

WHEN"001"=>A<='0';B<='1';C<='1';D<='0';E<='0';F<='0';G<='0';

WHEN"010"=>A<='1';B<='1';C<='0';D<='1';E<='1';F<='0';G<='1';

WHEN"011"=>A<='1';B<='0';C<='0';D<='1';E<='1';F<='1';G<='1';

WHENOTHERS=>A<='1';B<='0';C<='1';D<='0';E<='0';F<='1';G<='1';

ENDCASE;

ENDPROCESS;

ENDbehav;

8位16位移位器编程及仿真结果

LIBRARYIEEE;

USEIEEE.std_logic_1164.all;

USEIEEE.std_logic_arith.all;

USEIEEE.std_logic_unsigned.all;

ENTITYshifterIS

PORT(input:

INstd_logic_vector(7downto0);

cnt:

INstd_logic_vector(1downto0);

result:

OUTstd_logic_vector(15downto0)

);

ENDshifter;

ARCHITECTURElogicOFshifterIS

BEGIN

PROCESS(input,cnt)

VARIABLEtemp:

std_logic_vector(15downto0);

BEGIN

temp(15downto8):

="00000000";

temp(7downto0):

=input;

IFcnt="01"THEN

FORiIN15DOWNTO4LOOP

temp(i):

=temp(i-4);

ENDLOOP;

temp(3downto0):

="0000";

ELSIFcnt="10"THEN

FORiiN15DOWNTO8LOOP

temp(i):

=temp(i-8);

ENDLOOP;

temp(7downto0):

="00000000";

ELSE

temp:

=temp;

ENDIF;

result<=temp;

ENDPROCESS;

ENDlogic;

A16位同步寄存器编程及仿真结果

LIBRARYIEEE;

USEIEEE.std_logic_1164.all;

USEIEEE.std_logic_unsigned.all;

ENTITYregIS

PORT(CLK,CLKEN,CLR:

INstd_logic;

IN_REG:

INstd_logic_vector(15downto0);

OUT_REG:

OUTstd_logic_vector(15downto0));

ENDreg;

ARCHITECTURElogicOFREGIS

BEGIN

PROCESS(clk)

BEGIN

IFrising_edge(clk)THEN

IFclken='0'THEN

IFclr='1'THENOUT_REG<=in_reg;

ELSIFclr='0'THENOUT_REG<=(OTHERS=>'0');

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

ENDlogic;

B2位异步计数器编程及仿真结果

LIBRARYIEEE;

USEIEEE.std_logic_1164.all;

USEIEEE.std_logic_unsigned.all;

ENTITYcounterIS

PORT(clk,clr:

INstd_logic;

sum:

OUTstd_logic_vector(1downto0));

ENDcounter;

ARCHITECTURElogicOFcounterIS

BEGIN

PROCESS(clk,clr)

VARIABLEcount:

std_logic_vector(1downto0);

BEGIN

IFclr='0'THEN

count:

="00";

sum<=count;

ELSIFrising_edge(clk)THEN

count:

=count+1;

sum<=count;

ENDIF;

ENDPROCESS;

ENDlogic;

A状态机的编程及仿真结果

LIBRARYIEEE;

USEIEEE.std_logic_1164.all;

USEIEEE.std_logic_unsigned.all;

ENTITYcontrolIS

PORT(clk,rst,start:

INstd_logic;

count:

INstd_logic_vector(1downto0);

in_sel,shift:

OUTstd_logic_vector(1downto0);

state_out:

OUTstd_logic_vector(2downto0);

done,clken,regclr:

OUTstd_logic);

ENDcontrol;

ARCHITECTURElogicOFcontrolIS

TYPEstate_typeIS(idle,lsb,mid,msb,err);

SIGNALcode:

state_type;

BEGIN

PROCESS(rst,clk)

BEGIN

IFrst='1'THEN

code<=idle;

ELSIFrising_edge(clk)THEN

CASEcodeIS

WHENidle=>

IFstart='1'THEN

code<=lsb;

ELSE

code<=idle;

ENDIF;

WHENlsb=>

IFstart='0'andcount="00"THEN

code<=mid;

ELSE

code<=err;

ENDIF;

WHENmid=>

IFstart='0'andcount="10"THEN

code<=msb;

ELSIFstart='0'andcount="01"THEN

code<=mid;

ELSE

code<=err;

ENDIF;

WHENmsb=>

IFstart='0'andcount="11"THEN

code<=idle;

ELSE

code<=idle;

ENDIF;

WHENerr=>

IFstart='1'THEN

code<=lsb;

ELSE

code<=err;

ENDIF;

WHENOTHERS=>

code<=idle;

ENDCASE;

endif;

ENDPROCESS;

mealy:

PROCESS(code,start,count)

BEGIN

CASEcodeIS

WHENidle=>

IFstart='1'THEN

in_sel<="XX";

shift<="XX";

done<='0';

clken<='1';

regclr<='0';

ELSE

in_sel<="XX";

shift<="XX";

done<='0';

clken<='1';

regclr<='1';

ENDIF;

WHENlsb=>

IFstart='0'andcount="00"THEN

in_sel<="00";

shift<="00";

done<='0';

clken<='0';

regclr<='1';

ELSE

in_sel<="XX";

shift<="XX";

done<='0';

clken<='1';

regclr<='1';

ENDIF;

WHENmid=>

IFstart='0'andcount="10"THEN

in_sel<="10";

shift<="01";

done<='0';

clken<='0';

regclr<='1';

ELSIFstart='0'andcount="01"THEN

in_sel<="01";

shift<="01";

done<='0';

clken<='0';

regclr<='1';

ELSE

in_sel<="XX";

shift<="XX";

done<='0';

clken<='1';

regclr<='1';

ENDIF;

WHENmsb=>

IFstart='0'andcount="11"THEN

in_sel<="11";

shift<="10";

done<='1';

clken<='0';

regclr<='1';

ELSE

in_sel<="XX";

shift<="XX";

done<='0';

clken<='1';

regclr<='1';

ENDIF;

WHENerr=>

IFstart='1'THEN

in_sel<="XX";

shift<="XX";

done<='0';

clken<='1';

regclr<='0';

ELSE

in_sel<="XX";

shift<="XX";

done<='0';

clken<='1';

regclr<='1';

ENDIF;

WHENOTHERS=>

IFstart='1'THEN

in_sel<="XX";

shift<="XX";

done<='0';

clken<='1';

regclr<='0';

ELSE

in_sel<="XX";

shift<="XX";

done<='0';

clken<='1';

regclr<='1';

ENDIF;

ENDCASE;

ENDPROCESSmealy;

moore:

PROCESS(code)

BEGIN

CASEcodeIS

WHENidle=>

state_out<="000";

WHENlsb=>

state_out<="001";

WHENmid=>

state_out<="010";

WHENmsb=>

state_out<="011";

WHENerr=>

state_out<="100";

WHENOTHERS=>

state_out<="000";

ENDCASE;

ENDPROCESSmoore;

ENDlogic;

B4x4乘法器的编程及仿真结果

LIBRARYieee;

USEieee.std_logic_1164.all;

LIBRARYlpm;

USElpm.lpm_components.all;

ENTITYmult4x4IS

PORT

(

dataa:

INSTD_LOGIC_VECTOR(3DOWNTO0);

datab:

INSTD_LOGIC_VECTOR(3DOWNTO0);

result:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDmult4x4;

ARCHITECTURESYNOFmult4x4IS

SIGNALsub_wire0:

STD_LOGIC_VECTOR(7DOWNTO0);

COMPONENTlpm_mult

GENERIC(

lpm_hint:

STRING;

lpm_representation:

STRING;

lpm_type:

STRING;

lpm_widtha:

NATURAL;

lpm_widthb:

NATURAL;

lpm_widthp:

NATURAL;

lpm_widths:

NATURAL

);

PORT(

dataa:

INSTD_LOGIC_VECTOR(3DOWNTO0);

datab:

INSTD_LOGIC_VECTOR(3DOWNTO0);

result:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDCOMPONENT;

BEGIN

result<=sub_wire0(7DOWNTO0);

lpm_mult_component:

lpm_mult

GENERICMAP(

lpm_hint=>"MAXIMIZE_SPEED=5",

lpm_representation=>"UNSIGNED",

lpm_type=>"LPM_MULT",

lpm_widtha=>4,

lpm_widthb=>4,

lpm_widthp=>8,

lpm_widths=>1

)

PORTMAP(

dataa=>dataa,

datab=>datab,

result=>sub_wire0

)

ENDSYN;

C8×8乘法器的顶层电路的实现