《EDA技术及应用》实验书.docx

《《EDA技术及应用》实验书.docx》由会员分享,可在线阅读,更多相关《《EDA技术及应用》实验书.docx(31页珍藏版)》请在冰豆网上搜索。

《EDA技术及应用》实验书

实验一组合逻辑器件设计

一、实验目的

1、通过一个简单的3-8译码器的设计,掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、初步了解QUARTUSII原理图输入设计的全过程。

二、实验主要仪器与设备

1、输入:

DIP拨码开关3位。

2、输出:

LED灯。

3、主芯片:

EP1K10TC100-3。

三、实验内容及原理

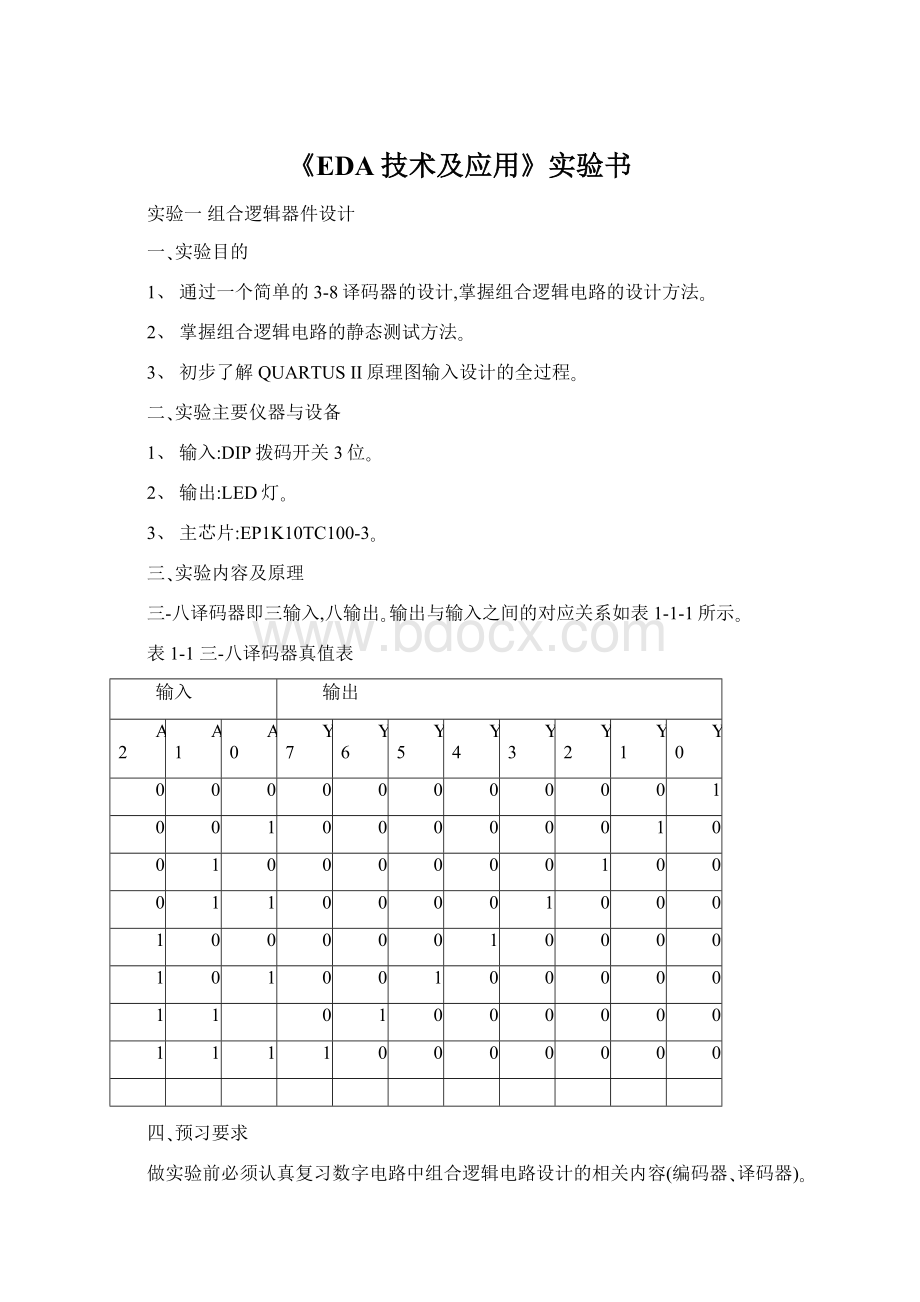

三-八译码器即三输入,八输出。输出与输入之间的对应关系如表1-1-1所示。

表1-1三-八译码器真值表

输入

输出

A2

A1

A0

Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

0

0

0

0

0

0

0

0

0

0

1

0

0

1

0

0

0

0

0

0

1

0

0

1

0

0

0

0

0

0

1

0

0

0

1

1

0

0

0

0

1

0

0

0

1

0

0

0

0

0

1

0

0

0

0

1

0

1

0

0

1

0

0

0

0

0

1

1

0

1

0

0

0

0

0

0

1

1

1

1

0

0

0

0

0

0

0

四、预习要求

做实验前必须认真复习数字电路中组合逻辑电路设计的相关内容(编码器、译码器)。

五、实验步骤

1、利用原理图设计输入法画图1-1-1。

2、选择芯片ACEX1KEP1K10TC100-3。

3、编译。

4、时序仿真。

5、管脚分配,并再次编译。

6、实验连线。

7、编程下载,观察实验结果。

图1-1三-八译码器原理图

六、实验连线

用拨码开关的低三位代表译码器的输入(A,B,C),将之与EP1K10TC100-3的管脚相连;用LED灯来表示译码器的输出(D0~D7),将之与EP1K10TC100-3芯片的管脚相连。拨动拨档开关,可以观察发光二极管与输入状态的对应关系同真值表中所描述的情况是一致的。

七、实验结果

八、思考题

在输入端加入使能端后应如何设计?

附:

用硬件描述语言完成译码器的设计:

:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYT2IS

PORT(

A:

INSTD_LOGIC_VECTOR(2DOWNTO0);

Y:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));

ENDT2;

ARCHITECTUREAOFT2IS

BEGIN

WITHASELECT

Y<="00000001"WHEN"000",

"00000010"WHEN"001",

"00000100"WHEN"010",

"00001000"WHEN"011",

"00010000"WHEN"100",

"00100000"WHEN"101",

"01000000"WHEN"110",

"10000000"WHENOTHERS;

ENDA;

实验二组合电路设计

一、实验目的

1、掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、加深FPGA设计的过程,并比较原理图输入和文本输入的优劣。

二、实验主要仪器与设备

1、输入:

按键开关(常高)4个;拨码开关4位。

2、输出:

LED灯。

4、主芯片:

EP1K10TC100-3。

三、实验内容及原理

1、四舍五入判别电路,其输入为8421BCD码,要求当输入大于或等于5

时,判别电路输出为1,反之为0。原理图如图1-2-1。

图2-1四舍五入判别电路原理图

2、

设计四个开关控制一盏灯的逻辑电路,要求合任一开关,灯亮;断任

一开关,灯灭。原理图如图1-2-2。

图2-2开关控制电路原理图

3、设计一个优先权排队电路,排队顺序:

A=1为最高优先级;B=1为次高优先级;C=1为最低优先级。要求输出端最高只能有一端为“1”,即只能是优先级较高的输入端所对应的输出端为“1”。原理图如图

1-2-3所示。

4、1-2-3。

图2-3优先权排队电路原理图

四、预习要求

做实验前必须认真复习数字电路中组合逻辑电路设计的有关内容(组合电路的设计方法、加法器的设计、三人表决器的设计等)。

五、实验步骤

1、利用原理图设计输入法画图2-1。

2、选择芯片ACEX1KEP1K10TC100-3。

3、编译。

4、时序仿真。

5、管脚分配,并再次编译。

6、实验连线。

7、编程下载,观察实验结果。

同理,完成图2-2、2-3的设计过程。

六、实验连线

1、输入信号D3,D2,D1,D0对应的管脚接四个拨码开关;输出信号OUT对应的管脚接LED灯。

2、输入信号K1,K2,K3,K4对应的管脚接四个按键开关;输出信号OUT对应的管脚接LED灯。拨动按键开关,当按下奇数个按键时,灯亮;当按下偶数个按键时,灯灭。

3、输入信号A、B、C对应的管脚连三个按键开关;输出信号A-OUT,B-OUT,C-OUT对应的管脚分别连三个LED灯。

拨动拨码开关或者按下按键开关,观察LED灯,与实验内容是否相符。

七、实验结果

八、思考题

写对于两种硬件设计输入法的比较。

附:

用硬件描述语言(VHDL)完成3个实验项目的设计:

(1)

LibraryIEEE;

UseIEEE.std_logic_1164.all;

Entityt2_1is

port(D:

Instd_logic_vector(3downto0);

Y:

Outstd_logic);

endt2_1;

Architecturestructoft2_1is

begin

process(D)

begin

if(D>="0101"andD<="1001")then

Y<='1';

elsifD<="0101"then

Y<='0';

else

Y<='Z';

endif;

endprocess;

end;

(2)

LibraryIEEE;

UseIEEE.std_logic_1164.all;

Entityt2_2is

port(D:

Instd_logic_vector(3downto0);

Y:

Outstd_logic);

endt2_2;

Architecturestructoft2_2is

begin

process(D)

begin

caseDis

when"0000"=>Y<='0';

when"0001"=>Y<='1';

when"0011"=>Y<='0';

when"0010"=>Y<='1';

when"0110"=>Y<='0';

when"0111"=>Y<='1';

when"0101"=>Y<='0';

when"0100"=>Y<='1';

when"1100"=>Y<='0';

when"1101"=>Y<='1';

when"1111"=>Y<='0';

when"1110"=>Y<='1';

when"1010"=>Y<='0';

when"1011"=>Y<='1';

when"1001"=>Y<='0';

when"1000"=>Y<='1';

whenothers=>Y<='Z';

endcase;

endprocess;

end;

(3)

LibraryIEEE;

UseIEEE.std_logic_1164.all;

Entityt2_3is

port(A,B,C:

Instd_logic;

Y:

Outstd_logic_vector(2downto0));

endt2_3;

Architecturestructoft2_3is

begin

process(A,B,C)

begin

ifA='1'then

Y<="100";

elsifB='1'then

Y<="010";

elsifC='1'then

Y<="001";

elseY<="000";

endif;

endprocess;

end;

实验三触发器功能模拟

一、实验目的

1、掌握触发器功能的测试方法。

2、掌握基本RS触发器的组成及工作原理。

3、掌握集成JK触发器和逻辑功能及触发方式。

4、掌握几种主要触发器之间相互转换的方法。

5、通过实验,体会FPGA芯片的高集成度和多I/O口。

二、实验主要仪器与设备

1、输入:

按键开关(常高);拨码开关;时钟源。

2、输出:

LED灯。

5、主芯片:

EP1K10TC100-3。

三、实验内容及原理

图3-1四种触发器电路原理图

将基本RS触发器,同步RS触发器,集成J-K触发器,D触发器同时集成在一个CPLD芯片中模拟其功能,并研究其相互转化的方法。

四、预习要求

做实验前必须认真复习数字电路中触发器的相关内容,基本RS触发器,同步RS触发器,J-K触发器,D触发器,T触发器的电路结构及工作原理。

五、实验步骤

1、利用原理图设计输入法画图3-1。

2、选择芯片ACEX1KEP1K10TC100-3。

3、编译。

4、时序仿真。

5、管脚分配,并再次编译。

6、实验连线。

7、编程下载,观察实验结果。

六、实验连线

输入信号Sd,Rd对应的管脚接按键开关,CLK接时钟源(频率<0.5Hz):

输入信号J,K,D,R,S对应的管脚分别接拨码开关;输出信号QRS,NQRS,QRSC,NQRSC,QJK,NQJK,QD,NQD对应管脚分别接LED灯。

另外准备几根连接线,在改变为T“触发”器时,短接相应管脚,或连接“0”“1”电平。

七、实验结果

填下述表一,表二,表三,表四。

表一RS寄存器

Rd

Sd

Q

说明

0

1

1

0

1

1

0

0

表二RS锁存器

R

S

CLK

Rd

Sd

Q

说明

X

X

X

1

0

X

X

X

0

1

X

X

X

0

0

X

X

0

1

1

R

S

CLK

Rd

Sd

说明

0

0

1

1

1

0

1

1

1

1

1

0

1

1

1

1

1

1

1

1

表三JK触发器

J

K

CLK

Rd

Sd

Q

说明

X

X

X

0

1

X

X

X

1

0

X

X

X

0

0

X

X

0

1

1

X

X

1

1

1

J

K

CLK

Rd

Sd

说明

0

0

↑

1

1

0

1

↑

1

1

1

0

↑

1

1

1

1

↑

1

1

表四D触发器

D

CLK

Rd

Sd

Q

说明

X

X

0

1

X

X

1

0

X

X

0

0

X

0

1

1

X

1

1

1

D

CLK

Rd

Sd

Q

NQ

X

↑

1

1

1

↑

1

1

八、思考题

分别将JK触发器和D触发器接成T触发器,模拟其工作状态,并画出其波形。

实验四扫描显示电路设计

一、实验目的

了解教学系统中8位七段数码管显示模块的工作原理,设计标准扫描驱动电路模块,以备后面实验调用。

二、实验主要仪器与设备

1、输入:

时钟源,四位拨码开关。

2、输出:

八位七段数码显示管。

3、主芯片:

EP1K10TC100-3。

三、实验内容及原理

四位拨码开关提供8421BCD码,经译码电路后成为7段数码管的字形显示驱动信号。(A…G)扫描电路通过可调时钟输出片选地址SEL[2..0]。由SEL[2..0]和A..G决定了8位中的哪一位显示和显示什么字形。SEL[2..0]变化的快慢决定了扫描频率的快慢。

1、用拨码开关产生8421BCD码,用FPGA产生字形编码电路和扫描驱动电路,然后进行仿真,观察波形,正确后进行设计实现,适配化分。调节时钟频率,感受“扫描”的过程,并观察字符亮度和显示刷新的效果。参考电路(时钟频率>40HZ,如图4-1)

图4-1

2、编一个简单的从0~F轮换显示十六进制的电路。参考电路(时钟频率<2HZ,如图4-2)

图4-2

四、预习要求

做实验前必须认真复习数字电路中计数器的实现方法,74161的构成及功能,七段显示译码器的实现,以及VHDL编程等相关内容。

五、实验步骤

1、利用VHDL文本输入法设计DELED模块,并生成元件符号。

2、利用原理图设计输入法画图4-1。

3、选择芯片ACEX1KEP1K10TC100-3。

4、编译。

5、仿真。

6、管脚分配,并再次编译。

7、实验连线。

8、编程下载,观察实验结果。

同理,完成图4-2的设计过程。

六、实验连线

输入信号:

D3,D2,D1,D0所对应的管脚同四位拨码开关相连;清零信号RESET所对应的管脚同按键开关相连;时钟CLK所对应的管脚同实验箱上的时钟源相连;

输出信号:

代表扫描片选地址信号SEL2,SEL1,SEL0的管脚同四位扫描驱动地址的低3位相连,最高位地址接“0”(也可悬空);代表7段字码驱动信号A,B,C,D,E,F,G的管脚分别同扫描数码管的段输入a,b,c,d,e,f,g相连。

观察数码管所显示的数字与输入之间的关系。

七、实验结果

八、思考题

1、字形编码的种类,即一个7段数码管可产生多少种字符,产生所有字符需多少根被译码信号线?

2、字符显示亮度同扫描频率的关系,且让人眼感觉不出光烁现象的最低扫描频率是多少?

附:

模块DELED的源代码:

LIBRARYieee;

USEieee.std_logic_1164.ALL;

ENTITYdeledIS

PORT(

a:

INSTD_LOGIC_VECTOR(3DOWNTO0);

y:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDdeled;

ARCHITECTUREaOFdeledIS

BEGIN

withaselect

y<="0111111"when"0000",

"0000110"when"0001",

"1011011"when"0010",

"1001111"when"0011",

"1100110"when"0100",

"1101101"when"0101",

"1111101"when"0110",

"0000111"when"0111",

"1111111"when"1000",

"1101111"when"1001",

"1110111"when"1010",

"1111100"when"1011",

"0111001"when"1100",

"1011110"when"1101",

"1111001"when"1110",

"1110001"when"1111",

"0000000"whenothers;

ENDa;

实验五计数器及时序电路设计

(一)

一、实验目的

1、掌握时序电路的经典设计方法(D触发器和JK触发器和一般逻辑门组成的时序逻辑电路)。

2、掌握通用同步计数器,异步计数器的设计方法。

3、了解用同步计数器通过清零法和置数法得到循环任意进制计数器的方法。

二、实验主要仪器与设备

1、输入:

时钟源。

2、输出:

四位七段数码显示管。

3、主芯片:

EP1K10TC100-3。

三、实验内容及原理

1、用D触发器设计异步四位二进制加法计数器。原理图如图5-1所示。

图5-1

2、用JK触发器设计异步二—十进制减法计数器。原理图如图5-2所示。

图5-2

3、

用74LS161两个宏连接成八位二进制同步计数器。原理图如图5-3所示。

图5-3

四、预习要求

做实验前必须认真复习数字电路中计数器的实现方法,74161的构成及功能,七段显示译码器的实现,以及硬件描述语言编程等相关内容。

五、实验步骤

1、利用VHDL文本输入法设计DELED模块,并生成元件符号。

2、利用原理图设计输入法画图5-1。

3、选择芯片ACEX1KEP1K10TC100-3。

4、编译。

5、仿真。

6、管脚分配,并再次编译。

7、实验连线。

8、编程下载,观察实验结果。

同理,完成图5-2、5-3的设计过程。

六、实验连线

输入信号:

清零信号RESET所对应的管脚同按键开关相连;计数时钟CLK、扫描时钟CKDSP所对应的管脚同实验箱上的时钟源相连(计数时钟频率CKCNT<4Hz,扫描时钟频率CKDSP>40Hz);

输出信号:

代表扫描片选地址信号SEL2,SEL1,SEL0的管脚同四位扫描驱动地址的低3位相连,最高位地址接“0”(也可悬空);代表7段字码驱动信号A,B,C,D,E,F,G的管脚分别同扫描数码管的段输入a,b,c,d,e,f,g相连。

七、实验结果

八、思考题

在FPGA设计中,同步设计和异步设计有何不同。

附:

模块sh8_4的源代码

LIBRARYieee;

USEieee.std_logic_1164.ALL;

ENTITYsh8_4IS

PORT(sel:

INSTD_LOGIC;

da:

INSTD_LOGIC_VECTOR(7DOWNTO0);

q:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDsh8_4;

ARCHITECTUREaOFsh8_4IS

BEGIN

Process

begin

Ifsel=’0’Thenq<=da(3DOWNTO0);

Elseq<=da(7DOWNTO4);

Endif;

Endprocess;

ENDa;

实验六计数器及时序电路设计

(二)

一、实验目的

1、理解时序电路和同步计数器加译码电路的联系,设计任意编码计数器。

2、了解同步芯片和异步芯片的区别。

二、实验主要仪器与设备

1、输入:

时钟源。

2、输出:

四位七段数码显示管。

3、主芯片:

EP1K10TC100-3。

三、实验内容及原理

用74LS161清零和置数法组成六进制和十二进制计数器。原理图如图6-1所示。计数时钟频率CKCNT<0.5HZ,扫描时钟频率CKDSP>40HZ;清零法分别完成0~4、0~B的顺序计数;置位法分别完成3~9、3~F的顺序计数;用八位数码管显示四个计数状态。

图6-1

四、预习要求

做实验前必须认真复习数字电路中计数器的实现方法,74161的构成及功能,七段显示译码器的实现,以及VHDL编程等相关内容。

五、实验步骤

1、利用VHDL文本输入法设计DELED、HB1、HB2、HB3、HB4、SEL4模块,并生成相应的元件符号。

2、利用原理图设计输入法画图6-1。

3、选择芯片ACEX1KEP1K10TC100-3。

4、编译。

5、仿真。

6、管脚分配,并再次编译。

7、实验连线。

8、编程下载,观察实验结果。

六、实验连线

输入信号:

清零信号RESET所对应的管脚同按键开关相连;计数时钟CLK、扫描时钟CKDSP所对应的管脚同实验箱上的时钟源相连;

输出信号:

代表扫描片选地址信号SEL2,SEL1,SEL0的管脚同四位扫描驱动地址的低3位相连,最高位地址接“0”(也可悬空);代表7段字码驱动信号A,B,C,D,E,F,G的管脚分别同扫描数码管的段输入a,b,c,d,e,f,g相连。

七、实验报告与思考题

1、写出实验步骤和实验结果

2、用74161实现任意进制计数器的方法。

3、状态机的VHDL实现代码。

4、体会同步设计和异步设计的不同之处。

附:

各模块的VHDL代码

LIBRARYieee;

USEieee.std_logic_1164.ALL;

ENTITYhb1IS

PORT(d:

INSTD_LOGIC_VECTOR(3DOWNTO0);

out1:

OUTSTD_LOGIC);

ENDhb1;

ARCHITECTUREaOFhb1IS

BEGIN

process

begin

Ifd>"0100"Thenout1<='0';

Elseout1<='1';

Endif;

endprocess;

ENDa;

LIBRARYieee;

USEieee.std_logic_1164.ALL;

ENTITYhb2IS

PORT(d:

INSTD_LOGIC_VECTOR(3DOWNTO0);

out1:

OUTSTD_LOGIC);

ENDhb2;

ARCHITECTUREaOFhb2IS

BEGIN

process

begin

Ifd>"1001"ord<"0011"Thenout1<='0';

Elseout1<='1';

Endif;

endprocess;

ENDa;

LIBRARYieee;

USEieee.std_logic_1164.ALL;

ENTITYhb3IS

PORT(d:

INSTD_LOGIC_VECTOR(3DOWNTO0);

out1:

OUTSTD_LOGIC);

ENDhb3;

ARCHITECTUREaOFhb3IS

BEGIN

process

begin

Ifd>"1011"Thenout1<='0';

Elseout1<='1';

Endif;

endprocess;

ENDa;

LIBRARYieee;

USEieee.std_logic_1164.ALL;

ENTITYhb4IS

PORT(d:

INSTD_LOGIC_VECTOR(3DOWNTO0);

out1:

OUTSTD_LOGIC);

ENDhb4;

ARCHITECTUREaOFhb4IS

BEGIN

process

begin

Ifd="1111"ord<"0011"Thenout1<='0';

Elseout1<='1';

Endif;

endprocess;

ENDa;

LIBRARYieee;

USEiee