DSP原理与应用技术考试知识点总结太原理工大学13届葬仪落任影汐整理.docx

《DSP原理与应用技术考试知识点总结太原理工大学13届葬仪落任影汐整理.docx》由会员分享,可在线阅读,更多相关《DSP原理与应用技术考试知识点总结太原理工大学13届葬仪落任影汐整理.docx(20页珍藏版)》请在冰豆网上搜索。

DSP原理与应用技术考试知识点总结太原理工大学13届葬仪落任影汐整理

第一章

1、DSP系统的组成:

由控制处理器、DSPs、输入/输出接口、存储器、数据传输网络构成。

P2图1-1-1

2、TMS320系列DSPs芯片的基本特点:

哈佛结构、流水线操作、专用的硬件乘法器、特殊的DSP指令、快速的指令周期。

3、哈佛结构:

是一种将程序指令储存和数据储存分开的储存器结构。

特点:

并行结构体系,是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址,独立访问。

系统中设置了程序和数据两条总线,使数据吞吐率提高一倍。

4、TMS320系列在哈佛结构之上DSPs芯片的改进:

(1)允许数据存放在程序存储器中,并被算数运算指令直接使用,增强芯片灵活性

(2)指令储存在高速缓冲器中,执行指令时,不需要再从存储器中读取指令,节约了一个指令周期的时间。

5、冯诺依曼结构:

将指令、数据、地址存储在同一存储器中,统一编址,依靠指令计数器提供的地址来区分是指令、数据还是地址,取指令和去数据都访问同一存储器,数据吞吐率低。

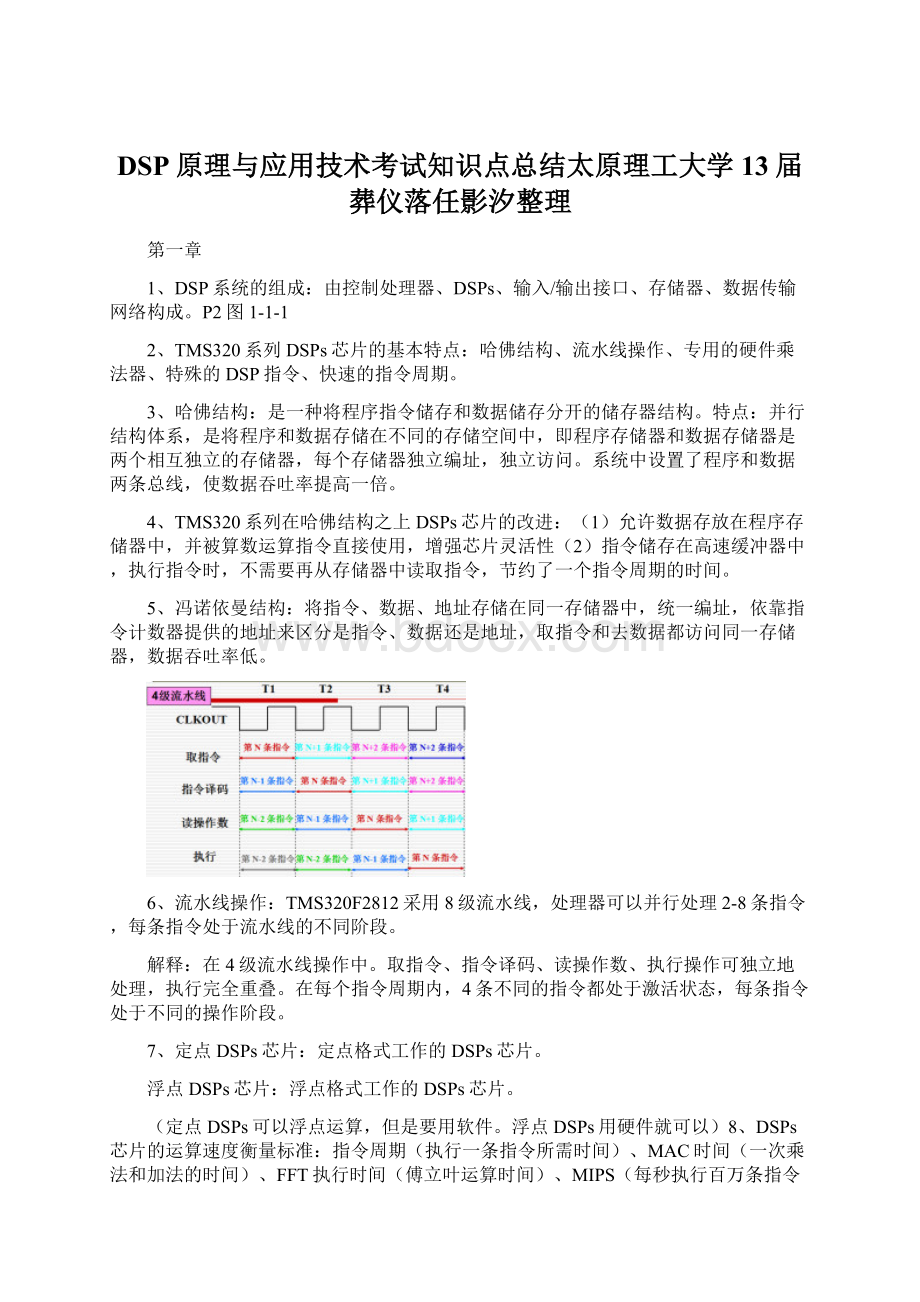

6、流水线操作:

TMS320F2812采用8级流水线,处理器可以并行处理2-8条指令,每条指令处于流水线的不同阶段。

解释:

在4级流水线操作中。

取指令、指令译码、读操作数、执行操作可独立地处理,执行完全重叠。

在每个指令周期内,4条不同的指令都处于激活状态,每条指令处于不同的操作阶段。

7、定点DSPs芯片:

定点格式工作的DSPs芯片。

浮点DSPs芯片:

浮点格式工作的DSPs芯片。

(定点DSPs可以浮点运算,但是要用软件。

浮点DSPs用硬件就可以)8、DSPs芯片的运算速度衡量标准:

指令周期(执行一条指令所需时间)、MAC时间(一次乘法和加法的时间)、FFT执行时间(傅立叶运算时间)、MIPS(每秒执行百万条指令)、MOPS(每秒执行百万次操作)、MFLOPS(每秒执行百万次浮点操作)、BOPS(每秒十亿次操作)。

9、TMS320F281x系列芯片主要性能:

(1)低功耗设计(核心电压1.8V,I/O电压3.3V)

(2)高性能的32位中央处理器:

可达4兆字的线性程序地址,可达4兆字的线性数据地址

(3)3个外部中断128位的密钥,3个32位的CPU定时器

(4)串口外围设备(串行外围接口SPI,两个串行通信接口SCIs,标准的UART,改进的局域网络eCAN,多通道缓冲串行接口McBSP和串行外围接口模式)

(5)最多有56个独立的可编程、多用途通用输入/输出(GPIO)引脚。

10、TMS320F2812是TI推出的新一代32位定点DSPs芯片。

第二章

1、TMS320F2812是32位定点DSPs芯片。

2、TMS320C28x系列芯片有三个主要部分:

中央处理单元(CPU),存储器,片内外设。

CPU负责控制程序的流程和指令的处理,可执行算术运算、布尔逻辑、乘法和位移操作。

(CPU组成:

产生数据和程序存储地址的CPU,仿真逻辑,各种信号线)

3、TMS320C28x的CPU是一种低功耗的32位定点数字信号处理器,优秀特性:

哈佛结构和循环寻址方式、精简指令系统、字节的组合和拆分、位操作。

4、CPU的主要特性:

(1)保护流水线

(2)独立寄存器空间(3)算术逻辑单元(4)地址寄存器算术单元(5)循环移位器(6)乘法器利用改进型哈佛结构可以并行地执行指令和读取数据。

5、C28x芯片具有3种操作模式:

C27x目标-兼容模式、C28x模式及C2xLP源-兼容模式。

C27x目标-兼容模式在复位时,C28x的CPU处于C27x目标-兼容模式。

6、CPU有4种主要信号的名称和功能

(1)存储器接口信号:

在CPU、存储器和外围设备之间进行数据传送;进行程序存储器的访问和数据存储器的存取;并能根据不同的字段长度区分不同的存取操作(16位或32位)

(2)时钟和控制信号:

为CPU和仿真逻辑提供时钟,可以用来控制和监视CPU状态。

(3)复位和中断信号:

用来产生硬件复位和中断,并用来监视中断的状态。

(4)仿真信号:

用来进行测试和调试。

7、CPU的主要单元:

程序和数据逻辑控制、实时仿真逻辑、地址寄存器算术单元(ARAU)、算术逻辑单元(ALU)、预取队列和指令译码、程序和数据地址发生器、定点MPY/ALU、中断处理。

8、存储器接口3条地址总线:

(1)PAB(程序地址总线),传送程序空间的读/写地址,是一个22位的总线,寻址空间4M。

(2)DRAB(数据读地址总线)32位,传送来自数据空间的读地址。

(3)DWAB(数据写地址总线)32位,传送来自数据空间的写地址。

9、存储器接口3条数据总线:

(1)PRDB程序读数据总线32位,在读取程序空间时用来传送指令或数据。

(2)DRDB数据读数据总线32位,在读取数据空间时用来传送数据。

(3)DWDB数据/程序写数据总线32位,在对数据空间写数据时用来传送数据。

(注意:

程序空间的读和写不能同时发生,因为它们都要使用程序地址总线PAB。

程序空间的写和数据空间的写也不能同时发生,因为两者都要使用数据/程序写数据总线DWDB。

)

10、数据页指针(DP):

在直接寻址模式中,对数据存储器的寻址要在64个字的数据页中进行。

由低4M字的数据存储器组成65536个数据页,用0~65535进行标号。

16位指针。

当CPU工作在C2xLP源-兼容模式时,使用一个7位的偏移量,并忽略DP寄存器的最低位。

堆栈指针(SP):

允许在数据存储器中使用软件堆栈。

堆栈指针SP为16位,可以对数据空间的低64K(216)进行寻址。

当使用SP时,将32位地址的高16位置为0(SP高16位不可操作)。

复位后SP指向地址00000400H。

(堆栈:

1.堆栈从低地址向高地址增长。

2.SP总是指向堆栈中的下一个空域。

3.复位时,SP被初始化,它指向地址00000400H。

4.将32位数值存入堆栈时,先存入低16位。

5.当读写32位的数值时,C28xCPU期望存储器或外设接口逻辑把读/写排成偶数地址。

6.如果增加SP的值,使它超过FFFFH,或者减少SP的值,使它低于0000H,则表明SP已经溢出。

当数值存入堆栈时,SP并不要求排成奇数或偶数地址。

排列由存储器或外设接口逻辑完成。

)

程序计数器(PC):

当流水线满时,22位的程序指针总是指向流水线中到达译码的第2阶段的指令。

一旦指令到达了流水线译码的第2阶段,它就不会再被中断从流水线中清除掉,而是在中断执行之前就被执行了。

11、状态寄存器1(ST1):

VMAP,位3,向量映射位,VMAP决定CPU的中断向量(包括复位向量)被映射到程序存储器的最低地址还是最高地址。

0:

CPU的中断向量映射到程序存储器的底部,地址是000000h-0003FFh。

1:

CPU的中断向量映射到程序存储器的上部,地址是3FFFC0h-3FFFFFh。

可使用SETCVMAP和CLPCVMAP指令对该位进行置位和清0,复位时VMAP被置位。

12、解释物理程序

X1/XCLKIN振荡器输入信号

X2振荡器输出信号

XF_XPLLDIS锁相环使能信号(选择系统时钟源)

OSC振荡器

SYSCLKOUT系统时钟

CLKIN外部时钟

13、解释物理意义:

XF_PLLDIS(选择系统时钟源)当使用内部振荡器,在X1和X2之间连接石英晶体,使用外部振荡器,输入时钟信号接在X1,X2悬空。

14、PLL被禁止:

当

则PLL被禁止,SYSCLKOUT=XCLKIN

PLL被旁路:

PLL被旁路,SYSCLKOUT=XCLKIN/2

PLL使能:

使能PLL,在PLLCR寄存器中写入一个非零值n

SYSCLKOUT=(XCLKIN*n)/2

15、F2812器件上3个32位CPU定时器(TIMER0/1/2)

16、设系统时钟SCLKOUT,xmHz,计数器走一步需多长时间?

CPU定时器一个周期

溢出频率:

17、看门狗作用:

(1)防止程序“跑飞”或进入死循环

(2)程序“跑飞”或死循环后,定时器发出复位信号。

喂狗:

不希望产生脉冲信号,需屏蔽计数器或用软件周期性地向看门狗复位控制寄存器写“0x55+0xAA”。

3个事件都可以使看门狗产生脉冲信号:

(1)未及时“喂狗”使8位看门计数器溢出,受看门屏蔽位的控制

(2)错误的“喂狗”方式(未正确对看门狗复位控制寄存器写入“0x55+0xAA”)(3)对看门狗控制寄存器(WDCR)的WDCHK(2:

0)位写入的不是“1,0,1”。

18、喂狗周期公式:

第三章

1、C28x芯片具有32位数据地址和22位程序地址,总地址空间可达4G字节的数据空间和4M字节的程序空间。

2、片内SARAM的共同特点:

(1)每个存储器块都可以被单独访问

(2)每个存储器块都可映射到程序空间或数据空间,用以存放指令代码或存储数据变量。

(3)每个存储器块在读/写访问时都可以全速运行,即等待状态为零等待。

片内SARAM的各自特点:

(1)复位时,自动将堆栈指针SP设置在M1块的顶部地址400h处。

(2)L0和L1受到代码安全模块的保护。

DARAM:

片内双访问存储器,每个机器周期可被访问两次存储器。

3、片上OTP:

一次性可编程存储器,只能编程一次,不能擦除。

4、F2812CPU采用32位格式访问储存器或外设时,分配的地址必须是偶地址。

如果操作的是奇地址,则CPU操作奇地址之前的偶地址。

5、F2812处理器的外部接口(XINTF)映射到5个独立的存储区域,使用三个片选信号。

6、外部存储器接口能配置各种参数,尽量不要将配置程序放在XINTF扩展的存储器空间中执行。

7、外设接口提供一个时钟输出XCLKOUT,所有外部接口的访问都是在XCLOCK的上升沿开始。

8、对XINTF空间的读/写操作的时序都可分为三个阶段:

建立(Lead)、激活(Active)和跟踪(Trail)。

(1)在建立阶段,访问空间的片选信号为低电平有效,产生的地址放在地址总线上。

(2)激活阶段。

F2812访问外部设备读操作:

读信号XRD低电平有效,数据锁存到DSPs中写操作:

写信号XWE低电平有效,DSPs数据放到数据总线上(3)跟踪阶段。

读/写信号(XRD/WE)变为高电平,而使片选信号仍然保持为低电平的一段时间。

9、理解图的意义:

SYSCLKOUT和XCLKOUT的关系

所有的外部扩展访问都是以内部XINTF的时钟XTIMCLK为参考的,因此在配置XINTF时,首先要通过XINTCNF2寄存器配置XTIMCLK。

XTIMCLK可以配置为两种情况:

SYSCLKOUT或者SYSCLKOUT/2(默认值)。

外部接口还提供一个时钟输出信号XCLKOUT,所有外部接口的访问都是在XCLKOUT的上升沿开始,可以通过XINTCNF2寄存器的CLKMODE位配置XCLKOUT的频率。

10、XREADY信号检测方式:

同步检测,XREADY信号在激活状态结束前的一个XTIMCLK信号上升沿被采样;异步检测,XREADY信号在激活状态结束前的倒数第三个XTIMCLK信号上升沿时被采样。

11、GPIO:

当某个引脚被配置成数字I/O时,引脚相应的外设功能(包括中断)必须被禁止。

如采样窗口是6个采样周期宽度,那么只有6个采样数据相同时输出才会改变。

作用:

这个功能可以有效地消除毛刺脉冲对输入信号的干扰(抗干扰)。

12、解释:

如果采样窗口是六个采样周期宽度,那么只有当6个采样数据相同时输出才会改变,有效消除毛刺脉冲对输入信号的影响。

第四章

1、可屏蔽中断:

这些中断可以用软件禁止或使能。

不可屏蔽中断:

这些中断不能被禁止。

CPU将立即响应这类中断并执行相应的中断服务子程序。

所有软件的激发都属于不可屏蔽中断。

2、C28x系列芯片支持32个CPU级中断向量,包括复位向量。

每个向量是一个22位的地址,该地址是相应中断服务程序(ISR)的入口地址。

每个向量被保存在两个地址连续的存储器单元中(每个存储单元为16位,两个共32位)。

其中,该空间的低地址保存向量的低16位(LSBs),其高地址则以右对齐保存向量的高6位(MSBs)。

3、清楚中断向量号和中断向量

4、VMAP功能:

向量表可以映像到程序空间的底部或顶部,这取决于状态寄存器STI中的向量映射位VMAP,如果VMAP为使0,向量就映像在以000000h开始的地址上,如果其值是1,向量就映像到以3FFFC0h开始的地址上。

VMAP位可以由SETCVNAP指令置1,由CLRCVMAP清0。

VMAP的复位值是1。

5、C28x不可屏蔽中断包括:

(1)软中断(INTR和TRAP指令)

(2)硬件中断

(3)非法指令陷阱(4)硬件复位中断(

)

6、复位操作:

当复位输入信号

产生后,CPU就会进入一个确定状态。

CPU将放弃所有当前操作,清空流水线,并且CPU的寄存器进行复位,然后取出RESET中断向量,从而执行相应的中断服务程序。

寄存器

位

复位后的值

说明

DP

所有

0000h

DP指向数据页

PC

所有

3FFFC0h

PC由地址000000h或3FFFC0h的复位中断向量赋值

SP

所有

0400h

SP指向地址0400h

7、PIE:

每个组有8个中断,每个组都被反馈到CPU内核的12条中断信号线的一条上,从而使整个PIE模块支持96个不同的中断。

C28xCPU支持17个CPU级硬件中断。

非复用中断源直接反馈给CPU。

8、整个系统的中断分为3级:

(1)外设级中断

某个外设产生中断时,与该事件相关的中断标志(IF)位会在这个外设的寄存器中置为1。

如果相应的中断使能(IE)位已经置位,则外设向PIE控制器产生一个中断请求。

如果该中断在外设级使能无效,则相应的IF位会一直保持直到用软件清除它为止。

如果在以后使能该中断,且中断标志仍然置位,那么就会向PIE发出一个中断请求。

外设寄存器中的中断标志必须采用软件清除。

(2)PIE级中断

PIE复用了8个外设和外部中断引脚向CPU申请中断。

这些中断被划分为12个组:

PIE组1~PIE组12,1个组中的中断被多路复用进入1个CPU中断。

与CPU剩余的中断相连接的中断源不是多路复用的。

对于非多路复用的中断而言,PIE直接向CPU传送中断请求。

对于多路复用的中断源,PIE块中的每个中断组都有一个相关标志位PIEIFRx.y和使能位PIEIERx.y。

每个中断组(1NT1~INTl2)都有一个应答位PIEACKx。

(3)CPU级中断

一旦某个中断请求被送往CPU,CPU级中与INTx相关的中断标志(IFR)位就被置位。

该标志位被锁存在IFR后,CPU不会马上就去执行相应的中断,而是等待CPU使能IER寄存器,或者使能DBGIER寄存器,并对全局中断屏蔽位INTM进行适当的使能。

9、物理含义:

上面第二部分。

10、从外设到CPU的多路复用中断请求流程

(1)任何PIE组里的外设和外部中断产生一个中断,加入外设中断已被使能,那么,该中断要求就被置入PIE模块

(2)PIE模块识别PIE组x内已经录入的中断y(INTx.y),并且将相应的PIE中断标志位锁存:

PIEIFRx.y=1。

(3)为了使能从PIE到CPU的中断,必须设置相应的中断使能位(PIEIERx.y=1),同时所在PIE组的PIEACK.x位必须清0。

(4)如果步骤(3)中的两个条件为真,那么就在CPU建立了一个中断要求,相应位将再次被置位(PIEACK.x=1)。

PIEACK.x位将一直保持置位直至清除该位(表示来自该组的其他中断能够从PIE传送至CPU)。

(5)CPU中断标志位置位(CPUIFRx=1)以表示一个CPU级的未响应中断x。

(6)加入CPU中断能被使能(CPUIERbitx=1或DBGIERbitx=1),全局中断屏蔽被清除(INTM=0),那么CPU将为INTx服务。

(7)CPU识别这个中断并自动存放有关信息,清除IER位,设置INTM,清除EALLOW。

(8)CPU从PIE获得适当的向量。

(9)对于复用中断,PIE模块使用PIEIERx和PIEIFRx寄存器中的当前值来确定要使用的向量地址:

该组中最高优先级中断的向量被取出,并且被用作分支地址。

这个中断在PIEIERx寄存器中使能,在PIEIFRx中标示为未响应的中断。

在这种情况下,假如一个更高优先级的已使能中断在步骤4之后被标示,它就会首先得到服务;如果该组中没有已经标示的中断被使能,那么PIE将响应该组中最高优先级的中断向量,即用INTx.1作为分支地址,这种操作相当于执行28x的TRAP或INT指令。

从而PIEIFRx.y位被清除,CPU转到从PIE取出的中断向量里去执行。

11、F2812支持3个外部可屏蔽中断:

XINT1,XINT2,XINT13

第五章

1、TMS320F2812芯片内部集成诸多片内外设,主要有:

系统控制(包括存储器、时钟、低功耗模块、看门狗、CPU定时器、GPIO和外设帧等)、外设中断扩展(PIE)、外部接口扩展(XINTF)、引导模块(BootROM)、时间管理器(EV)、串行通信接口(SCI)、串行外设接口(SPI)、eCAN总线模块、多通道缓冲串行口(McBSP)和模数转换模块(ADC)等。

2、F2812提供了两个具有相同结构和功能的事件管理器模块EVA和EVB。

作用:

多电机控制。

每个事件管理器模块都包含通用定时器。

全比较/PWM单元、捕获单元及正交编码脉冲电路。

EVA/EVB可分别提供8个PWM信号。

3、通用定时器功能:

在控制系统中产生采样周期,为捕获单元、正交编码电路、比较单元和PWM产生电路提供时基。

(1)定时

(2)产生PWM波形(3)为其他模块提供时钟

4、通用计时器(16位)用于4个可屏蔽中断(上溢、下溢、定时器比较和周期中断)的控制和中断逻辑。

5、通用定时器外部时钟TCLKINA/B,最大频率是CPU时钟频率的1/4。

6、通用定时器作用:

(1)定时

(2)产生PWM波形(3)为其它模块提供时钟

7、通用定时器的工作方式:

(1)停止/保持模式:

通用定时器的操作停止并保持当前状态,定时器的计数器、比较输出和预定标计数器均保持不变。

(2)连续递增计数模式:

通用定时器按照预定标的输入时钟计数,当计数器的值与周期寄存器的值匹配时,在下一个输入时钟的上升沿,通用计数器复位为0,并开始另一个计数周期。

计数器的初值可以为0~FFFFH中的任一个。

(3)定向增/减计数模式

通用定时器在定标的输入时钟上升沿开始计数,计数方向由输入引脚TDIRA/B确定:

引脚为高时,递增计数,与连续增计数模式相同;引脚为低时,递减计数,从初值递减直到为0,此时若TDIRA/B引脚仍为低,计数器将重新载入周期寄存器的值,并继续计数。

(4)连续增/减计数模式。

这种模式与定向增/减计数模式基本相同。

区别是:

计数方向不再受引脚TDIRA/B的控制,而是在计数值达到周期寄存器的值时或FFFFH(初值大于周期寄存器的值)时,才从增计数变为减计数,而在计数值为0时,从减计数变为增计数。

8、通用定时器的比较操作

每个通用定时器都有一个相应的比较寄存器TxCMPR和一个PWM输出引脚TxPWM。

通用定时器的值总是与相应的比较寄存器的值进行比较,当二者相等时,就产生比较匹配事件。

通过将TxCON的TECMPR=1(D1位)来使能比较操作。

目的:

产生PWM,通用定时器可提供4个PWM输出TxPWM。

非对称和对称波形发生器:

在连续增/减计数模式时,产生对称波形(计数操作开始前为0(低电平)、保持不变直到第1次比较匹配发生、第1次比较匹配时,切换输出为高电平、保持不变直到第2次比较匹配第2次比较匹配时,再次切换输出为低电平、保持不变直到周期结束);在连续增计数模式时,产生非对称波形(计数操作开始前为0(低电平)保持不变直到比较匹配发生(TxCNT<TxCMPR)在比较匹配时切换输出状态为1(高电平有效)(TxCNT=TxCMPR)直到当前计数周期结束,输出电平保持不变(TxCNT=TxPR)如果下一周期新的比较寄存器的值不是0,则在匹配周期结束后复位为0)。

PWM引脚的电平跳变:

GPTCONA/B寄存器中的极性选择位设置、定时器的计数操作模式、当选择连续递增、减模式时的计数方向

9、占空比公式:

6、每一个事件管理器可以同时产生8路PWM信号,包括3对由圈比较单元产生的带有可编程死区的PWM信号和由定时器比较器产生的2路独立的PWM信号。

7、EV有6个捕获单元。

8、物理意义:

上升沿比另一个早1/4周期即为先导序列。

QEP1为先导序列,DIR为低,减计数;QEP2为先导序列,DIR为高,增计数。

9、SCI口主要作用:

与多种具有标准异步串口的设备进行通信;当系统中有多个处理器同时工作时,SCI口可作为多处理器间进行通信协调的通道。

SCI模块可以对接收到的数据进行间断、奇偶性、溢出和帧错误检测。

SCI模块的主要特点包括:

数据字格式(1个起始位;1-8个可编程数据字长度;可供选择的奇、偶或无校验模式;1-2个停止位)、发送和接受可以通过中断或查询两种形式、具有16级发送/接受FIFO。

SCI一般的数据发送格式为:

1个起始位;1-8个数据位;1个奇、偶或无校验位;1-2个停止位。

10、SPI主要应用于处理器与EEPROM、Flash、实时时钟、AD转换器等外设器件之间的通信,通过SPI的主从模式也可以支持多处理器间的通信。

SPI接口可以接收或发送16位数据,并且接收和发送都是双缓冲。

发送和接受可同步操作。

(发送功能可通过软件禁用)

SPI有主/从两种工作模式,其工作模式的选择及SPICLK信号由MASTER/SLAVE位(SPICTL.2)控制。

一方面,主控制器可在任何时刻通过发送SPICLK信号来启动数据传输。

另一方面,由软件决定主控制器如何检测从控制器准备好发送数据的时间。

主从控制器的连接的物理意义。

11、eCAN模块具有32个完全可配置邮箱和时间标记功能,能够实现灵活、可靠的串行通信。

12、eCAN模块的结构主要由CAN协议内核(CPK)和消息控制器组成。

CPK有两个功能,一是根据CAN协议对CAN总线上接收到的所有消息进行译码丙存入接收缓冲器;二是根据CAN协议吧消息发送到CAN总线上。

12、消息控制器功能:

消息控制器包含三部分:

存储器管理单元(CPU接口、接收控制单元额定时器管理单元);可以存储32位消息的邮箱RAM;控制和状态寄存器。

消息控制器可以对CPK收到的消息进行判断丙决定是否为CPU保存在邮箱RAM中。

消息控制根据消息的优先级将消息发送给CPK或将CPK中的消息发送给CPU。

消息控制器在初始化时,CPU根据应用程序设定消息控制器所有用到的消息标志符。

4.F2812芯片的多通道缓冲串行口(McBSP),为DSP和系统其他设备之间提供了UI个直接的串行接口。

McBSP可实现与兼容的McBSP设备之间进行通信,此外McBSP还能同步的发送、接收8/16/32位串行数据。

13、CAN协议支持4种数据帧格式:

数据、远程、错误、过载帧。

14、F2812芯片的多通道缓冲串行口McBSP,为DSP和系统其他设备之间提供了一个直接的串行接口。

McBSP可以实现与兼容的McBSP设备之间的通信(VBAP语音频带音频处理器、AIC、多媒体数字信号编码器/解码器)McBSP还可以同步发送、接收8/16/32位串行数据

15、TMS320F28x的片内ADC是一个分辨率为12位且具有流水线