计算机组成原理课程设计报告wangweisheng.docx

《计算机组成原理课程设计报告wangweisheng.docx》由会员分享,可在线阅读,更多相关《计算机组成原理课程设计报告wangweisheng.docx(40页珍藏版)》请在冰豆网上搜索。

计算机组成原理课程设计报告wangweisheng

计算机组成原理课程设计报告

专业名称:

计算机科学与技术

班级学号:

计算机0802

学生姓名:

指导教师:

设计时间:

2010年06月28日——2010年07月01日

2010年07月

第一天取操作数微程序的设计和调试

一、设计目标

设计并调试取操作数的微程序

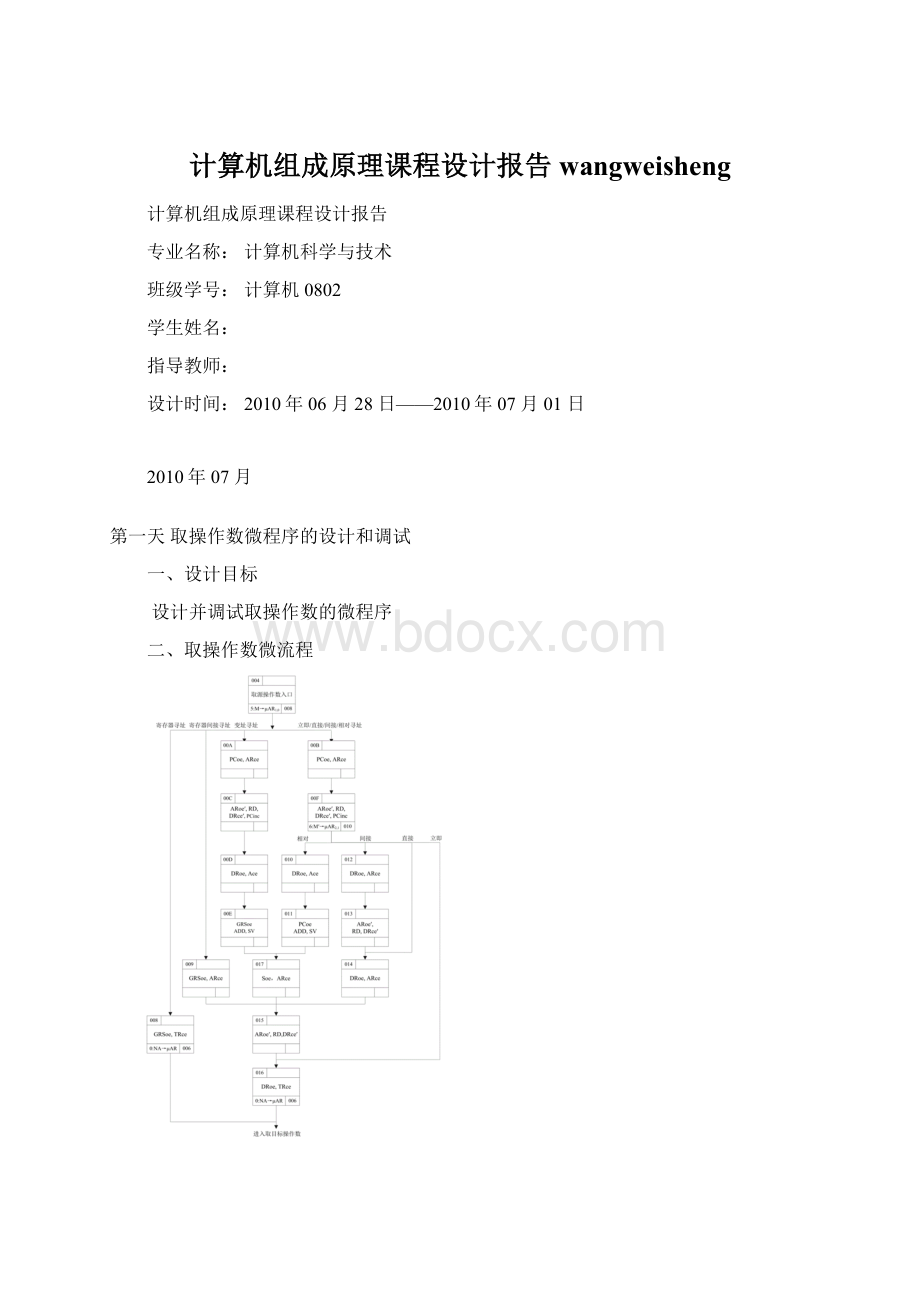

二、取操作数微流程

三、测试程序、数据及运行结果

格式如下:

1、测试内容:

立即数寻址、直接寻址、间接寻址、相对寻址、寄存器寻址

立即寻址测试指令(或程序):

MOV#1234H,R1

机器码:

内存地址(H)

机器码(H)

汇编指令

0000

07611234

MOV#1234H,R1

运行结果及分析:

为了分析微程序是否正确,首先通过查看微指令流程判断BM和NC是设置是否正确,如果执行的微指令依次是:

001——002——003——004——00B——00F——016——006——018——007——。

。

。

(后面的MOV指令的EXE微指令是由老师提供的),根据前面指令微流程的设计,所执行的微指令次序是正确的。

在上图中,测试指令微程序最后一条微指令的地址为046,微指令是88000000,所代表的微操作应该是TRoe,GRSce。

执行后CRS=0000,好像出错了。

但是我们看到在下一条微指令时GRS=1234,赵老师在上实验课的时候曾经讲过这个问题,这是因为GRS的装入使能信号GRSce受时钟信号的影响,内容在微指令周期结束时才被保存,所以观察到的数据慢了一步。

直接寻址测试指令(或程序):

MOV0014H,R1

机器码:

内存地址(H)

机器码(H)

汇编指令

0000

07611234

MOV0014H,R1

运行结果及分析:

为了分析微程序是否正确,首先通过查看微指令流程判断BM和NC是设置是否正确,如果执行的微指令依次是:

001——002——003——004——00B——00F——014——015——016——006——018——007——。

。

。

根据前面指令微流程的设计,所执行的微指令次序是正确的。

间接寻址测试指令(或程序):

MOV(0014),R1

机器码:

内存地址(H)

机器码(H)

汇编指令

0000

07211234

MOV(0014),R1

运行结果及分析:

为了分析微程序是否正确,首先通过查看微指令流程判断BM和NC是设置是否正确,如果执行的微指令依次是:

001——002——003——004——00B——00F——012——0013——014——015——016——006——018——007。

。

。

根据前面指令微流程的设计,所执行的微指令次序是正确的。

测试指令(或程序):

MOVdisp(0014),R1

机器码:

内存地址(H)

机器码(H)

汇编指令

0000

07011234

MOV+disp,R1

运行结果及分析:

为了分析微程序是否正确,首先通过查看微指令流程判断BM和NC是设置是否正确,如果执行的微指令依次是:

001——002——003——004——00B——00F——010——011——017——015——016——006——018——007。

。

。

根据前面指令微流程的设计,所执行的微指令次序是正确的。

由于时间关系,今天只验证了5种寻址方式。

后面两种寻址方式的指令和编码如下所示:

寄存器间接寻址MOV#1234H,(R1)指令编码为07691234

寄存器变址寻址MOV#1234H,disp(R1)指令编码为07711234

四、设计中遇到的问题及解决办法

遇到的问题:

1.搞不清楚‘取操作数入口’的微程序是由什么组成。

2.对软件UniDebugger的操作不太熟悉。

3.以为只需要将取源操作数的微程序输入到micro中就行了。

解决的办法:

1:

一时搞不清楚去源操作数的入口的微程序究竟是要填什么,便不和它纠缠,往下看的时候,看到图中的都填满了微命令,便知道了,原来取操作数的入口的微命令是空的(NOP)。

2:

认真地回忆了做实验的时候的上机步骤后,对该软件的基本操作基本熟悉,然后按照课程设计指导书上的要求便能更好地运用该软件。

3:

MOV指令为双操作数指令。

原本以为该指令虽然是双操作数指令,但应该只涉及到取源操作数,至于目的操作数,该指令应该只是将源操作数输送到目的地址中,取不取目的操作数不影响问题的。

但是很快,我就意识到这个认识是错误的了。

因为在我执行该MOV指令的时候,程序竟然运行到0018处。

这个微指令地址应该出现在取目的操作数阶段,但是我却没有将取目的操作数的微指令编码输入micro中,导致程序运行到该行后输出地微指令编码是00000000。

当然运行结果肯定是错误的。

于是我毫不犹豫地将取目的操作数的微指令编码全都输入到micro中,然后再次运行MOV指令,这一次运行结果就正确了。

第二天运算指令的微程序设计与调试

一、设计目标

设计并调试运算指令的微指令

二、运算指令微程序入口地址

指令助记符

指令编码

入口地址(H)

F

E

D

C

B

A

9

8

7

6

5

4

3

2

1

0

MOVsrc,dst

0

0

0

0

0

1

源地址码

目的地址码

044

ADDsrc,dst

0

0

0

0

1

0

源地址码

目的地址码

048

ADDCsrc,dst

0

0

0

0

1

1

源地址码

目的地址码

04c

SUBsrc,dst

0

0

0

1

0

0

源地址码

目的地址码

050

SUBBsrc,dst

0

0

0

1

0

1

源地址码

目的地址码

054

CMPsrc,dst

0

0

0

1

1

0

源地址码

目的地址码

058

ANDsrc,dst

0

0

0

1

1

1

源地址码

目的地址码

05c

ORsrc,dst

0

0

1

0

0

0

源地址码

目的地址码

060

XORsrc,dst

0

0

1

0

0

1

源地址码

目的地址码

064

TESTsrc,dst

0

0

1

0

1

0

源地址码

目的地址码

068

INCdst

0

0

0

0

0

0

1

0

0

0

1

目的地址码

0A4

DECdst

0

0

0

0

0

0

1

0

0

1

0

目的地址码

0A8

NOTdst

0

0

0

0

0

0

1

0

0

1

1

目的地址码

0AC

三、运算类指令微程序

(参照指导书图2-6的形式)

ADDC:

04C98B0006FTRoe,ADDC,SV,PSWce0:

NA->uAR06F

SUB:

05098F0006FTRoe,SUB,SV,PSWce0:

NA->uAR06F

SUBB:

0549930006FTRoe,SUBB,SV,PSWce0:

NA->uAR06F

CMP:

05898C0006FTRoe,SUB,PSWce0:

NA->uAR000

AND:

05C9970006FTRoe,AND,SV,PSWce0:

NA->uAR06F

OR:

06099B0006FTRoe,OR,SV,PSWce0:

NA->uAR06F

XOR:

0649A30006FTRoe,XOR,SV,PSWce0:

NA->uAR06F

DEC:

0A81AB0006FTRoe,DEC,SV,PSWce0:

NA->uAR06F

NOT:

0AC19F0006FTRoe,NOT,SV,PSWce0:

NA->uAR06F

四、测试程序、数据及运行结果

1、

测试内容:

1:

将数据移动到寄存器中;

2:

将存储数据单元的内容加1;

3:

将寄存器中的数据和地址单元里的数据进行比较;

4:

将寄存器做为变址寄存器,将其与1111进行逻辑与运算

运行数据:

07600000MOV#0000H,R1;

077A1101MOV#1101,0010;

023A0011INC(0011);

1B2A0015CMP(0015),(R1);

1F711111AND#1111,DISP(R1);

运行结果:

对于MOV指令而言,在第一天的课程设计的时候已经得到了验证,结果是正确的,这里就不在重复了。

加一指令INC,为了分析微程序是否正确,首先通过查看微指令流程判断BM和NC是设置是否正确,如果执行的微指令依次是:

001——002——003——006——00B——00F——022——0023——024——025——026——007——0A4——06F——071——072——000。

。

。

根据前面指令微流程的设计,所执行的微指令次序是正确的,而且,通过ALU运算后,输出结果加1,说明运算是正确的。

对于CMP指令的执行出现了问题,没将图片拷下来。

为了验证指令的正确性,我重新编写了MOV指令,并用了比较简单的寻址方式,以便快速查处问题所在。

之后就是所遇到的问题。

五、设计中遇到的问题及解决办法

对于CMP指令的执行出现了问题,没将出问题的图片拷下来。

但为了验证指令的正确性,我重新编写了MOV指令,并用了比较简单的寻址方式。

1B7AFFFD0008MOV#FFFD,0008H

并对RAM中的0008单元做了设置,将其中的内容改成了FFFD,根据CMP指令的工作原理,比较两个相同的数据的时候(两个数据都是FFFD),输出地PSW的标志位中的ZF应该为1,其他结果应该是0的。

但是运行的结果与想象中的有很大差别。

运行结果如下:

仔细看图片中的数据:

001——002——003——006——00B——00F——016——006——01B——01F——024——025——026——007——058——000指令的运行顺序没出现问题。

但是结果出现了问题。

SZOC为8,说明标志位SF为1,结果竟然是负的。

再看看ALU中的运行结果,竟然不是0000,而是FFFD,由此可知,并不是我的CMP指令出现了错误,而是ALU运算器出现了一点小小的错误(SUB指令的编写出了点问题)。

第三天CPU硬件的初级设计与验证

一、设计目标

在运算器实验的基础上对硬件进行扩充,建立初级CPU的数据通路,构造一个只支持运算指令的初级CPU。

二、硬件设计

1、PC模块设计

(加上适当注释)

/*程序计数器PC与R模块一样采用异步复位,当n_reset有效时,PC清0,否则在时钟信号clk的上升沿如果数据装入使能ce有效则d→q,如果自加信号PCinc有效则q+1→q。

PC通过三态门与IB相连。

*/

`timescale1ns/1ps

modulePC(d,q,n_reset,clk,ce,PCinc);

input[15:

0]d;

inputn_reset,clk,ce;

inputPCinc;

output[15:

0]q;

reg[15:

0]data;

always@(posedgeclkornegedgen_reset)

begin

if(!

n_reset)//当n_reset有效时,PC清0

data=0;

elseif(ce)//ce有效则d→q

data=d;

elseif(PCinc)//PCinc有效则q+1→q

data=data+1;

end

assignq=data;

endmodule

2、IR模块设计

`timescale1ns/1ps

/*DR连接内部总线IB和系统总线的DB;DR有两路数据输入data_IB、data_DB,分别来自IB、DB,相应的有两个装入使能信号DRce_IB、DRce_DB,输出端q分别通过两个三态门连到IB、DB。

DR采用异步复位,复位时DR清0,否则在时钟信号的上升沿,当DRce_IB有效时则data_IB→q,当DRce_DB有效时则data_DB→q。

*/

moduleDR#(

parameterDATAWIDTH=16)

(inputwire[DATAWIDTH-1:

0]data_IB,

inputwire[DATAWIDTH-1:

0]data_DB,

inputwireclk,

inputwireDRce_IB,

inputwireDRce_DB,

inputn_reset,

outputreg[DATAWIDTH-1:

0]q);

always@(posedgeclkornegedgen_reset)

begin

if(!

n_reset)//DR采用异步复位,复位时DR清0

q=0;

elseif(DRce_IB)//DRce_IB有效时则data_IB→q

q=data_IB;

elseif(DRce_DB)//DRce_DB有效时则data_DB→q

q=data_DB;

end

endmodule

3、顶层模块设计(自己增加的设计部分)

//TR寄存器的实例化

R#(DATAWIDTH)TR(.q(TR_out),.d(IB),.clk(clock),.ce(TRce),.n_reset(n_reset));

//AR寄存器的实例化

R#(DATAWIDTH)AR(.q(AR_out),.d(IB),.clk(clock),.ce(ARce),.n_reset(n_reset));

//IR寄存器的实例化

R#(DATAWIDTH)IR(.q(IR_out),.d(IB),.clk(clock),.ce(IRce),.n_reset(n_reset));

三、验证

07620014MOV#0000H,R1;

023A0014INC0014H;

1B2A0015CMP(0015),(R2);

07620001MOV#0001,R2;

1F721010AND#1010,DISP(R2);

运行结果:

结果分析:

为了分析微程序是否正确,首先通过查看微指令流程判断BM和NC是设置是否正确,如果执行的微指令依次是:

001——002——003——004——00B——00F——016——006——018——007——044——046——000根据前面指令微流程的设计,所执行的微指令次序是正确的,而且GRS里的数据内容为:

0014,所以执行的结果是正确的。

INC指令的执行的微指令依次是:

001——002——003——006——01B——01F——024——025——026——007——0A4——06F——071——072——000根据前面指令过程微流程的设计,所执行的微指令次序是正确的。

INC指令执行后,ALU中内容是FFFD(原来0014单元内容为FFFC),所以执行结果是正确的。

CMP指令:

为了分析微程序是否正确,首先通过查看微指令流程判断BM和NC是设置是否正确。

执行的微指令依次是:

001——002——003——004——00B——00F——012——013——014——015——016——006——019——025——026——007——058——000根据执行结果看:

ALU中运行结果是0000,而且PSW标志位为0101。

说明结果为0,且没有借位。

执行结果正确。

MOV+AND指令

MOV指令的执行是没问题的。

为了分析AND微程序是否正确,首先通过查看微指令流程判断BM和NC是设置是否正确。

执行的微指令依次是:

001——002——003——004——00B——00F——016——006——01A——01C——01D——01E——027——025——026——007——05C——06F——071——072——000根据执行结果看:

ALU中运行结果是0000,而且PSW标志位为0101。

说明结果为0,且没有借位。

执行结果正确。

四、设计中遇到的问题及解决办法

问题:

INC指令

在结果执行过程中

仔细看程序执行的过程可知:

INC指令应该在取完目的操作数之后(026)就转到EXE执行007,但是程序中却是直接返回取指令入口。

这个问题应该出在微指令设计的正确性上,果然,查看micro中的微指令(026)单元,竟然是00000000,问题出现在这里。

但是这个确实很奇怪,在第二天的时候我已经将所有微指令都保存好了,但现在下载的微指令却和第二天的微指令不一样,很可能是软件设计上的缺陷吧。

将正确的微指令输入后,问题也就解决了。

同样的问题出现在AND指令上。

一下就是AND指令运行的结果。

从程序运行的流程上看:

正确的AND指令应该在执行完01A后执行的01C的。

但是这里却出现了错误。

经检查,同样的问题出现了,micro了的微指令已经和第二天设计的微指令不一样了,由此可见该软件还存在一些缺陷。

第四天为CPU扩充转移指令

一、设计要求

在初级CPU的基础上进行功能扩充,使其支持转移类指令

二、硬件uAG模块设计

(自己修改的设计部分,加上适当注释)

3’d3:

uAGout={NA[8:

1],BM3_uAR0};

case(IR[7:

6])//条件转移类指令*

2'b00:

Flag_MUX<=1'b0;

2'b01:

Flag_MUX<=1'b0;//添加第四天的代码,参照指导书图2-10

2'b10:

Flag_MUX<=1'b0;//根据标志位正确生成BM3_uAR0

2'b11:

Flag_MUX<=1'b0;

default:

Flag_MUX<=1'b0;

endcase

三、转移指令微程序的设计

四、测试程序、数据及运行结果

1、

测试内容

(1):

通过比较指令,将PSW标志位设置为5,然后测试转移指令是否能正确执行。

运行数据:

(0010单元设置为1111,如下图)

1B7A11110010CMP#1111,0010;

019A000BJZ000B;

运行结果及分析:

为了分析CMP+JZ微程序是否正确,首先通过查看微指令流程判断BM和NC是设置是否正确。

首先,CMP执行的微指令依次是:

001——002——003——004——00B——00F——016——006——01B——01F——024——025——026——007——058——000根据执行结果看:

ALU中运行结果是0000,而且PSW标志位为0101。

说明结果为0,且没有借位。

执行结果正确。

接下来验证JZ指令执行是否正确:

001——002——003——006——01B——01F——024——025——026——007——075——077——000,程序正常跳转,执行结果正确。

测试内容

(2):

通过比较指令,将PSW标志位设置为9,然后测试转移指令是否能正确执行。

运行数据:

(0010单元设置为FFEF,如下图)

1B7A11110010CMP#1111,0010;

019A000BJZ000B;

运行结果及分析:

为了分析CMP+JZ微程序是否正确,首先通过查看微指令流程判断BM和NC是设置是否正确。

首先,CMP执行的微指令依次是:

001——002——003——004——00B——00F——016——006——01B——01F——024——025——026——007——058——000根据执行结果看:

ALU中运行结果是EEDE,而且PSW标志位为9。

说明结果为负,且有借位。

执行结果正确。

接下来验证JZ指令执行是否正确:

001——002——003——006——01B——01F——024——025——026——007——075——076——000,程序正常跳转,执行结果正确。

五、设计中遇到的问题及解决办法

出现的问题:

在程序编写完成后,开始验证。

但是指令运行顺序出现了问题。

如图所示:

(程序没有跳转到075的位置)

微指令运行的顺序出现了问题,首先考虑微指令编码有没有出现错误。

经仔细检测,指令编码没有出现问题。

接下来很可能是程序出现了问题。

果然,在转移指令的入口的地方,原本要设置为075H,但是我在编写代码的时候写成了4’b0011IR[7:

5]1’b01;这样子虽然能运行程序,但是却将程序复杂化,本来只需要一个模式来执行转移程序的,现在却必须为8个转移指令准备8个转移条件。

为了使程序运行,将代码改成’h075后,程序只需要一个入口来为8个转移指令服务。

第五天为CPU扩充移位指令

一、设计目标

在前面CPU的就出上扩充硬件,使其支持移位指令。

二、硬件设计

1、SHIFTER模块设计

(加上适当注释)

muxmux_lsb(.addr(IR76),.q(data_lsb),.d1(1'b0),.d2(1'b0),.d3(d[DATAWIDTH-1]),.d4(CF));

muxmux_hsb(.addr(IR76),.q(data_hsb),.d1(d[DATAWIDTH-1]),.d2(1'b0),.d3(d[0]),.d4(CF));

2、CF模块设计

`timescale1ns/1ps

moduleCF_MUX(d15,d0,Cout,q,SL,SR);

inputd15,d0,Cout;

inputSL,SR;

outputq;

regq;

always@(*)

begin

case({SL,SR})

3'b01:

q=d0;

3'b10:

q=d15;

default:

q=Cout;

endcase

end

endmodule

3、IR_DECODE模块设计(自己增加修改的设计部分)

2'b00:

BM4_uA<={5'b01001,IR[7:

5],1'b0};

4、顶层模块设计(增加自己修改的设计部分)

wireCF;

CF_MUXCFM(.d15(ALU_out[DATAWIDTH-1]),.d0(ALU_out[0]),.Cout(Cout),.q(CF),.SL(SL),.SR(SR));

三、移位指令微程序的设计

微地址(H)

微指令(H)

微指令字段(H)

微命令

F0

F1

F2

F3

F4

F5

F6

F7

F8

F9

092

SAR

0

6

0

1

0

0

0

0

0

06F

1810006F

094

SHL

0

6