8位十进制频率计设计 EDA技术与Verilog HDL实验报告.docx

《8位十进制频率计设计 EDA技术与Verilog HDL实验报告.docx》由会员分享,可在线阅读,更多相关《8位十进制频率计设计 EDA技术与Verilog HDL实验报告.docx(8页珍藏版)》请在冰豆网上搜索。

8位十进制频率计设计EDA技术与VerilogHDL实验报告

8位十进制频率计设计

一.实验目的

熟悉在QuartusII下设计2位和8位十进制频率计。

二.实验内容

在QuartusII下设计2位和8位十进制频率计,并编译、仿真验证其功能。

三.程序清单

频率计顶层文件设计:

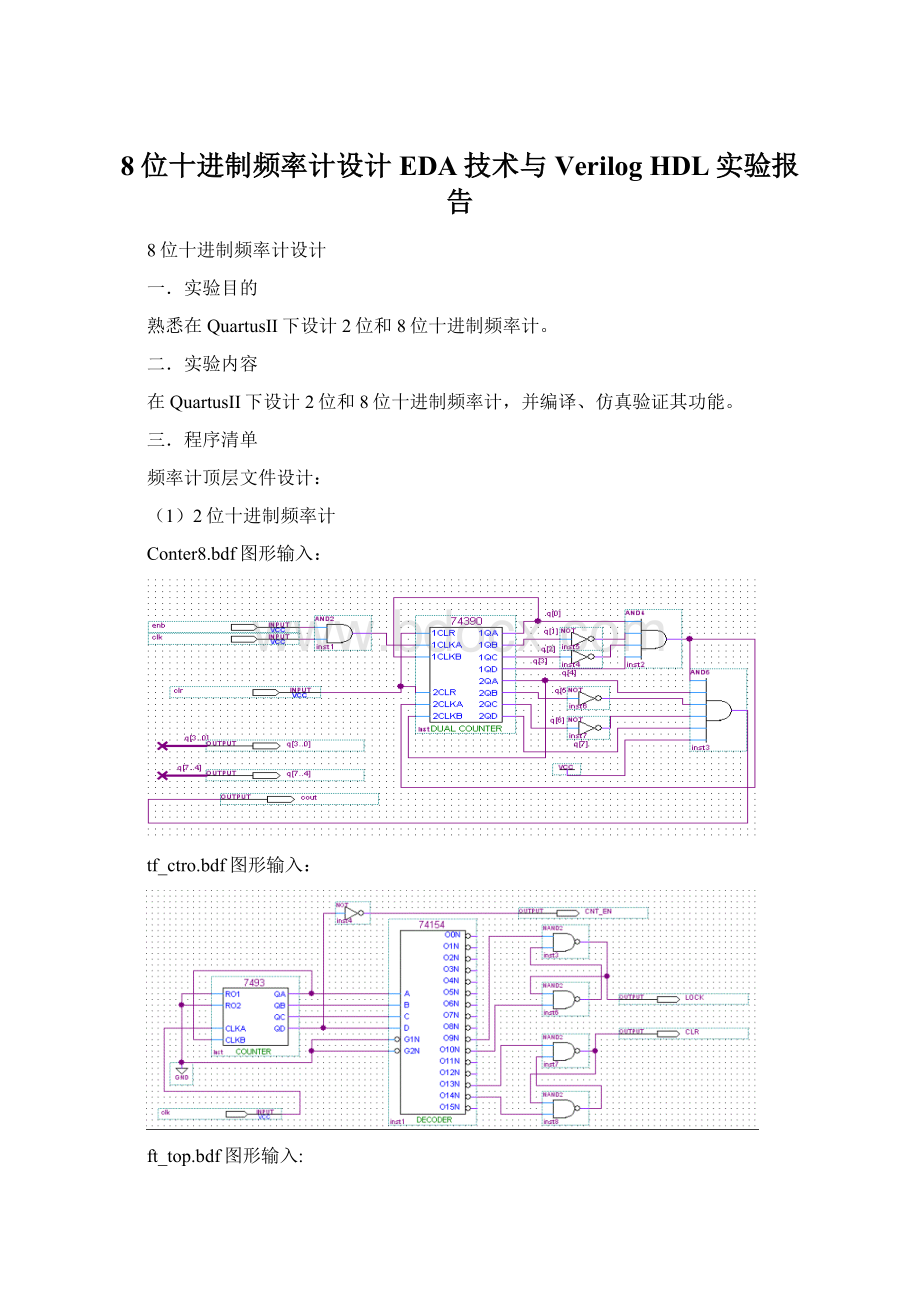

(1)2位十进制频率计

Conter8.bdf图形输入:

tf_ctro.bdf图形输入:

ft_top.bdf图形输入:

conter100.v文本输入:

moduleconter100(CLK,CLR,EN,cout,ge,shi);

inputCLK,EN,CLR;

output[3:

0]ge;

output[3:

0]shi;

outputcout;

regcout;

reg[3:

0]ge;

reg[3:

0]shi;

always@(posedgeCLK)

if(!

CLR)

begin

ge<=0;

shi<=0;

cout<=0;

end

elseif((ge==9)&&(shi==9))

begin

ge<=0;

shi<=0;

cout<=1;

end

elseif(ge==9)

begin

ge<=0;

shi<=shi+1;

cout<=0;

end

else

begin

ge<=ge+1;

shi<=shi;

cout<=0;

end

endmodule

tf_ctro.v文本输入:

moduletf_ctro(clk,en,clr,lock);

inputclk;

outputen,clr,lock;

regen,clr,lock;

integerd=0;

always@(posedgeclk)

begin

d<=d+1;

if(d==1)

begin

en<=0;

lock<=0;

clr<=0;end

elseif(d==2)

begin

lock<=1;

en<=0;

clr<=0;

end

elseif(d==3)

begin

lock<=0;

clr<=0;

en<=0;

end

elseif(d==6)

begin

lock<=0;

clr<=1;

en<=0;

end

elseif(d==7)

begin

lock<=0;

clr<=0;

en<=0;

end

elseif(d==8)

begin

lock<=0;

clr<=0;

en<=1;

end

elseif(d==16)

begin

d<=0;

en<=0;

lock<=0;

clr<=0;

end

end

endmodule

74374锁存器文本输入:

moduleoctal(clk,en,d_in,q_in);

inputclk,en;

input[3:

0]d_in;

output[3:

0]q_in;

reg[3:

0]Q;

assignq_in=Q;

always@(posedgeclk)

if(!

en)

begin

Q<=d_in;

end

endmodule

(2)8位十进制频率计

ft_top.bdf图形输入:

四.实验步骤

1、新建一个名称为CTR10的工程,并在该文件夹中新建一个CTR10.bdf的文件,在工程文件夹中新建一个counter8.bdf的文件。

2、编译工程,编译成功后进行下一步,若不成功则查改错误。

3、在工程文件夹中新建一个CTR10.vwf的波形文件,导入工程端口,设置输入波形,仿真得出输出端口波形。

4、验证输出端口波形是否实现8位十进制频率计的功能。

五、实验数据

仿真波形如下图所示:

(1)2位十进制频率计

Conter8.bdf图形输入仿真波形:

Conter100.v文本输入仿真波形:

Tf_ctro.bdf图形输入仿真波形输入:

ft_top.bdf图形输入仿真波形:

(2)8位十进制频率计

ft_top.bdf图形输入仿真波形

六、实验小结

通过本次实验熟悉在QuartusII下设计2位和8位十进制频率计,并编译、仿真验证其功能。