EDA技术实验指导书new.docx

《EDA技术实验指导书new.docx》由会员分享,可在线阅读,更多相关《EDA技术实验指导书new.docx(17页珍藏版)》请在冰豆网上搜索。

EDA技术实验指导书new

EDA技术实验指导书

电路教研组

2007.8

实验一利用原理图输入法设计4位全加器

一、实验目的:

掌握利用原理图输入法设计简单组合电路的方法,掌握MAX+plusII的层次化设计方法。

通过一个4位全加器的设计,熟悉用EDA软件进行电路设计的详细流程。

二、实验原理:

一个4位全加器可以由4个一位全加器构成,全加器的进位以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的低位进位输入信号cin相接。

1位全加器f-adder由2个半加器h-adder和一个或门按照下列电路来实现。

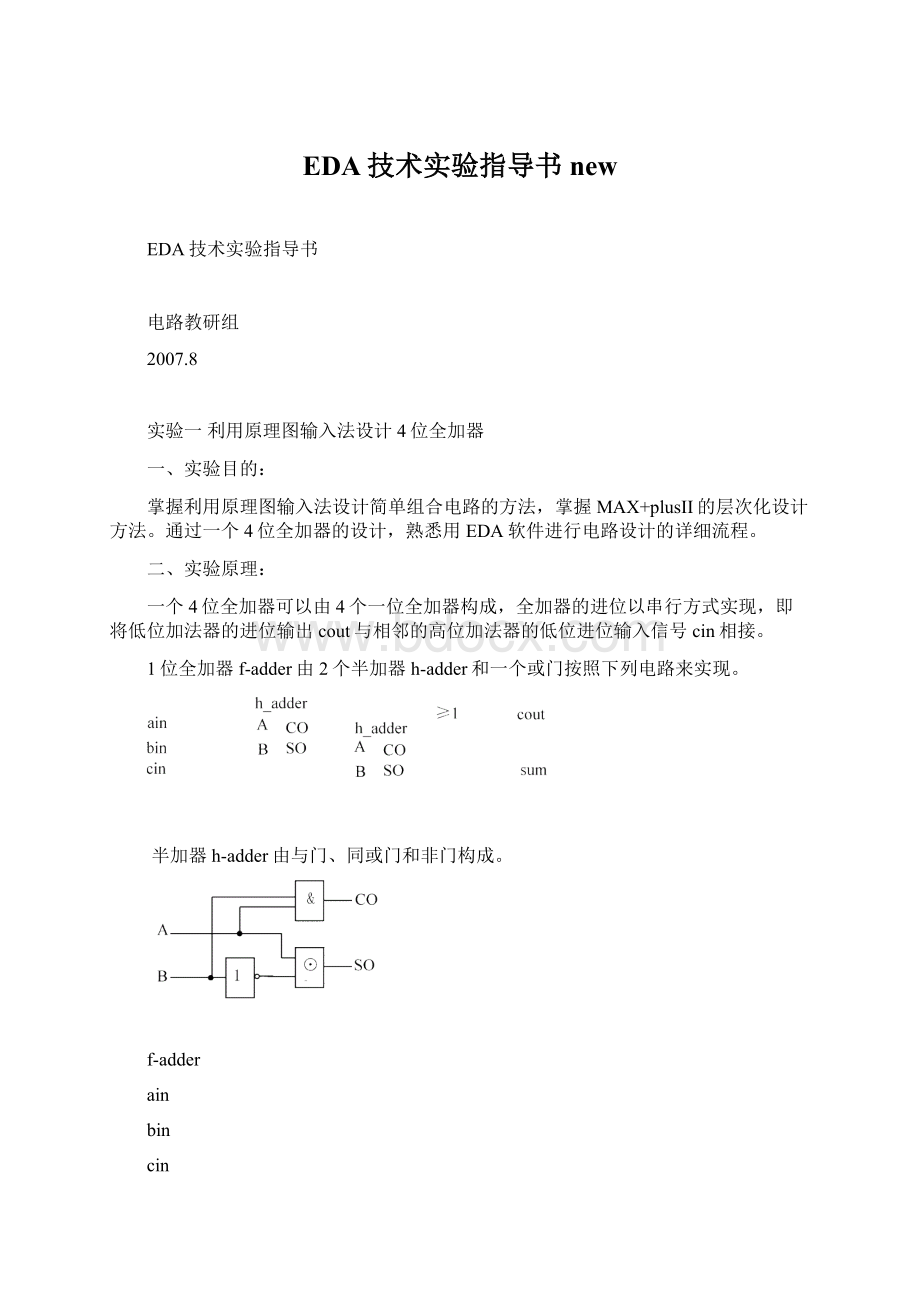

半加器h-adder由与门、同或门和非门构成。

f-adder

ain

bin

cin

cout

sum

ain

bin

cin

cout

sum

ain

bin

cin

cout

sum

f-adder

f-adder

f-adder

A1B1

A2B2

A3B3

A4B4

ain

bin

cin

cout

sum

CI

CO

S1

S2

S3

S4

四位加法器由4个全加器构成

三、实验内容:

1.熟悉QuartusII软件界面,掌握利用原理图进行电路模块设计的方法。

信息显示窗

编译状态显示区

工程工作区

资源管理区

QuartusII设计流程见教材第五章:

QuartusII应用向导。

2.设计1位全加器原理图

(1)生成一个新的图形文件(file->new->graphiceditor)

(2)按照给定的原理图输入逻辑门(symbol->entersymbol)

(3)根据原理图连接所有逻辑门的端口,并添加输入/输出端口

(4)为管脚和节点命名:

在管脚上的PIN_NAME处双击鼠标左键,然后输入名字;

选中需命名的线,然后输入名字。

(5)创建缺省(Default)符号:

在File菜单中选择CreateSymbolFilesforCurrentFile项,即可创建一个设计的符号,该符号可被高层设计调用。

3.利用层次化原理图方法设计4位全加器

(1)生成新的空白原理图,作为4位全加器设计输入

(2)利用已经生成的1位全加器的缺省符号作为电路单元,设计4位全加器的原理图.

4.新建波形文件(file->new->OtherFiles->VectorWaveformFile),保存后进行仿真(Processing->StartSimulation),对4位全加器进行时序仿真。

给出波形图,并分析仿真结果是否正确。

5.思考如何在原理图中输入一个总线,并与其他总线连接?

实验二简单组合电路的设计

一、实验目的:

熟悉QuartusIIVHDL文本设计流程全过程。

学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

二、实验原理

VHDL硬件描述语言是一种可以从多个层次上对数字逻辑电路进行建模的国际标准(IEEE),本次实验是用VHDL设计一个简单的数字组合逻辑电路,并结合QuartusII环境和实验电路进行硬件测试。

三、实验内容:

1)根据实验一中一位全加器的电路原理图,改用VHDL语言文本输入方法,设计一位全加器,要求采用结构化的描述方法。

设计完成后,利用QuartusII集成环境进行时序分析、仿真,记录仿真波形和时序分析数据。

2)用VHDL语言设计一个四选一数据选择器电路。

要求先设计一个二选一数据选择器mux21,然后利用元件例化语句设计四选一数据选择器mux41,同样请给出时序分析数据和仿真结果。

3)硬件测试(选用器件EPF10K10Pin84)

管脚锁定:

1)一位全加器aPIO23(I/O19)30SW1

bPIO24(I/O20)35SW2

ciPIO25(I/O21)36SW3

sPIO21(I/O16)27LED10

coPIO19(I/O8)29LED12

2)四选一数据选择器a1PIO2330SW1

a0PIO2435SW2

d3PIO2738SW5

d2PIO2839SW6

d1PIO2947SW7

d0PIO3042SW8

yout29LED12

四、思考题

比较原理图输入法和文本输入法的优缺点。

实验结果:

一位全加器的VHDL描述:

仿真波形:

硬件测试结果及分析:

四选一数据选择器的VHDL描述:

仿真波形:

硬件测试结果及分析:

回答问题:

实验三简单时序电路的设计

一、实验目的:

熟悉QuartusII的VHDL文本设计过程,学习简单时序电路的设计、仿真和硬件测试。

二、实验原理

时序逻辑电路是现代复杂数字电路的重要组成部分,往往占到整个设计的90%以上。

触发器是时序电路的基本单元,本实验中将涉及到边沿触发和电平触发两种电路结构,其中边沿触发是实际电路实现的主要方式。

三、实验内容

1)设计一个上升沿触发的D触发器

输入:

D

输出:

Q

触发时钟:

CLK

2)设计同步/异步清零D触发器

触发器有两种清零方式:

同步——当触发沿到来时,若清零信号有效,则实现清零;异步——任何时候清零信号一旦有效,触发器马上清零,而不论触发沿是否到来。

在以上设计的D触发器基础上,加入清零端rst,分别实现同步和异步清零方式。

3)设计一个高电平有效的锁存器

输入:

D

输出:

Q

触发:

E

电平触发的锁存器与沿触发的触发器不同之处在于当触发端处于有效电平时,输出等于输出,随输入变化;触发端无效时输出保持不变。

4)在QuartusII环境下对以上设计的模块进行编译,记录时序分析数据和仿真波形,并在实验电路上进行硬件测试。

管脚锁定:

DPIO2330SW1

CLKCLK143频率源(35SW2)

QPIO1929LED12

四、问题

1)在本次实验中你使用的VHDL描述方式是和实验二中一样的结构化描述还是行为级描述?

这两种方式描述的编译出来的仿真结果是否相同?

2)请在试验报告中分析和比较1)和3)的仿真和实测结果,说明两者之间的异同点。

实验结果:

上升沿触发的D触发器的VHDL描述:

仿真波形:

硬件测试结果及分析:

设计同步/异步清零D触发器的VHDL描述:

仿真波形:

硬件测试结果及分析:

高电平有效的锁存器的VHDL描述:

仿真波形:

硬件测试结果及分析:

回答问题:

实验四设计一个异步清零和同步时钟使能的4位加法计数器

一、实验目的:

学习计数器的设计、仿真和硬件测试,进一步熟悉VHDL设计技术。

二、实验原理

本试验中所要设计的计数器,由4位带异步清零的加法计数器和一个4位锁存器组成。

其中,rst是异步清零信号,高电平有效;clk是计数时钟,同时也是锁存信号;ENA为计数器输出使能控制。

当ENA为‘1’时,加法计数器的输出值加载于锁存器的数据端,;当ENA为‘0’时锁存器输出为高阻态。

当计数器输出“1111”时,进位信号COUT为“1”。

三、实验内容

1)画出该计数器的原理框图。

2)用VHDL语言完成上述计数器的行为级设计。

可以采用分层描述的方式,分别设计计数器和输出锁存器模块,然后将两个模块组合成一个顶层模块。

注意锁存器输出高阻时的描述的方式。

3)用QuartusII对上述设计进行编译、综合、仿真,给出其所有信号的仿真波形和时序分析数据。

4)通过QuartusII集成环境,将设计下载到实验电路上进行硬件测试。

引脚锁定:

clk:

clk143clk1

rst:

PIO2435SW2

ena:

PIO2330SW1

outy(3)PIO1929LED12

outy

(2)PIO2028LED11

outy

(1)PIO2127LED10

outy(0)PIO2225LED9

coutPIO1223LED7

2、思考题:

如果需要设计带并行预置初始值的计数器,用VHDL应如何描述?

实验结果:

计数器的原理框图:

计数器的VHDL描述:

仿真波形:

硬件测试结果及分析:

回答问题:

实验五七段数码显示译码器设计

一、实验目的:

学习7段数码显示译码器设计,学习VHDL的多层次设计方法。

二、实验原理:

七段数码管由8个(a,b,c,d,e,f,g,dp)按照一定位置排列的发光二极管构成,通常采取共阴极或者共阳极的设计,将8个二极管的同一极接在一起,通过分别控制另外的8个电极的电平,使二极管导通(发光)或截止(不发光)。

七段数码显示译码器的功能就是根据需要显示的字符,输出能够控制七段数码管显示出该字符的编码。

三、实验内容:

1)用VHDL设计7段数码管显示译码电路,并在VHDL描述的测试平台下对译码器进行功能仿真,给出仿真的波形。

2)数码管显示电路设计

利用以上设计的译码器模块,设计一个可以在8个数码管上同时显示字符的电路。

快速轮流点亮8个数码管,这样就可以实现同时显示8个字符的效果(尽管实际上同一时间只有一个数码管被点亮)。

要实现以上功能,就必须按照一定时钟节拍,轮流使译码器输出所需要字符的编码;同时控制数码管的公共电极电平,轮流点亮数码管(可以使用上个实验设计的计数器,加实验板上的74ls138来实现)。

3)用QuartusII对2)中的设计进行编译、综合、仿真,给出其所有信号的仿真波形和时序分析数据。

4)通过QuartusII集成环境,将设计下载到实验电路上进行硬件测试。

管脚锁定:

*clk:

clk143clk1

D(3):

PIO3030SW1

D

(2):

PIO2435SW2

D

(1):

PIO2536SW3

D(0):

PIO2637SW4

A(6):

PIO611SEGgLED1

A(5):

PIO510SEGf

A(4):

PIO49SEGe

A(3):

PIO38SEGd

A

(2):

PIO27SEGc

A

(1):

PIO16SEGb

A(0):

PIO05SEGa

*S

(2):

80

*S

(1):

79

*S(0):

78

四、思考题:

尝试将74ls138的功能也用VHDL来实现,将所有逻辑功能都集成到FPGA里面。

实验结果:

数码管显示电路的原理框图:

VHDL描述:

仿真波形:

硬件测试结果及分析:

回答问题:

实验六数控分频器的设计

一、实验目的:

学习数控分频器的设计和测试方法。

二、实验原理:

数控分频器的功能为在不同输入信号时,对时钟信号进行不同的分频,在输出端输出不同频率的信号。

该电路可以用具有并行预置功能的加法计数器实现,方法是对应不同的输入信号,预置数(初始计数值)设定不同的值,计数器以此预置数为初始状态进行不同模值的计数,当计数器的状态全为1时,计数器输出溢出信号。

用计数器的溢出信号作为输出信号或输出信号的控制值,使输出信号的频率受控于输入的预置数。

电路输出波形图:

三、实验内容:

1)根据实验原理画出电路框图,并计算在不同预置数时输出信号的频率与时钟频率的比值。

2)编写实现数控分频器的VHDL程序。

要求输出信号的占空比尽量为50%。

提示:

可以将计数器溢出信号输出给一个翻转触发器,溢出信号的边沿作为触发器的触发信号,触发器的输出就是分频器的输出(注意计数器初始计数值与输出频率之间的关系)。

3)用QuartusII对设计进行编译、综合、仿真,给出仿真波形和时序分析数据。

4)通过QuartusII集成环境,将设计下载到实验电路上进行硬件测试。

输入不同的clk信号和不同的输入控制信号,测试输出波形。

管脚锁定:

clkclk143

D(3)PIO2330SW1

D

(2)PIO2435SW2

D

(1)Pio2536SW3

D(0)PIO2637SW4

FoutPIO1929LED12

四、思考题:

如果需要进行奇数分频(如3分频),能否够保持输出波形的占空比为50%?

如果不能,如何使占空比尽量接近50%;如果可以,应如何做?

实验结果:

数控分频器的原理框图:

数控分频器输出频率与输入时钟的关系:

数控分频器的VHDL描述:

仿真波形:

硬件测试结果及分析:

回答问题:

实验七4位十进制频率计的设计

一、实验目的:

设计一个4位十进制频率计,学习复杂数字系统的设计方法。

二、实验原理:

根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1秒的脉冲计数允许信号,1秒计数结束后,计数值(即所测信号频率)锁入锁存器,并为下一次测频作准备,即将计数器清零。

三、试验内容:

1、根据频率计的工作原理,将电路划分成控制器、计数器、锁存器和LED显示几个模块,

控制器——产生1秒脉宽的计数允许信号、锁存信号和计数器清零信号

计数器——对输入信号的脉冲数进行累计

锁存器——锁存测得的频率值

LED显示——将频率值显示在数码管上

顶层文件框图如下:

2、用元件例化语句写出频率计的顶层文件。

3、用VHDL硬件描述语言进行模块电路的设计。

本实验中不少模块在之前的实验中已经有所涉及,只需要对以前的设计做部分修改即可用于这次实验。

提示:

十进制计数器输出的应是4位十进制数的BCD码,因此输出一共是4×4bit。

4、用QuartusII对设计进行编译、综合、仿真,给出仿真波形和时序分析数据(不包括数码管显示部分)。

5、通过QuartusII集成环境,将设计下载到实验电路上进行硬件测试。

管脚锁定:

Clkclk143

fx(频率任选)

A(7):

81SEGdp

A(6):

PIO611SEGg

A(5):

PIO510SEGf

A(4):

PIO49SEGe

A(3):

PIO38SEGd

A

(2):

PIO27SEGc

A

(1):

PIO16SEGb

A(0):

PIO05SEGa

S

(1):

79

S(0):

78

四、思考题:

本实验中的控制器部分可以用以前实验中的哪个电路来实现,其输出的rst和ena信号是否可以合并为一个信号?

实验结果:

各模块电路的VHDL描述:

顶层电路的VHDL描述:

仿真波形:

硬件测试结果及分析:

回答问题:

实验八交通灯控制电路的设计

一、实验目的:

进一步学习复杂数字电路的设计方法,提高利用硬件描述语言进行电路设计的技巧和熟练程度。

二、实验要求及原理:

1、满足图1顺序工作流程。

图中设南北方向的红、黄、绿灯分别为NSR、NSY、NSG,东西方向的红、黄、绿灯分别为EWR、EWY、EWG。

它们的工作方式有些必须是并行进行的,即南北方向绿灯亮,东西方向红灯亮;南北方向黄灯亮,东西方向红灯亮;南北方向红灯亮,东西方向绿灯亮;南北方向红灯亮,东西方向黄红灯亮。

图1交通灯顺序工作流程图

2、应满足两个方向的工作时序:

即东西方向亮红灯时间应等于南北方向亮黄、绿灯时间之和,南北方向亮红灯时间应等于东西方向亮黄、绿灯时间之和。

时序流程图2所示。

图2中,假设每个单位时间为3秒,则南北、东西方向绿、黄、红灯亮时间分别15秒、3秒、18秒,一次循环为36秒。

其中红灯亮的时间为绿灯、黄灯亮的时间之和。

图2交通灯时序工作流程图

3、十字路口要有数字显示,作为时间提示,以便人们更直观地把握时间。

具体为:

当某方向红灯亮时,置显示器为某值,然后以每秒减1计数方式方式工作,直至减到数为“0”,十字路口红、绿灯交换,一次工作循环结束,进入下一步某方向地工作循环。

例如:

当南北方向从黄灯转换成红灯时,置南北方向数字显示为24,并使数显计数器开始减“1”计数,当减到“0”,时,此时红灯灭,而南北方向的绿灯亮;同时,东西方向的红灯亮,并置东西方向的数显为24。

三、实验内容

1、根据实验要求及原理1、2画出交通指示灯控制电路原理框图。

提示:

两个方向的控制电路可以共用一个24进制计数器实现。

2、用VHDL硬件描述语言层次化设计方法进行顶层文件和各模块电路的设计。

3、用QuartusII对设计进行编译、综合、仿真,给出仿真波形和时序分析数据(不包括数码显示部分)。

4、通过QuartusII集成环境,将设计下载到实验电路上进行硬件测试。

管脚锁定:

clk:

clk143clk1

start:

PIO2330SW1

NSGPIO1929LED12

NSYPIO2028LED11

NSRPIO2127LED10

EWGPIO22LED3

EWYPIO12LED2

EWRLED1

5、画出完整的交通灯控制电路原理框图(含数码显示部分)。

6、修改上述内容2的设计,增加数码显示部分。

注意:

两方向的计数要求分别显示在数码管1、2和数码管7、8上。

7、用MAX_plusⅡ对设计进行编译、综合、仿真,给出仿真波形和时序分析数据。

8、再次将设计下载到实验电路上进行硬件测试。

新增管脚锁定:

A(6):

PIO611SEGg

A(5):

PIO510SEGf

A(4):

PIO49SEGe

A(3):

PIO38SEGd

A

(2):

PIO27SEGc

A

(1):

PIO16SEGb

A(0):

PIO05SEGa

*S

(2):

80

*S

(1):

79

*S(0):

78

四、思考题:

1、控制电路除用有限状态机实现外,还可以采用什么方法实现?

2、如果增加夜间显示(即全部黄灯闪烁),电路该怎样设计?

实验结果:

交通灯控制电路原理框图:

顶层电路的VHDL描述:

各模块电路的VHDL描述:

交通灯工作时序仿真波形:

硬件测试结果及分析:

回答问题:

仅供个人用于学习、研究;不得用于商业用途。

Forpersonaluseonlyinstudyandresearch;notforcommercialuse.

NurfürdenpersönlichenfürStudien,Forschung,zukommerziellenZweckenverwendetwerden.

Pourl'étudeetlarechercheuniquementàdesfinspersonnelles;pasàdesfinscommerciales.

толькодлялюдей,которыеиспользуютсядляобучения,исследованийинедолжныиспользоватьсявкоммерческихцелях.

以下无正文