2440寄存器总结.docx

《2440寄存器总结.docx》由会员分享,可在线阅读,更多相关《2440寄存器总结.docx(18页珍藏版)》请在冰豆网上搜索。

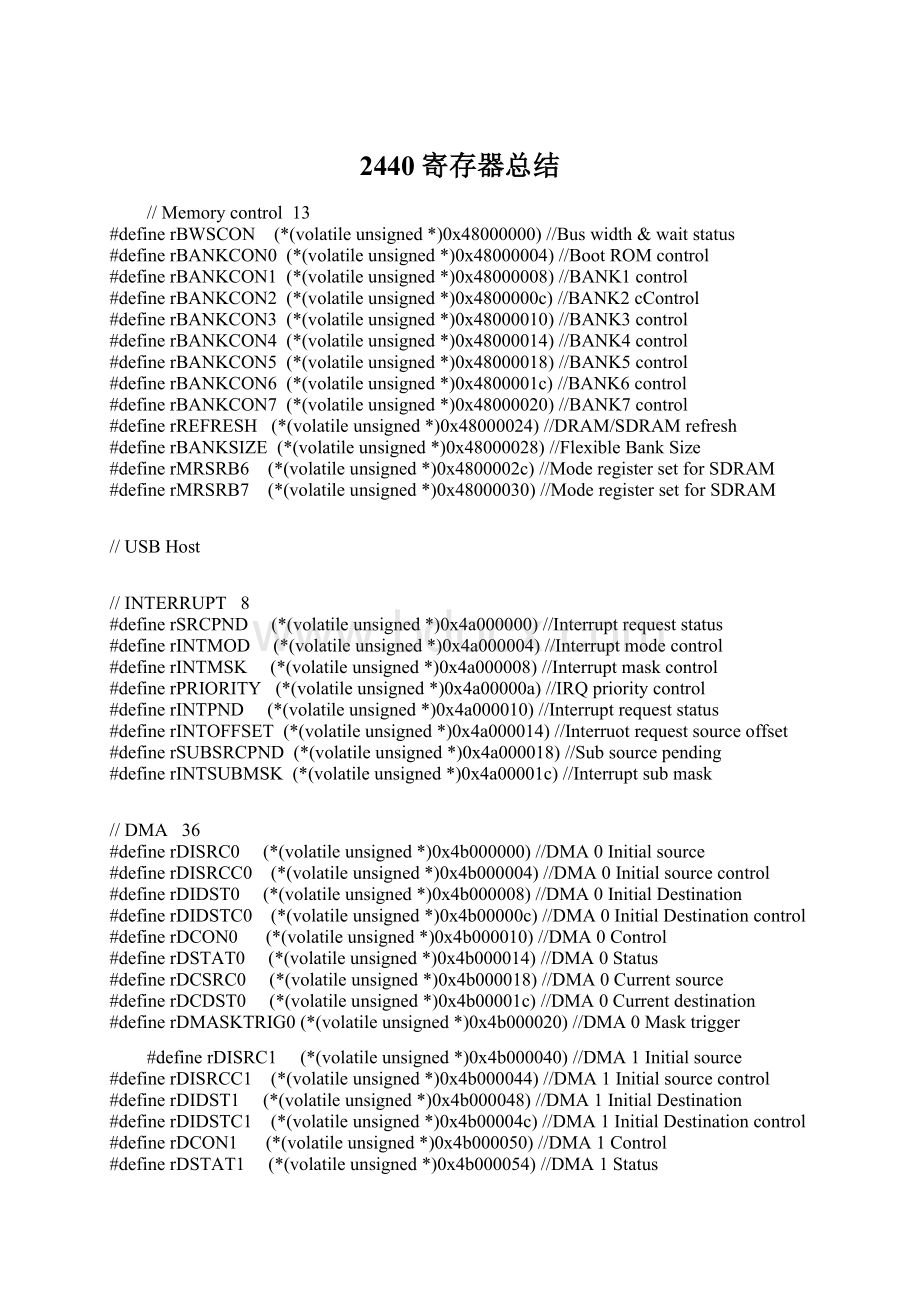

2440寄存器总结

//Memorycontrol 13

#definerBWSCON (*(volatileunsigned*)0x48000000)//Buswidth&waitstatus

#definerBANKCON0 (*(volatileunsigned*)0x48000004)//BootROMcontrol

#definerBANKCON1 (*(volatileunsigned*)0x48000008)//BANK1control

#definerBANKCON2 (*(volatileunsigned*)0x4800000c)//BANK2cControl

#definerBANKCON3 (*(volatileunsigned*)0x48000010)//BANK3control

#definerBANKCON4 (*(volatileunsigned*)0x48000014)//BANK4control

#definerBANKCON5 (*(volatileunsigned*)0x48000018)//BANK5control

#definerBANKCON6 (*(volatileunsigned*)0x4800001c)//BANK6control

#definerBANKCON7 (*(volatileunsigned*)0x48000020)//BANK7control

#definerREFRESH (*(volatileunsigned*)0x48000024)//DRAM/SDRAMrefresh

#definerBANKSIZE (*(volatileunsigned*)0x48000028)//FlexibleBankSize

#definerMRSRB6 (*(volatileunsigned*)0x4800002c)//ModeregistersetforSDRAM

#definerMRSRB7 (*(volatileunsigned*)0x48000030)//ModeregistersetforSDRAM

//USBHost

//INTERRUPT 8

#definerSRCPND (*(volatileunsigned*)0x4a000000)//Interruptrequeststatus

#definerINTMOD (*(volatileunsigned*)0x4a000004)//Interruptmodecontrol

#definerINTMSK (*(volatileunsigned*)0x4a000008)//Interruptmaskcontrol

#definerPRIORITY (*(volatileunsigned*)0x4a00000a)//IRQprioritycontrol

#definerINTPND (*(volatileunsigned*)0x4a000010)//Interruptrequeststatus

#definerINTOFFSET (*(volatileunsigned*)0x4a000014)//Interruotrequestsourceoffset

#definerSUBSRCPND (*(volatileunsigned*)0x4a000018)//Subsourcepending

#definerINTSUBMSK (*(volatileunsigned*)0x4a00001c)//Interruptsubmask

//DMA 36

#definerDISRC0 (*(volatileunsigned*)0x4b000000)//DMA0Initialsource

#definerDISRCC0 (*(volatileunsigned*)0x4b000004)//DMA0Initialsourcecontrol

#definerDIDST0 (*(volatileunsigned*)0x4b000008)//DMA0InitialDestination

#definerDIDSTC0 (*(volatileunsigned*)0x4b00000c)//DMA0InitialDestinationcontrol

#definerDCON0 (*(volatileunsigned*)0x4b000010)//DMA0Control

#definerDSTAT0 (*(volatileunsigned*)0x4b000014)//DMA0Status

#definerDCSRC0 (*(volatileunsigned*)0x4b000018)//DMA0Currentsource

#definerDCDST0 (*(volatileunsigned*)0x4b00001c)//DMA0Currentdestination

#definerDMASKTRIG0(*(volatileunsigned*)0x4b000020)//DMA0Masktrigger

#definerDISRC1 (*(volatileunsigned*)0x4b000040)//DMA1Initialsource

#definerDISRCC1 (*(volatileunsigned*)0x4b000044)//DMA1Initialsourcecontrol

#definerDIDST1 (*(volatileunsigned*)0x4b000048)//DMA1InitialDestination

#definerDIDSTC1 (*(volatileunsigned*)0x4b00004c)//DMA1InitialDestinationcontrol

#definerDCON1 (*(volatileunsigned*)0x4b000050)//DMA1Control

#definerDSTAT1 (*(volatileunsigned*)0x4b000054)//DMA1Status

#definerDCSRC1 (*(volatileunsigned*)0x4b000058)//DMA1Currentsource

#definerDCDST1 (*(volatileunsigned*)0x4b00005c)//DMA1Currentdestination

#definerDMASKTRIG1(*(volatileunsigned*)0x4b000060)//DMA1Masktrigger

#definerDISRC2 (*(volatileunsigned*)0x4b000080)//DMA2Initialsource

#definerDISRCC2 (*(volatileunsigned*)0x4b000084)//DMA2Initialsourcecontrol

#definerDIDST2 (*(volatileunsigned*)0x4b000088)//DMA2InitialDestination

#definerDIDSTC2 (*(volatileunsigned*)0x4b00008c)//DMA2InitialDestinationcontrol

#definerDCON2 (*(volatileunsigned*)0x4b000090)//DMA2Control

#definerDSTAT2 (*(volatileunsigned*)0x4b000094)//DMA2Status

#definerDCSRC2 (*(volatileunsigned*)0x4b000098)//DMA2Currentsource

#definerDCDST2 (*(volatileunsigned*)0x4b00009c)//DMA2Currentdestination

#definerDMASKTRIG2(*(volatileunsigned*)0x4b0000a0)//DMA2Masktrigger

#definerDISRC3 (*(volatileunsigned*)0x4b0000c0)//DMA3Initialsource

#definerDISRCC3 (*(volatileunsigned*)0x4b0000c4)//DMA3Initialsourcecontrol

#definerDIDST3 (*(volatileunsigned*)0x4b0000c8)//DMA3InitialDestination

#definerDIDSTC3 (*(volatileunsigned*)0x4b0000cc)//DMA3InitialDestinationcontrol

#definerDCON3 (*(volatileunsigned*)0x4b0000d0)//DMA3Control

#definerDSTAT3 (*(volatileunsigned*)0x4b0000d4)//DMA3Status

#definerDCSRC3 (*(volatileunsigned*)0x4b0000d8)//DMA3Currentsource

#definerDCDST3 (*(volatileunsigned*)0x4b0000dc)//DMA3Currentdestination

#definerDMASKTRIG3(*(volatileunsigned*)0x4b0000e0)//DMA3Masktrigger

//CLOCK&POWERMANAGEMENT 7

#definerLOCKTIME (*(volatileunsigned*)0x4c000000)//PLLlocktimecounter

#definerMPLLCON (*(volatileunsigned*)0x4c000004)//MPLLControl//系统主频配置寄存器基地址

#definerUPLLCON (*(volatileunsigned*)0x4c000008)//UPLLControl//USB时钟频率配置寄存器基地址

#definerCLKCON (*(volatileunsigned*)0x4c00000c)//Clockgeneratorcontrol

#definerCLKSLOW (*(volatileunsigned*)0x4c000010)//Slowclockcontrol

#definerCLKDIVN (*(volatileunsigned*)0x4c000014)//Clockdividercontrol

#definerCAMDIVN (*(volatileunsigned*)0x4c000018) //USB,CAMClockdividercontrol

//LCDCONTROLLER 18

#definerLCDCON1 (*(volatileunsigned*)0x4d000000)//LCDcontrol1

#definerLCDCON2 (*(volatileunsigned*)0x4d000004)//LCDcontrol2

#definerLCDCON3 (*(volatileunsigned*)0x4d000008)//LCDcontrol3

#definerLCDCON4 (*(volatileunsigned*)0x4d00000c)//LCDcontrol4

#definerLCDCON5 (*(volatileunsigned*)0x4d000010)//LCDcontrol5

#definerLCDSADDR1 (*(volatileunsigned*)0x4d000014)//STN/TFTFramebufferstartaddress1

#definerLCDSADDR2 (*(volatileunsigned*)0x4d000018)//STN/TFTFramebufferstartaddress2

#definerLCDSADDR3 (*(volatileunsigned*)0x4d00001c)//STN/TFTVirtualscreenaddressset

#definerREDLUT (*(volatileunsigned*)0x4d000020)//STNRedlookuptable

#definerGREENLUT (*(volatileunsigned*)0x4d000024)//STNGreenlookuptable

#definerBLUELUT (*(volatileunsigned*)0x4d000028)//STNBluelookuptable

#definerDITHMODE (*(volatileunsigned*)0x4d00004c)//STNDitheringmode

#definerTPAL (*(volatileunsigned*)0x4d000050)//TFTTemporarypalette

#definerLCDINTPND (*(volatileunsigned*)0x4d000054)//LCDInterruptpending

#definerLCDSRCPND (*(volatileunsigned*)0x4d000058)//LCDInterruptsource

#definerLCDINTMSK (*(volatileunsigned*)0x4d00005c)//LCDInterruptmask

#definerLPCSEL (*(volatileunsigned*)0x4d000060)//LPC3600Control

#definePALETTE 0x4d000400 //Palettestartaddress

//NandFlash 17

#definerNFCONF (*(volatileunsigned*)0x4E000000) //NANDFlashconfiguration

#definerNFCONT (*(volatileunsigned*)0x4E000004) //NANDFlashcontrol

#definerNFCMD (*(volatileunsigned*)0x4E000008) //NANDFlashcommand

#definerNFADDR (*(volatileunsigned*)0x4E00000C) //NANDFlashaddress

#definerNFDATA (*(volatileunsigned*)0x4E000010) //NANDFlashdata

#definerNFDATA8 (*(volatileunsignedchar*)0x4E000010) //NANDFlashdata

#definerNFMECCD0 (*(volatileunsigned*)0x4E000014) //NANDFlashECCforMainArea

#definerNFMECCD1 (*(volatileunsigned*)0x4E000018)

#definerNFSECCD (*(volatileunsigned*)0x4E00001C) //NANDFlashECCforSpareArea

#definerNFSTAT (*(volatileunsigned*)0x4E000020) //NANDFlashoperationstatus

#definerNFESTAT0 (*(volatileunsigned*)0x4E000024)

#definerNFESTAT1 (*(volatileunsigned*)0x4E000028)

#definerNFMECC0 (*(volatileunsigned*)0x4E00002C)

#definerNFMECC1 (*(volatileunsigned*)0x4E000030)

#definerNFSECC (*(volatileunsigned*)0x4E000034)

#definerNFSBLK (*(volatileunsigned*)0x4E000038) //NANDFlashStartblockaddress

#definerNFEBLK (*(volatileunsigned*)0x4E00003C) //NANDFlashEndblockaddress

//UART 45

#definerULCON0 (*(volatileunsigned*)0x50000000)//UART0Linecontrol

#definerUCON0 (*(volatileunsigned*)0x50000004)//UART0Control

#definerUFCON0 (*(volatileunsigned*)0x50000008)//UART0FIFOcontrol

#definerUMCON0 (*(volatileunsigned*)0x5000000c)//UART0Modemcontrol

#definerUTRSTAT0 (*(volatileunsigned*)0x50000010)//UART0Tx/Rxstatus

#definerUERSTAT0 (*(volatileunsigned*)0x50000014)//UART0Rxerrorstatus

#definerUFSTAT0 (*(volatileunsigned*)0x50000018)//UART0FIFOstatus

#definerUMSTAT0 (*(volatileunsigned*)0x5000001c)//UART0Modemstatus

#definerUBRDIV0 (*(volatileunsigned*)0x50000028)//UART0Baudratedivisor

#definerULCON1 (*(volatileunsigned*)0x50004000)//UART1Linecontrol

#definerUCON1 (*(volatileunsigned*)0x50004004)//UART1Control

#definerUFCON1 (*(volatileunsigned*)0x50004008)//UART1FIFOcontrol

#definerUMCON1 (*(volatileunsigned*)0x5000400c)//UART1Modemcontrol

#definerUTRSTAT1 (*(volatileunsigned*)0x50004010)//UART1Tx/Rxstatus

#definerUERSTAT1 (*(volatileunsigned*)0x50004014)//UART1Rxerrorstatus

#definerUFSTAT1 (*(volatileunsigned*)0x50004018)//UART1FIFOstatus

#definerUMSTAT1 (*(volatileunsigned*)0x5000401c)//UART1Modemstatus

#definerUBRDIV1 (*(volatileunsigned*)0x50004028)//UART1Baudratedivisor

#definerULCON2 (*(volatileunsigned*)0x50008000)//UART2Linecontrol

#definerUCON2 (*(volatileunsigned*)0x50008004)//UART2Control

#definerUFCON2 (*(volatileunsigned*)0x50008008)//UART2FIFOcontrol

#definerUMCON2 (*(volatileunsigned*)0x5000800c)//UART2Modemcontrol

#definerUTRSTAT2 (*(volatileunsigned*)0x50008010)//UART2Tx/Rxstatus

#definerUERSTAT2 (*(volatileunsigned*)0x50008014)//UART2Rxerrorstatus

#definerUFSTAT2 (*(volatileunsigned*)0x50008018)//UART2FIFOstatus

#definerUMSTAT2 (*(volatileunsigned*)0x5000801c)//UART2Modemstatus

#definerUBRDIV2 (*(volat