FSK综合设计实验教材.docx

《FSK综合设计实验教材.docx》由会员分享,可在线阅读,更多相关《FSK综合设计实验教材.docx(16页珍藏版)》请在冰豆网上搜索。

FSK综合设计实验教材

实验九综合设计性实验

------二进制频移键控(FSK)调制与解调

频移键控(FSK)是用不同频率的载波来传送数字信号,并用数字基带信号控制载波信号

的频率。

二进制频移键控是用两个不同频率的载波来代表数字信号的两种电平。

接收端收到不同的载波信号再进行逆变换成为数字信号,完成信息传输过程。

8.1FSK信号的产生

FSK信号的产生有两种方法,直接调频法和频率键控法。

1.直接调频法

直接调频法是用数字基带信号直接控制载频振荡器的振荡频率。

直接调频法实现电路有许多,一般采用的控制方法是:

当基带信号为正时(相当于“1”码),改变振荡器谐振回路的参数(电容或者电感数值),使振荡器的振荡频率提高(设为f1);当基带信号为负时(相当于“0”码),改变振荡器谐振回路的参数(电容或者电感数值),使振荡器的振荡频率降低(设为f2);从而实现了调频,这种方法产生的调频信号是相位连续的。

虽然实现方法简单,但频率稳定度不高,同时频率转换速度不能太快。

2.频率键控法

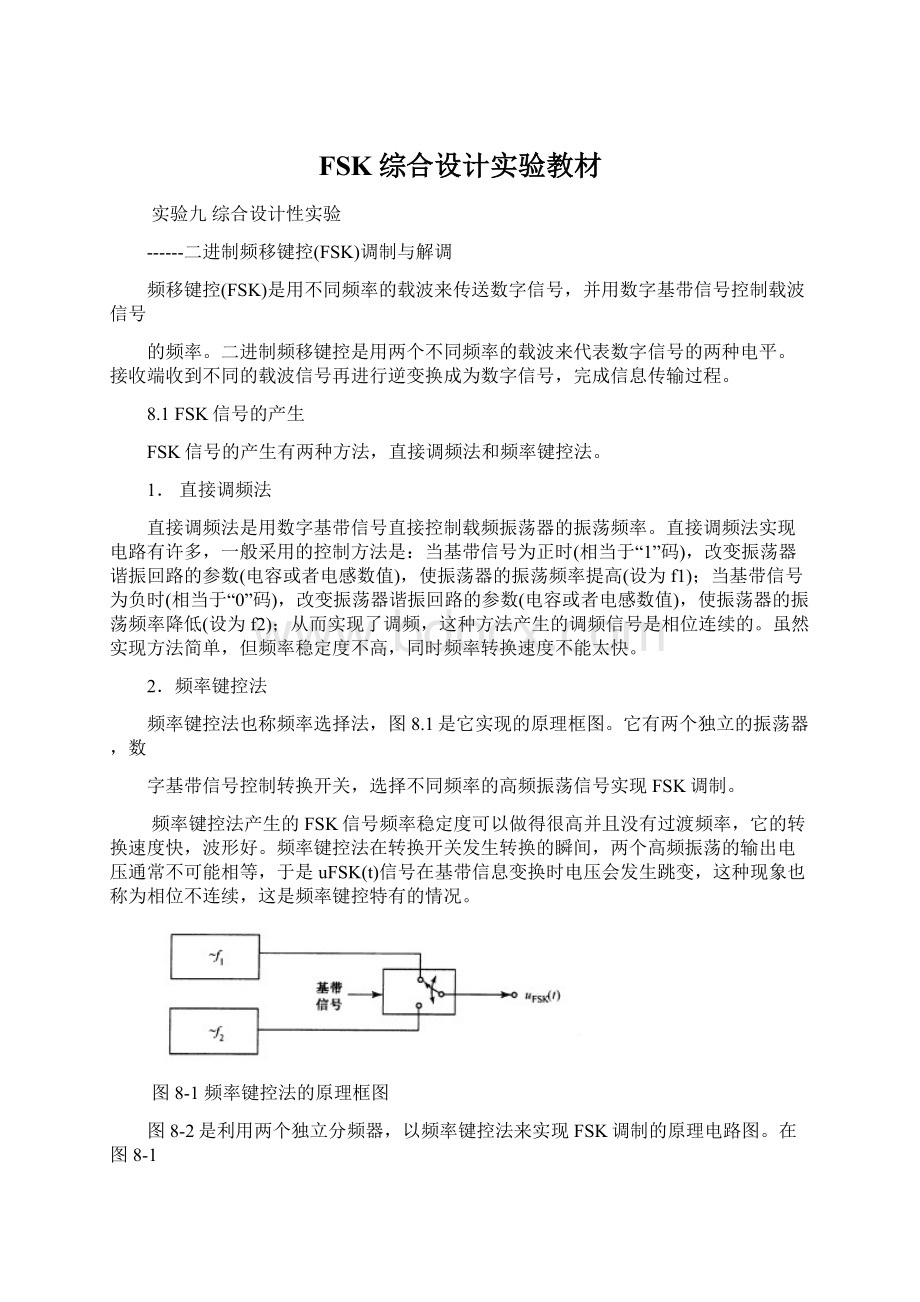

频率键控法也称频率选择法,图8.1是它实现的原理框图。

它有两个独立的振荡器,数

字基带信号控制转换开关,选择不同频率的高频振荡信号实现FSK调制。

频率键控法产生的FSK信号频率稳定度可以做得很高并且没有过渡频率,它的转换速度快,波形好。

频率键控法在转换开关发生转换的瞬间,两个高频振荡的输出电压通常不可能相等,于是uFSK(t)信号在基带信息变换时电压会发生跳变,这种现象也称为相位不连续,这是频率键控特有的情况。

图8-1频率键控法的原理框图

图8-2是利用两个独立分频器,以频率键控法来实现FSK调制的原理电路图。

在图8-1

中,与非门3和4起到了转换开关的作用。

当数字基带信号为“1”时,与非门4打开,f1输出,当数字基带信号为“0”时,与非门3打开,f2输出,从而实现了FSK调制。

图8-2利用独立分频器的键控法实现FSK调制

频率键控法也常常利用数字基带信号去控制可变分频器的分频比来改变输出载波频率,从而实现FSK调制。

图8-3是一个11/13可控分频器原理图。

当数字基带信号为“1”时,第四级双稳态电路输出的反馈脉冲被加到第一级和第二级双稳态电路上,此时分频比为13;当基带信号为“0”时,第四级双稳态电路输出的反馈脉冲被加到第一级和第三级双稳态电路上,分频比变为11。

由于分频比的改变,使输出信号频率发生变化,从而实现了FSK调制。

采用可变分频器产生的FSK信号相位通常是连续的,因此在基带信息变化时,FSK信号会出现过渡频率。

为减小过渡时间,可变分频器应工作于较高的频率,并在可变分频器后再插入固定分频器,使输出频率满足FSK信号要求的频率。

图8-3利用可控分频器实现FSK调制

FSK信号有相位不连续和相位连续两种情况,相位不连续的FSK信号可以视为两个频率分别为/1和/2的ASK信号的叠加,如图8-4所示。

图8-4相位不连续的FSK信号可视为两个不同频率的ASK信号叠加

8.2基于VHDl硬件描述语言的FSK频率键控法调制程序设计

1.FSK调制的建模方框图及电路符号

FSK调制方框图如图8-5所示,FSK调制电路的VHDL建模符号如图8-6所示。

有了

ASK调制的建模方法基础,再根据FSK调制原理,对FSK信号产生的建模框图就容易理解了。

FSK调制的核心部分包括分频器、二选一选通开关等。

图8-5中的两个分频器分别产生两路数字载波信号;二选一选通开关的作用是:

以基带信号作为控制信号,当基带信号为“0”,选通载波f1;当基带信号为“1”时,选通载波f2从选通开关输出的信号就是数字FSK信号。

图中没有包含模拟电路部分,调制信号为数字信号。

图8-5FSK调制方框图

图8-6FSK调制电路的VHDL建模符号

2.FSK调制VHDL程序及仿真

——文件名:

PL_FSK

——功能:

基于VHDL硬件描述语言,对基带信号进行FSK调制

libraryieee;

useieee.std_logic_arith.all;

useieee.std_logic_1164.a11;

useieee.std_logic_unsigned.all;

entityPL_FSKis

port(clk:

instd_logic;——系统时钟

start:

instd_logic;——开始调制信号

x:

instdlogic;——基带信号

y:

outstd_logic);——调制信号

endPL_FSK;

architecturebehaveofPL_FSKis

signalql:

integerrange0to11;——载波信号n的分频计数器

signalq2:

integerrange0to3;——载波信号n的分频计数器

signalf1,f2:

std_logic;——载波信号f1,f2

begin

process(clk)——此进程通过对系统时钟clk的分频,得到载波f1

begin

ifclk'event.andclk=‘1’,then

ifstart=‘1’thenql<=0;

elsifql<=5thenf1<=‘1’;q1<=q1+1;

——改变q1后面的数字可以改变,载波f1的占空比

elsifql=11thenf1<=‘0’;q1<=0;

——改变q1后面的数字可以改变,载波f1的频率

elsef1<=‘0’;q1<=q1+1;

endif;

endif;

endprocess;

process(clk)——此进程通过对系统时钟clk的分频,得到载波f2

begin

ifclk'eventandclk=‘1’,then

ifstart=‘0’thenq2<=0;

elsifq2<=0thenf2<=‘1’;q2<=q2+1;

——改变q2后面的数字可以改变,载波f2的占空比

elsifq2=1thenf2<=‘0’;q2<=0;

——改变q2后面的数字可以改变,载波f2的频率

elsef2<=‘0’,q2<=q2+1;

endif;

endif;

endprocess;

process(clk,x)——此进程完成对基带信号的FSK调制

begin

ifclk'eventandclk=‘1’then

ifx=‘0’theny<=fl;

——当输入的基带信号x=‘0’时,输出的调制信号y为f1

elsey<=f2;——当输入的基带信号X=‘1’时,输出的调制信号y为f2

endif;

end避

endprocess;

endbehav;

3.FSK调制VHDL程序仿真图

FSK调制VHDI程序仿真图如图8-7所示。

(a)FSK调制VHDL程序仿真图

注:

①载波f1、f2分别是通过对clk的12分频和2分频得到的;

②基带码长为载波f1的2个周期,为载波f2的6个周期;

⑧输出的调制信号y在时间上滞后于载波信号一个clk,滞后于系统时钟2个clk。

(b)FSK调制VHDL程序仿真局部放大图

图8-7FSK调制VHDL程序仿真图

8.3FSK信号的解调

数字频率键控(FSK)信号常用的解调方法有很多种,如同步(相干)解调法、过零检测

法和差分检波法等。

1.同步解调法

同步解调中,FSK信号解调原理方框如图8—21所示。

图8-8FSK信号同步解调原理方框图

从图8—8可见,FSK信号的同步解调器分成上、下两个支路,输入的FSK信号经过f1和f2,两个带通滤波器后变成了上、下两路ASK信号,之后其解调原理与ASK类似,但判决需对上、下两支路比较来进行。

假设上支路低通滤波器输出为,下支路低通滤波器输出为x2,

则判决准则为

x1-x2>0,判输入为f1信号

(8-1)

x1-x2<0,判输入为f2信号

当输入的FSK信号振荡频率为f1时,上支路经带通后有正弦信号Acos2πf1t存在,与ASK系统接收到“1”码时的情况相似,经过低通滤波器,x1=A。

而下支路带通滤波器输出为0,与ASK系统接收到“0”码时情况相似,故x2=0,显然x1-x2=A-0>0,按判决准则判输入为fl;反之,当输入为f2时,x1=0,X2=A,x1-x2==0-A<0,按判决准则应判输入为f2。

因此可以判决出FSK信号。

2.包络解调法

FSK信号包络解调方框图如8-9所示。

从图8-9可见,FSK信号包络解调相当于两路ASK信号包络解调。

用两个窄带的分路滤波器分别滤出频率为f1及f2的高频脉冲,经包络检波后分别取出它们的包络。

把两路输出同时送到抽样判决器进行比较,从而判决输出基带数字信号。

设频率f1代表数字信号1,f2代表0,则抽样判决器的判决准则为

x1-x2>0,判输入为f1信号

x1-x2<0,判输入为f2信号

式中,x1和x2分别为抽样时刻两个包络检波器的输出值。

这里的抽样判决器,要比较x1、x2大小,或者说把差值x1-x2与零电平比较。

因此,有时称这种比较判决器的判决门限为零电平。

当FSK信号为f1时,上支路相当于ASK系统接收“1”码的情况,其输出x1为正弦波加窄带高斯噪声的包络,它服从莱斯分布。

而下支路相当于ASK系统接收“0”码的情况,输出x2为窄带高斯噪声的包络,它服从瑞利分布。

如果FSK信号为f2,上、下支路的情况正好相反,此时上支路输出的瞬时值服从瑞利分布,下支路输出的瞬时值服从莱斯分布。

由以上分析可知,无论输出的FSK信号是fl或f2,两路输出总是一路为莱斯分布,另一路为瑞利分布,而判决准则仍为式(8-1),因此可判决出FSK信号。

图8-9FSK信号包络解调方框图

3.过零检测法

过零检测法方框图及波形如图8-10所示,它是利用信号波形在单位时间内与零电平轴交叉的次数来测定信号频率。

输入的uFSK信号经限幅放大后成为矩形脉冲波,再经微分电路得到双向尖脉冲,然后整流得单向尖脉冲,每个尖脉冲表示信号的一个过零点,尖脉冲的重复频率就是信号频率的二倍。

将尖脉冲去触发一单稳电路,产生一定宽度的矩形脉冲序列,该序列的平均分量与脉冲重复频率成正比,即与输入信号频率成正比。

所以经过低通滤波器输出的平均分量的变化反映了输入信号频率的变化,这样就把码元“1”与“0”在幅度上区分开来,恢复出数字基带信号。

图8-10FSK过零检测法方框图及波形

8.4基于VHDL硬件描述语言的FSK频率键控法解调程序设计

1.FSK解调的建模原理

FSK解调方框图如图8-11所示,FSK解调电路的VHDL建模符号如图8-12所示。

该模型与ASK的解调模型类似。

其核心部分由分频器、寄存器、计数器和判决器组成。

图8-11中分频器的分频系数取值对应图8—5中的分频器1和分频器2中较小的分频系数值,也就是说FSK解调器的分频器输出为较高的那个载波信号。

由于f1和f2的周期不同,若设f1=2f2,且基带信号电平“1”,对应f1;基带信号电平“0”对应载波f2,则图8-11中计数器以f1为时钟信号,上升沿计数,基带信号“1”码元对应的计数个数为1/f1,基带信号“0”码元对应的计数个数为1/f2。

计数器根据两种不同的计数情况,对应输出“0”和“1”两种电平。

判决器以f1为时钟信号,对计数器输出信号进行抽样判决,并输出基带信号。

图中没有包含模拟电路部分,调制信号为数字信号形式。

图8-11FSK解调方框图

图8-12FSK解调电路的VHDL建模符号

2.FSK解调VHDL程序及注释

——文件名:

PL_PSK2

——功能:

基于VHDL硬件描述语言,对FSK调制信号进行解调

libraryieee;

useieee.st_logic_arith.all;

useieee.st_logic_1164.all;

useieee.st_logic_unsigned.all;

entityPL_PSK2is

port(clk:

instd_logic;——系统时钟

start:

instd_logic;——同步信号

x:

instd_logic;——调制信号

y:

outsrd_logic);——基带信号

endPL_FSK2;

architecturebehavofPL_FSK2is

signalq:

integerrange0to11;——分频计数器

signalxx:

std_logic;——寄存器

signalm:

integerrange0to5;——计数器

begin

process(clk)——对系统时钟进行q分频

begin

ifclk'eventandclk=‘1’thenxx<=x;

——在clk信号上升沿时,x信号对中间信号xx赋值

Ifstart=‘0’thenq<=0;——if语句完成Q的循环计数

elsifq=11thenq<=0;

elseq<=q+1;

endif;

endif;

endprocess;

process(xx,q)——此进程完成FSK解调

begin

ifq=11thenm<=0;——m计数器清零

elsifq=10then

ifm<=3theny<=0;——if语句通过对m大小,来判决y输出的电平

elsey<=‘1’;

endif;

elsifxx'eventandxx=‘1’thenm<=m+1;——计XX信号的脉冲个数

endif;

endprocess;

endbehav;

3.FSK解调VHDL程序仿真图及注释

FSK解调VHDL程序仿真图及注释如图8-13所示。

注:

①在q=11时,m清零。

②在q=10时,根据m的大小,进行对输出基带信号y的电平的判决。

③在q为其他值时,计数器m计下xx(寄存x信号)的脉冲数。

④输出信号y滞后输入信号x10个clk。

(b)FSK解调VHDL程序仿真局部放大图

图8-13FSK解调VHDL程序仿真图及注释

附:

ALTERA开发环境使用入门

世界各大FPGA/EPLD生产商都有自己的EDA开发环境,也有专业的第三方EDA软件。

ALTERA公司的MAX+plusII是其中较常被使用的EDA开发环境,它操作方便、功能强大,提供了原理图输入和VHDL语言输入功能,在环境中可以完成编译、查错、设计驱动信号、逻辑功能模拟、时序功能模拟、对FPGA/EPLD芯片编程等功能。

下面以VHDL语言输入设计为例,一步一步描述在MAX+plusII开发环境中如何完成EDA的设计流程。

1.建立工作文件目录。

我们将一个设计称为一个项目,在硬盘上建立一个工作文件目录,目录名应重名命名为英文名。

以后与该项目有关的所有设计文件都保存在此目录。

MAX+plusII软件安装好后,会在硬盘上生成一个MAX2WORK目录,我们在MAX2WORK之下建立一个工作文件目录,名命为“EX”,本例中所有文件都存在此目录下。

2.新建设计文件。

启动MAX+plusII开发环境,选择菜单[File]下的[New]功能,出现对话框,要求确认“新建”何种类型的文件,有四种类型文件可选择,因为我们新建VHDL文本,所以选择第三个“TextEditorfile”。

对话框如图。

确认对话框后,开发环境生成一空的文本编辑窗口用于输入VHDL文本。

3.输入VHDL设计描述。

在窗口输入如下VHDL程序,本例完成的是一个一位全加器的功能。

LIBRARYIEEE;

USEIEEE.std_logic_1164.ALL;

ENTITYEX1IS

PORT(

a:

INSTD_LOGIC;

b:

INSTD_LOGIC;

c_in:

INSTD_LOGIC;

sum:

OUTSTD_LOGIC;

c_out:

OUTSTD_LOGIC

);

ENDEX1;

ARCHITECTUREbehvOFEX1IS

BEGIN

sum<=aXORbXORc_in;

c_out<=(aANDb)OR(c_inAND(aORb));

ENDbehv;

其中“a”和“b”表示全加器的“输入1”和“输入2”,“c_in”表示“前级进位输入”,

“sum”表示全加器的“和”,“c_out”表示全加器的进位。

4.保存VHDL文本。

输入VHDL语言后,选择菜单[File]下的[SaveAs]功能,出现如图对话框,在“Directories”中选择刚才新建的项目文件目录“C:

\MAX2WORK\EX”,在“FileName:

”处填上文件名“EX1.VHD”。

按“OK”确认退出。

5.将当前文件设为项目的主文件。

因为在EDA设计中,一个项目按功能不同或层次不同,可以包括很多设计描述文件,这些文件可以是原理图也可以是VHDL,也可以是混合的。

设计时,可以按功能分模块来完成,也可以自底向上逐步完成。

将当前文件设为项目的主文件后,以后所进行的编译、仿真、测试都是以此文件为顶层文件,包括其下层文件来完成的,而此文件的上层文件和并行文件都不受影响。

选择菜单[File]的[Project]的“SetProjecttoCurrentFile”

功能可以将当前文件设成项目的主文件。

6.选择设计所使用的器件。

这里的器件就是指每个设计所使用的FPGA或EPLD芯片,ALTERA公司具有代表性的FPGA为FLEX10K系列的EPF10K10LC84-4。

具有代表性的EPLD为MAX7000S系列的EPM7128SLC84-15。

选择菜单[Assign]的[Device...]功能,出现如图对话框,在“DeviceFamily”中选择ALTERA公司的器件系列,当选定了器件系列后,“Devices”框内出现该系列的各种芯片,如果“ShowOnlyFastestSpeedGrades”被选中,则器件框中只显示最快速度的器件,去掉“只显

示最快芯片”前的勾,器件框中显示该系列所有芯片。

本例中,我们选择MAX7000S系列中的EPM7128SLC84-15芯片。

7.编译设计项目。

选择[MAX+plusII]菜单的[Compiler]功能,出现如图窗口,按“Start”开始编译。

如果有错,程序会自动停止并指出错误,用户解决错误后,再重新编译,直到全部编译完成。

8.建立输入控制波形。

在对设计进行验证时,要给输入信号加上驱动,用波形文件来描述驱动信号的高低状态和前后时序,并加在芯片相应的管脚上。

选择[File]的[New]功能,在对话框中选择

“WaveformEditorfile”,开发环境打开一空的波形编辑窗口。

9.加入信号接点。

在窗口中加入需要驱动的信号和想要观察的信号,选择波形窗口上方的[Node]菜单的[EnterNodefromSNF]功能。

出现如图对话框,按“LIST”按钮,在左边“Available

Nodes&Groups”出现设计中所有信号名,可以在窗口中选中其中想要观察的信号和需要驱动的信号,按“=>”按钮将信号加入右边选中窗口。

确认退出。

10.编辑波形。

波形窗口中已经有需要驱动的信号的想要观察信号的信号名,现在我们定义需要驱

动的信号状态和时序,在本例中只有三路输入信号:

c_in、b、a,三路信号共有8个状态,在波形定义时,只要列举出这8个状态就可以从输出波形中观察到设计的功能是否正确。

在波形定义窗口中,选中将要定义的信号名,按鼠标右键,选择弹出菜单的[Overwrite]下的[Clock...]功能,出现时钟脉冲波形定义对话框,来定义等宽度的时钟信号,“StartingValue”表示该信号的初始状态,“MultipliedBy”表示信号脉冲的宽度。

11.保存波形文件。

选择菜单[File]的[Saveas]功能将波形文件保存下来,便于下次模拟时调用。

波形文件的后缀为“.SCF”。

12.软件模拟仿真。

当有了驱动信号以后,就可以对设计进行模拟仿真,验证设计是否正确。

选择[MAX+plusII]菜单的[Simulator]功能,出现如图对话框,按“Start”按钮,开始运行软件模拟仿真,可以看到仿真输出。

“Value”表示标尺位置上各信号的当前值,在窗口内拖动标尺,观察各信号的当前值是否符合设计要求。

在波形窗口中,上方有几个显示框用来显示标尺的时间位置,鼠标的时间位置及两者的时间差,可以用这种方法来观察两信号间的延时。

如果信号过多,可用垂直滚动棒移动窗口,如果想要观察的时间不在当前窗口内,可用水平滚动棒将窗口移动到相应的时间段,用窗口左边的放大、缩小功能可以将波形时间展开、收缩,以观察波形的局部细节或全局概况。

13.时序分析。

为了能了解软件模拟仿真中各信号之间的具体延时量,可以用MAX+plusII提供的时序分析功能来做时序分析。

选择[MAX+plusII]菜单的[TimingAnalyzer]功能,出

现如图对话框,按“Start”按钮,启动时序分析,分析完成后,

各信号之间的延时时间以表格形式显示出来。

14.将信号锁定到芯片的管脚。

前面所做的只是逻辑功能的软件模拟仿真,即使模拟仿真、时序分析都达

到设计要求,这只是理论上的结果,实际硬件的执行与软件模拟不一定完全一样,最后必须做硬件的验证。

在做硬件验证时,各个输入、输出信号必须锁定到具体芯片的脚上,才能将外部信号加进来,将输出信号接出去,根据你的外部电路设计或根据EDA实验仪的要求,将设计中各个输入、输出信号锁定到芯片的管脚上。

选择菜单[Assign][Pin/Location/Chip...]功能,出现如图信号与芯片管脚锁定的对话框,在“NodeName”框内填入需要输入、输出的信号名,在“PinType”框内显示出该信号的输入、输出类型,在“Pin”复选框内选择芯片的管脚,按右下角的“Add”按钮将信号与管脚的锁定关系加入“ExistingPin/Location/ChipAssignments”框内,当所有的信号都加入后,按“OK”确认退出。

注意:

如果你的设计中有时钟信号、复位信号、输出允许信号等可以全局使用延时分析及结果信号与芯片管脚锁定对话框的信号,编译器会自动将这些信号分配到芯片的相应全局信号管脚,如果你锁定的管脚不是全局信号脚,在编译综合时,系统会提示有错,解决的方法是,选择[Assign]菜单下的[GlobalProjectSynthesis]功能,在弹出的对话框的“AutomaticGlobal”栏内,去掉所使用全局信号前的选中勾,使其不会被自动分配。

按“OK”钮确认退出。

15.重新编译设计项目。

当设计项目中的信号被锁定到芯片的各管脚上后,需要对项目重新进行编译,重新编译产生的数据文件就会包含管脚的定义。

选择[MAX+plusII]菜单的[Compiler]功能,出现编译窗口,按窗口内的“Start”按钮,重新编译。

16.数据下载到芯片上。

当用软件仿真验证设计的电路工作正常。

就可以将编译产生的位图文件编程下载到F