完整word版实验五 指令调度和延迟分支.docx

《完整word版实验五 指令调度和延迟分支.docx》由会员分享,可在线阅读,更多相关《完整word版实验五 指令调度和延迟分支.docx(16页珍藏版)》请在冰豆网上搜索。

完整word版实验五指令调度和延迟分支

实验5指令调度和延迟分支

一.实验目的

(1)加深对指令调度技术的理解。

(2)加深对延迟分支技术的理解。

(3)熟练掌握用指令调度技术解决流水线中的数据冲突的方法。

(4)进一步理解指令调度技术对CPU性能的改进。

(5)进一步理解延迟分支技术对CPU性能的改进。

二.实验内容和步骤:

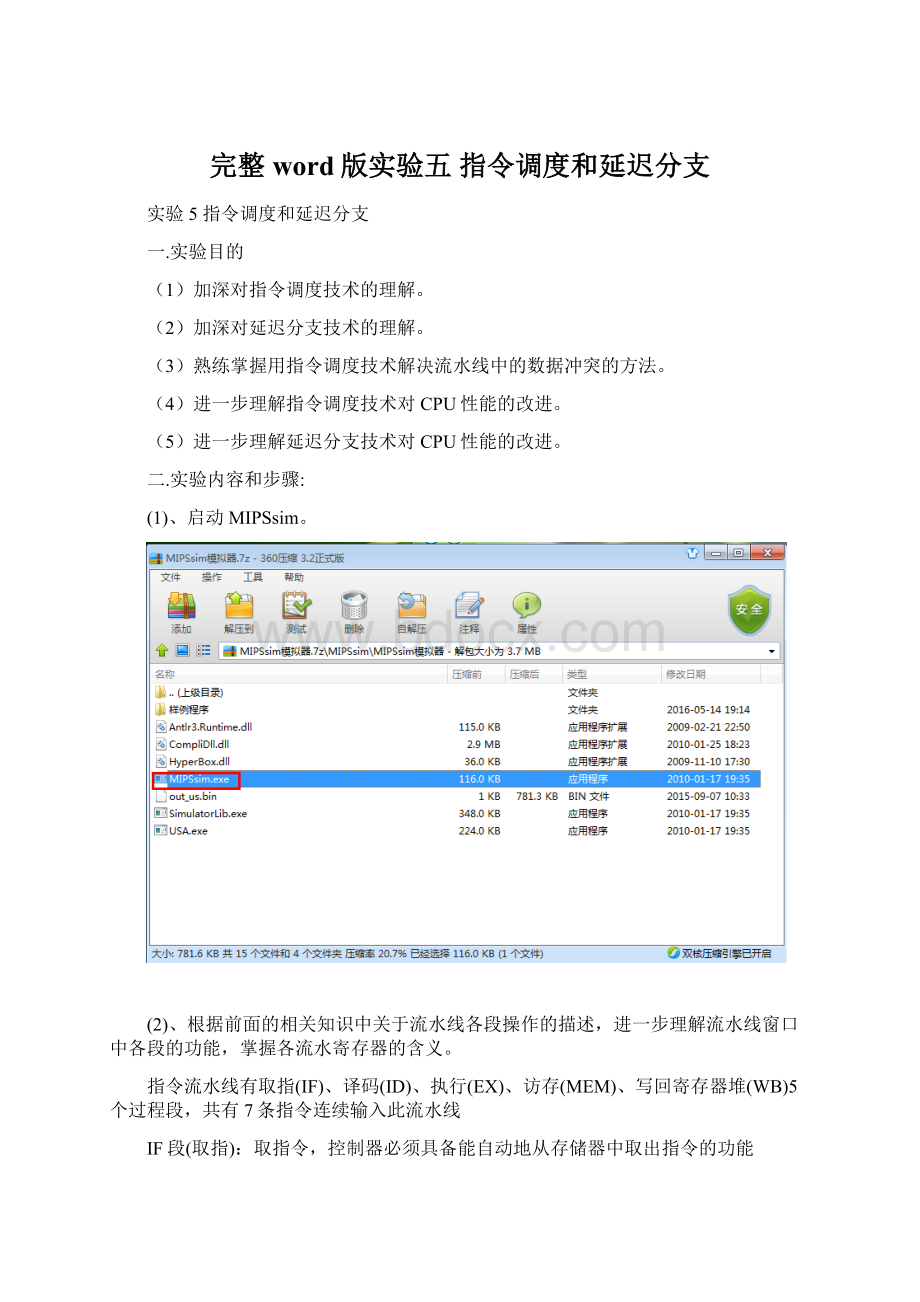

(1)、启动MIPSsim。

(2)、根据前面的相关知识中关于流水线各段操作的描述,进一步理解流水线窗口中各段的功能,掌握各流水寄存器的含义。

指令流水线有取指(IF)、译码(ID)、执行(EX)、访存(MEM)、写回寄存器堆(WB)5个过程段,共有7条指令连续输入此流水线

IF段(取指):

取指令,控制器必须具备能自动地从存储器中取出指令的功能

ID段(译码):

指令译码、读寄存器

EX段(执行):

执行、访存有效地址字段

MEM段(访存):

存储器访问

WB(写回寄存器堆):

结果写回寄存器

在该窗口中,每一个矩形方块代表一个流水段,它们用不同的颜色填充。

在该窗口的左侧是IF到WB段,其右边为浮点部件。

浮点部件分有浮点加法部件(fadd)、浮点乘法部件(fmul)和浮点除法部件(fdiv)三种。

在菜单“配置”“常规配置”中修改浮点部件个数,可看到该窗口中对应类型的浮点部件个数会发生相应的变化。

(3)、选择“配置”->“流水方式”选项,使模拟器工作于流水方式下。

(4)、用指令调度技术解决流水线中的数据冲突。

1)启动MIPSsim。

2)加载schedule.s。

3)关闭定向功能。

4)执行所载入的程序。

通过查看统计数据和时钟周期图,找出并记录程序执行过程中各种冲突发生的次数、发生冲突的指令组合以及程序执行的总时钟周期数。

调度前:

RAW发生的冲突周期数:

2、3、5、6、8、9、11、12、15、16、18、19、21、22、25、26

由以上可知:

RAW数据冲突发生了16次,其中load停顿6次,自陷停顿1次,停顿周期总数17次

执行过程中各种冲突发生次数:

16次

程序执行的总时钟周期数:

33次

发生冲突的指令组合:

TEQ$r0,$r0

ADDIU$r1,$r0,56

LW$r2,0($r1)与上条写后读冲突;

ADD$r4,$r0,$r2与上条指令写后读冲突;

SW$r4,0($r1)与上条指令写后读冲突;

LW$r6,4($r1)

ADD$r8,$r6,$r1与上条指令写后读冲突;

MUL$r12,$r10,$r1

ADD$r16,$r12,$r1与上条指令写后读冲突;

ADD$r18,$r16,$r1与上条指令组件冲突

SW$r18,16($r1)与上条指令写后读冲突;

LW$r20,8($r1)

MUL$r22,$r20,$r14与上条指令写后读冲突;

5)采用指令调度技术对程序进行指令调度,消除冲突。

将调度后的程序存到after-schedule.s中。

6)载入after-schedule.s。

7)执行该程序。

观察程序在流水线中的执行情况,记录程序执行的总时钟周期数。

调度后:

执行总时钟周期数为19,其中RAW停顿2次、load停顿0次、自陷停顿1次。

停顿总周期占总执行周期的15.78947%。

8)根据记录结果,比较调度前和调度后的性能。

论述指令调度对于提高CPU性能的作用。

根据记录结果:

指令调度后时钟总周期数从33降低到19,指令调度使指令顺序重新组合,可以消除部分的数据冲突,从而通过指令调度技术显著地提高了CPU的使用率,大大减少了指令冲突的次数,提高了CPU的性能。

指令调度的优劣直接影响CPU性能的发挥好坏,好的指令调度可以让停顿周期大幅度减少。

(5)、用延迟分支减少分支指令对性能的影响。

1)启动MIPSsim。

2)载入branch.s。

3)关闭延迟分支功能。

单击“配置”“延迟槽”,使处于关闭状态即为默认状态

4)执行该程序。

观察并记录发生分支延迟的时刻。

没有采用分支延迟:

答:

发生分支延迟的时刻为:

第18周期。

5)记录执行该程序所用的总时钟周期数。

执行周期总数为38,其中RAW停顿16次、load停顿4次、控制停顿0次、自陷停顿1次。

总停顿周期占总执行周期的50%。

6)假设延迟槽有1个,对branch.s进行指令调度,然后保存到“delayed-branch.s”中。

7)载入delayed-branch.s。

8)打开延迟分支功能。

单击“配置”“延迟槽”,使该项前有√来实现

9)执行该程序。

观察其时钟周期图。

采用分支延迟:

10)记录执行该程序所用的总时钟周期数。

总时钟周期数为26。

其中RAW停顿4次、load停顿2次、自陷停顿1次。

总停顿周期占总执行周期的19.23077%。

11)对比上述两种情况下的时钟周期图。

见上图

12)根据记录结果,比较没采用延迟分支和采用了延迟分支的性能之间的不同。

论述延迟分支对于提高CPU性能的作用。

答:

没采用分支延迟的时候周期总数为38,采用分支后的周期总数为26,可知,在使用延迟槽后,指令在运行到跳转指令时,不会出现延迟等待,则能够提高CPU的性能。

并且在使用延迟后,指令在运行到跳转指令时,不会出现延迟等待,则能够提高CPU的性能。

所以只要分支延迟槽中的指令是够用的,流水线中就没有停顿,这时延迟分支的方法就能很好的减少分支延迟。

所以放入延迟槽中的指令是很重要的,对CPU性能的影响是很显著的!

分支延迟槽(Branchdelayslot),简单地说就是位于分支指令后面的一条指令,不管分支发生与否其总是被执行,而且位于分支延迟槽中的指令先于分支指令提交(commit)。

3.实验结果分析

实验结论:

指令调度让指令顺序重新组织后能消除部分的数据冲突,指令调度的优劣直接影响CPU性能的发挥好坏,好的指令调度可以让停顿周期大幅度减少。

只要分支延迟槽中的指令时有用的,流水线中就没有停顿,这是延迟分支的方法就能很好的减少分支延迟,所以放入延迟槽中的指令是很重要的,对CPU性能的影响是显著的。