计算机组成原理第八章课后部分答案.docx

《计算机组成原理第八章课后部分答案.docx》由会员分享,可在线阅读,更多相关《计算机组成原理第八章课后部分答案.docx(7页珍藏版)》请在冰豆网上搜索。

计算机组成原理第八章课后部分答案

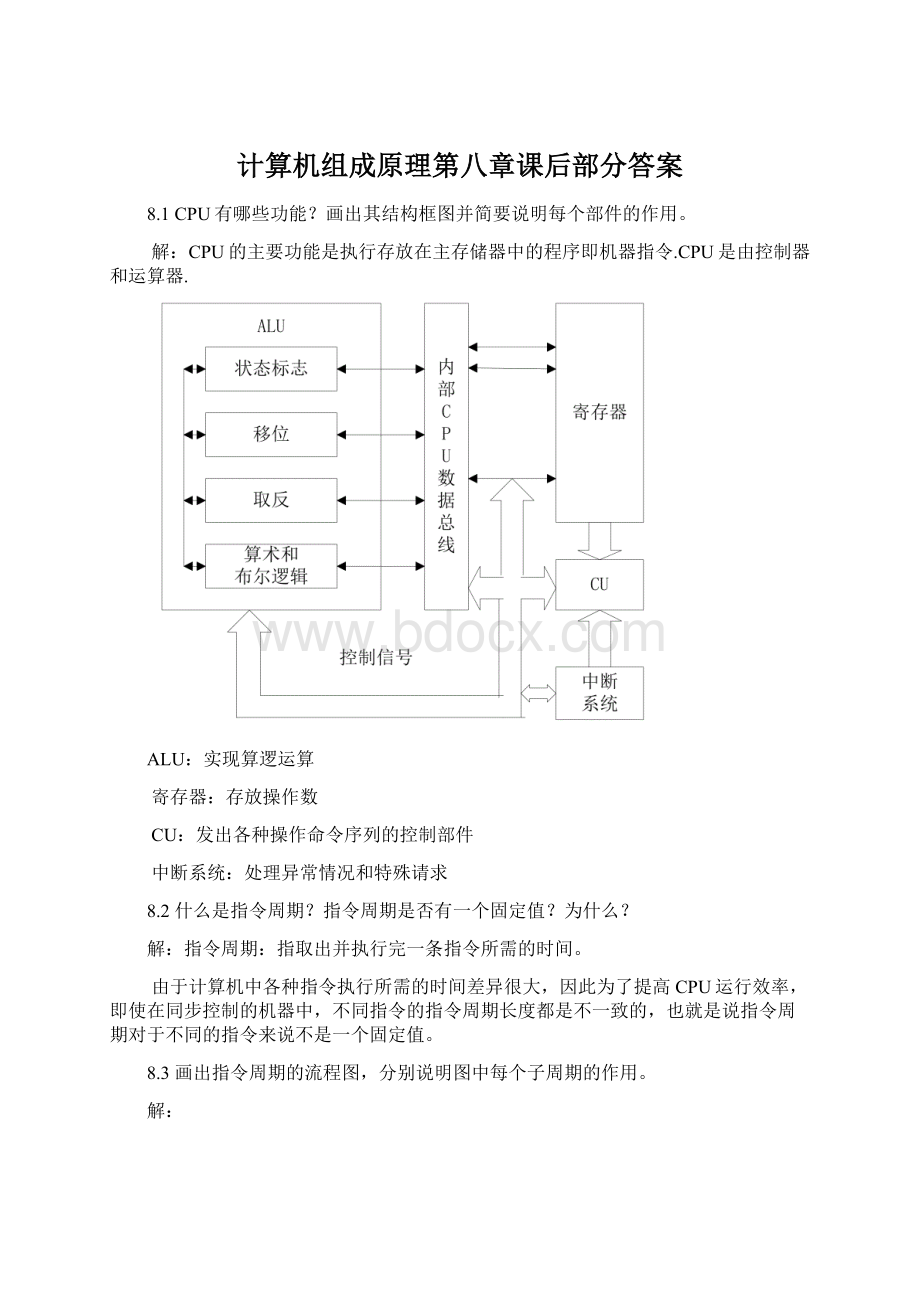

8.1CPU有哪些功能?

画出其结构框图并简要说明每个部件的作用。

解:

CPU的主要功能是执行存放在主存储器中的程序即机器指令.CPU是由控制器和运算器.

ALU:

实现算逻运算

寄存器:

存放操作数

CU:

发出各种操作命令序列的控制部件

中断系统:

处理异常情况和特殊请求

8.2什么是指令周期?

指令周期是否有一个固定值?

为什么?

解:

指令周期:

指取出并执行完一条指令所需的时间。

由于计算机中各种指令执行所需的时间差异很大,因此为了提高CPU运行效率,即使在同步控制的机器中,不同指令的指令周期长度都是不一致的,也就是说指令周期对于不同的指令来说不是一个固定值。

8.3画出指令周期的流程图,分别说明图中每个子周期的作用。

解:

指令周期流程图

取指周期:

取指令

间址周期:

取有效地址

执行周期:

取操作数(当指令为访存指令时)

中断周期:

保存程序断点

8.4设CPU内有这些部件:

PC、IR、SP、AC、MAR、MDR、CU。

(1)画出完成简洁寻址的取数指令“LDA@X”(将主存某地址单元的内容取至AC中)的数据流(从取指令开始)。

(2)画出中断周期的数据流。

解:

CPU中的数据通路结构方式有直接连线、单总线、双总线、三总线等形式,目前大多采用总线结构,直接连线方式仅适用于结构特别简单的机器中。

下面采用单总线形式连接各部件,框图如下:

(1)LDA@X指令周期数据流程图:

(2)中断周期流程图如下:

8.7什么叫系统的并行性?

粗粒度并行和细粒度并行有什么区别?

解:

并行性:

包含同时性和并发性。

同时性指两个或两个以上的事件在同一时刻发生,并发性指两个或多个事件在同一时间段发生。

即在同一时刻或同一时间段内完成两个或两个以上性质相同或性质不同的功能,只要在时间上存在相互重叠,就存在并行性。

粗粒度并行是指多个处理机上分别运行多个进程,由多台处理机合作完

成一个程序,一般算法实现。

细粒度并行是指在处理机的指令级和操作级的并行性。

8.8什么是指令流水?

画出指令二级流水和四级流水的示意图,它们中哪一个更

能提高处理器速度,为什么?

解:

指令流水:

指将一条指令的执行过程分为n个操作时间大致

相等的阶段,每个阶段由一个独立的功能部件来完成,这样n个部件可以同时执行n条指令的不同阶段,从而大大提高CPU的吞吐率。

指令二级流水和四级流水示意图如下:

二级指令流水示意图

四级指令流水示意图

四级流水更能提高处理机的速度

假设IF、ID、EX、WR每个阶段耗时为t,则连续执行n条指令

采用二级流水线时,耗时为:

4t+(n-1)2t=(2n+2)t

采用四级流水线时,耗时为:

4t+(n-1)t=(n+3)t

在n>1时,n+3<2n+2,可见四级流水线耗时比二级流水线耗时短,因此更能提高处理机速度。

8.10举例说明流水线中的几种数据相关。

解:

(1)写后读相关

(2)读后写相关

(3)写后写相关

8.15什么是中断?

设计中断系统需考虑哪些主要问题?

解:

中断:

指当出现需要时,CPU暂时停止当前程序的执行转而执行处理新情况的程序和执行过程。

即在程序运行过程中,系统出现了一个必须由CPU立即处理的情况,此时,CPU暂时中止程序的执行转而处理这个新的情况的过程就叫做中断。

设计中断系统需解决的问题:

(1)各中断源如何向CPU提出中断请求

(2)当对个中断源同时提出中断请求时,中断系统如何确定优先响

应哪个中断源的请求

(3)CPU在什么条件、什么时候、以什么方式来响应中断

(4)CPU响应中断后如何保护现场

(5)CPU响应中断后,如何停止原程序的执行而转入中断服务程序

的入口地址

(6)中断处理结束后,CPU如何恢复现场,如何返回到原程序的间断处。

(7)在中断处理过程中又出现了新的中断请求,CPU该如何处理。

8.17在中断系统中,INTR、INT、EINT这3个触发器各有何作用?

解:

INTR——中断请求触发器,用来登记中断源发出的随机性中断请求信号,以便为CPU查询中断及中断排队判优线路提供稳定的中断请求信号。

EINT——中断允许触发器,CPU中的中断总开关。

当EINT=1时,表示允许中断(开中断),当EINT=0时,表示禁止中断(关中断)。

其状态可由开、关中断等指令设置

。

INT——中断标记触发器,控制器时序系统中周期状态分配电路的一部分,表示中断周期标记。

当INT=1时,进入中断周期,执行中断隐指令的操作。

8.18什么是中断隐指令,有哪些功能?

解:

中断隐指令:

CPU响应中断之后,经过某些操作,转去执行中断服务程序。

这些操作是由硬件直接实现的

功能:

(1)保存断点

(2)暂不允许中断

(3)引出中断服务程序

8.21CPU在处理中断过程中,有几种方法找到中断服务程序的入口地址?

举例说明。

解:

(1)硬件向量法

(2)软件查询法

8.24现有A、B、C、D4个中断源,其优先级由高到低按A→B→C→D顺序排列。

若中断服务程序的执行时间为20μs,根据下图所示时间轴给出的中断源请求中断的时刻,画出CPU执行程序的轨迹。

解:

A、B、C、D的响优先级即处理优先级。

CPU执行程序的轨迹图如下:

8.25设某机有5个中断源L0、L1、L2、L3、L4,按中断响应的优先次序由高到低排序为L0→L1→L2→L4,现要求中断处理次序改为L1→L4→L2→L0→L3,根据下面的格式,写出各中断源的屏蔽字。

解:

各中断源屏蔽状态见下表:

中断源

屏蔽字

0

1

2

3

4

I0

1

0

0

1

0

I1

1

1

1

1

1

I2

1

0

1

1

0

I3

0

0

0

1

0

I4

1

0

1

1

1

表中:

设屏蔽位=1,表示屏蔽;屏蔽位=0,表示中断开放。

8.26设某机配有A、B、C3台设备,其优先级按A→B→C降序排列,为改变中断处理次序,它们的中断屏蔽字设置如下:

设备

屏蔽字

A

B

C

111

010

011

按下图所示时间轴给出的设备请求中断时刻,画出CPU执行程序的轨迹、设A、B、C中断服务程序的执行时间均为20μs

解:

A、B、C设备的响应优先级为A最高、B次之、C最低,处理优先级为A最高、C次之、B最低。

CPU执行程序的轨迹图如下:

如有侵权请联系告知删除,感谢你们的配合!