计算机组成原理与系统结构课后作业答案.docx

《计算机组成原理与系统结构课后作业答案.docx》由会员分享,可在线阅读,更多相关《计算机组成原理与系统结构课后作业答案.docx(29页珍藏版)》请在冰豆网上搜索。

计算机组成原理与系统结构课后作业答案

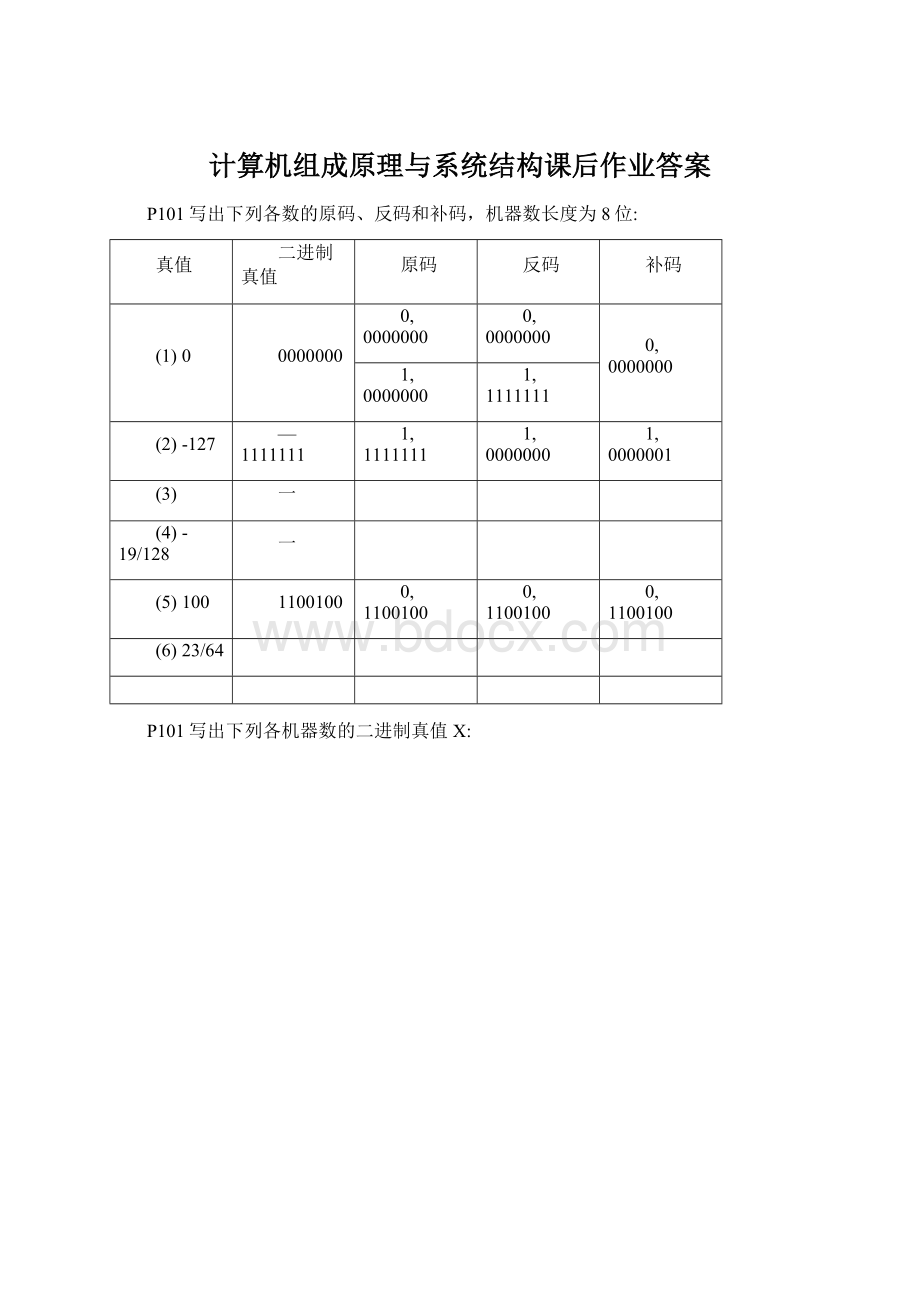

P101写出下列各数的原码、反码和补码,机器数长度为8位:

真值

二进制真值

原码

反码

补码

(1)0

0000000

0,0000000

0,0000000

0,0000000

1,0000000

1,1111111

(2)-127

—1111111

1,1111111

1,0000000

1,0000001

(3)

一

(4)-19/128

一

(5)100

1100100

0,1100100

0,1100100

0,1100100

(6)23/64

P101写出下列各机器数的二进制真值X:

(1)

[X]补=0,1001

(2)凶补=1,1001

(3)[X]原=0,1101

(4)[X]原=1,1101

(5)凶反=0,1011

(6)[X]反=1,1011

(7)[X]移=0,1001

(8)[X]移=1,1001

(9)[X]补=1,0000000

(10)[X]反=1,0000000

(11)凶原=1,0000000

(12)[X]移=1,0000000

P156X=Y=—(设机器数长度为8位)

[X]补=

[—X]补=

[2X]补=溢出

[—2X]补=溢出

[X/2]补=

[-X/2]补=

[Y]补=

[—丫]补=

[2Y]补=

[—2Y]补=

[Y/2]补=

[-Y/2]补=

[-Y/4]补=

P102:

、

阶码(6位移码)

尾数(6位原码)

(1)X=-25/64=,Y==

[X]浮=0,11111=7F9H[Y]浮=1,00010=897H

(2)

[Z]浮=9F4H=1,00111=-80

P102:

9、机器数字长16位

(1)

无符号整数:

0~216

1

(2)

原码表示的定点整数:

1,

111-

••11~0,

111…

11即

(215

1)〜215

(3)

补码表示的定点整数:

1,

00…

000~0,

111…

11即

215~

2151

(4)

补码表示的定点小数:

…

000~

•11即

1~1

215

(5)

非规格化浮点数:

N

M

R1

E

阶码(8位移码)

尾数(8位补码)

最大数=(127)2,1

阶码=1,1111111

尾数=

最小数=1221

阶码=1,1111111

尾数=

最大负数=2722

阶码=0,0000000

尾数=

最小正数=2722

阶码=0,0000000

尾数=

(6)规格化浮点数:

最大数=(127)2271

阶码=1,1111111

尾数=

最小数=1221

阶码=1,1111111

尾数=

最大负数=(2127)2

阶码=0,0000000

尾数=

最小正数=2122

阶码=0,0000000

尾数=

P156:

2、

(1)

P156:

4-1

4-2

P156:

5

5-1补码BOOT算法

5-2补码BOOT算法

P156:

6、

6-1原码恢复余数算法

6-1原码加减交替算法

6-2原码恢复余数算法

6-2原码加减交替算法

P1567-1补码加减交替算法

7-2补码加减交替算法

P156:

阶码(5位补码)

尾数(6位补码)

(1)X==Y==X+Y

X—Y:

1、对阶同上

2、尾数相减:

+

[EX-Y]补=

3、结果不需规格化

4、舍入处理:

[Ex-y]补=

[X-Y]=0,00111,00101

P108:

8—2

X==Y==

X—Y:

1、对阶同上

2、尾数相减:

+

[Ex-y]补=发生正溢

尾数右移,阶码加1

[Ex-y]补=

[Mx-y]=

3、结果不需规格化

4、舍入处理:

[Ex-y]补=

[X-Y]=1,11110,10100

P108:

9-1

(1)X==Y==X*Y

9-1X/Y:

9-2X*Y

9-2X/Y

《存储体系》

P225:

2、

(1)

64K1641664片

16K1

(2)

2ms

15.625s

128

(3)

128500ns64s

P225:

3、

(1)

最大主存容量=21816bit

(2)

18

共需216bit41664片芯片;若采用异步刷新,则刷新信号的周期为

64K1bit

2ms

15.625s

128

(3)

每块8子节,贝UCache容量为5122行,即卩c-9.Cache采用2路

8Byte

8Byte

组相联映射,则r=1。

主存容量为-一216块,即m=16每块包含4个字,

每字包含2个字节。

16

主存字节地址

主存字块标记

组地址

块内字地

址

字内字节地址

8

匕

8

2

1

16

主存字地址=462EH=00010001,10001011,10;因此该字映射到Cache的第139组。

(4)分析地址:

A

A6

A15

A4

A13

A2

A1

AI0

A

A

4

A

A

A

A

&

A

A

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0、

最小128K卜RAM

0

1

1

1

1

1

1

1

11

保留区

1

1

1

1

1

1

1

1丿

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

最高端8K

卜ROM

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1‘

16片SRAM芯片构成;

8组,组与组之间进行

分为

128K

128K的RAM区由

16bit

16K8bit

字扩展;每个组内有2片进行位扩展。

P225:

5、

平均访问时间tahctc(1hc)hm(tmQ(1九)(1hm)(JItp)

其中:

ta——平均访问时间;tc——Cache的存储周期;tm——主存的存储周期;tp—

—磁盘的存储周期;hcCache的命中率;hm主存的命中率。

ta90%20ns10%60%80ns10%40%(80ns1200ns)所以,

ta18ns4.8ns3.2ns48ns74ns

P168:

6、

命中率h

3900

3900100

100%

97.5%

平均访问时间

ta

ta

htc(1h)tm

97.5%40ns2.5%240ns39ns6ns45ns

e=tc/ta=40/45=8/9

P168:

7、

4路组相联映射,所以r=2

每块4字,所以b=2;每字32位,所以每字包含4字节。

Cache容量为

8K字节

44字节

512行29行,故c=9

主存容量为

4

16M字节

4字节

1M块

220块,故m=20

Cache

组地址

字块0

字块1

字块27-1

字块27

字块27+1

字块27-1

字块22冬7

字块22?

1

主存

1大*组

0

大*组

13

2-1大*组

1

标记

行0

标记

行3

标记

行4

标记

行7

标记

行29-4

标记

行29-1

Cache

0

27-1

(1)Cache共分为:

2^=29'2=128组。

主存字块标记

组地址

块内字地

址

字内字节地址

13

7

2

2

主存字节地址

"V

20

P226:

&

4路组相联映射,所以r=2每块64字,所以b=6;

Cache容量为签字

27行,故c=7

主存容量为

256K字

64字

212块,故m=12

Cache

组地址

主存字地址

8448字

64字

字块0

字块1

字块25-1

字块25

字块25+1

字块25-1

字块212-25

字块2121

主存

0

大*

组

1

大W

组

7

2-1大*组

1

0~8447,位于主存的哪几块内呢

标记

行0

标记

行3

标记

行4

标记

行7

标记

行27-4

标记

行27-1

Cache

0

25-1

132,即主存的第0~8447字位于连续的132块内。

132^商4余4,因此这

25块

132块连续分布在第0~4大组内,其中在第4大组中只有4块。

CPU第1次依次访问主存的0~8447字时不命中132次。

Cache的变化如图所示

CPU从第2次开始直到第21次访问主存的0~8447字时,每轮不命中20次(从第0~4大组的前4块都不命中,其余都命中),Cache的变化如图所示

第4组的4行

第1组的4行

第2组的4行

第3组的4行

第0大组

第1大组

第2大组

第3大组

Cache

第3组的4行

第4组的4行

第1组第2组的4行的4行

第0大组

第伏组

第2大组

第3大组

Cache

第3组

的4行

第0组的4行

第1组第2组的4行的4行

第0大组

第伏组

第2大组

第3大组

第4组

■第组—第

第3组

第4组

第0组

第1组

第3组

的4行

的4行

的4行

的4行

的4行

的4行

的4行

的4行

第0大组

第1大组

第2大组

第3大组

r

第0大组

第1大组

第2大组

第3大组

CacheCache

弟4组的4行

弟0组的4行

第1组第2组的4行的4行

第0大组

第1大组

第2大组

第3大组

Cache

因为tc如,

10

命中率h8448211322020100%176876I。

。

%99.7%

844821177408

设使用Cache比不使用Cache在速度上提高x倍,贝U

tm

htc(1h)(tmtc)

tm

tm

(1

h)

11tm

9.7倍

12、

地址

0019H

001AH

第一条转移指令:

《指令系统》

OP

MOD

DISP

指令

JMP

0006H

0019H001AH

(PC)=001AH执行该JMP指令后(PQ=001AH+0006H=0020H

第二条转移指令:

0019HJMP

001AH0025H

(PC)=001AH执行该JMP指令后(PQ=001AH+0025H=003FH

13、

寄存器-存储器型指令是指一个操作数来自寄存器,另一个操作数来自存储器。

(1)指令字长32位:

OP(6)

MOD(3)

REG(4)

ADDR(19)

直接寻址时EA=ADDR因此主存最大存储空间为219字。

(假设存储器按字编址)

间接寻址时EA=(ADDR,因此操作数地址存放在主存地址为0~219-1的单元内,假设存储器

按字编址,则EA应该是32位的地址,则主存最大存储空间为232字。

(2)其实用32位通用寄存器做基址寄存器,类似于80X86机器上存储器分段管理。

EA=32位基地址+偏移地址,所以EA是32位,则主存最大存储空间为232字。

16、设某机寄存器字长16位,用16进制表示,已知:

变址寄存器内容为0004H,PC

的内容为0003H,内存中部分单元内容如下:

地址:

内容

地址:

内容

0002H

OOOAH

0007H

000AH

0003H

0002H

0008H

0002H

0004H

0007H

0009H

0003H

0005H

0004H

000AH

0009H

0006H

0005H

OOOBH

0008H

指令为双字长指令,

格式如下:

操作码,寻址方式码,寄存器号(16位)0002H

直接地址/间接地址/立即数/相对位移量/形式地址(16位)0007H

若当前指令分别为下列寻址方式时,试求出操作数填入下表。

寻址方式

EA=

操作数

直接

0007H

000AH

间接

000AH

0009H

立即

/

0007H

变址

0004H+0007H

0008H

某机器字长16位,采用单字长指令,每个地址码6位。

试采用操作码扩展技术,设计14

条二地址指令,80条一地址指令,60条零地址指令。

请给出指令编码示意图。

双操作数指令格式:

OP(4位)

A1(6位)

A2(6位)

14条双操作数指令

op=oooo

OP=1101

A1(6位)

A2(6位)

单操作数指令格式:

OP(10位)

A1(6位)

80条双操作数指令

OP=00

OP=I1

OP=00

OP=11

A1(6位)

无操作数指令格式:

OP(16位)

60条双操作数指令

OP=QOO

OP=011

设某8位计算机,除HALT指令外,指令均为双字长,格式如下:

OP(4位)

M(2位)

Rd(2位)

A(8位)

假设:

PC的内容为22H;变址寄存器R3的内容为30H;主存部分单元的内容如下:

主存地址:

内容

主存地址:

内容

主存地址:

内容

20H:

22H

27H

:

02H

2EH:

00H

21H:

33H

28H

:

21H

2FH:

01H

22H:

35H

29H

:

0FH

30H:

02H

23H:

20H

2AH

:

48H

31H:

03H

24H:

01H

2BH

:

01H

32H:

04H

25H:

20H

2CH

:

55H

33H:

05H

26H:

1DH

2DH

:

F0H

34H:

06H

问:

CPU启动执行指令到停机,期间执行了哪几条指令写出每条指令的功能、寻址方式、操作数及执行结果。

解:

由于(PC)=22H,即程序的第一条指令地址为22H,从22H开始,执行到2DH(HALT指令)为止,共五条指令。

经分析,所有指令的目的操作数的寻址方式均为寄存器寻址方式,

为R1。

下面列出每条指令的功能、源操作数的寻址方式、源操作数及执行结果。

PC

指令

助记符

寻址方式

EA

源操作数

执行结果

22H

35H

MOV

直接寻址

20H

(20H)=22H

(R1)=22H

23H

20H

24H

01H

ADD

立即数

20H

(R1)=(R1)+20H

=42H

25H

20H

26H

1DH

SUB

变址寻址

(R3)+02H=32H

(32H)=04H

(R1)=(R1)-04H

=3EH

27H

02H

28H

21H

AND

立即数

0FH

(R1)=(R1)-0FH

=0EH-

29H

0FH

2AH

48H

JMP

相对

(PC+01H

=2CH+01H=2DH

(PC)=2DH

2BH

01H

2CH

55H

2DH

F0H

HALT

停机

《控制器》

6、设某机平均执行一条指令需要两次访问内存,平均需要三个机器周期,每个机器

周期包含4个节拍周期。

若机器主频为25MHz试回答:

1)若访问主存不需要插入等待周期,则平均执行一条指令的时间为多少

2)若每次访问内存需要插入2个等待节拍周期,则平均执行一条指令的时间是

又多少

解:

(1)

(2)

(2)机器周期

4

8MHz

平均每条指令?

机器周期

8、参见图7-41的数据通路,指令“INCR1”将R1寄存器的内容加1,画出其指令周期微程序流程图,并根据表7-11和表7-12写出每一条微指令码。

解:

INCR1;(R1)+1R1

BTO

OTB

FUNC

FS

S3-S0MCi

空

M6-M0

110

111

000

1

000000

0

0000010

011

000

010

0

000000

0

0000011

000

000

001

1

000000

0

0010000

001

011

000

0

000000

0

0000100

100

001

0

0

000000

0

0000001

9、根据图7-41所示的模型机结构和数据通路,写出以下指令从取址到执行的全部微操作序列,说明各条指令需要哪几个机器周期,需要几次访问内存及完成什么操作。

1)SUBA,R,该指令完成(A)-FH(A),源操作数一个为寄存器寻址,目标操作数为指令提供的内存有效地址A。

2)JMP偏移量,该指令完成PC+偏移量tPG

解:

(1)SUBA,R;(A)-FH(A)

指令为双字节格式:

所以,共需要8个机器周期,共访存4次。

(2)JMPDISP;(PC+DISiPC

所以,共需要7个机器周期,共访存2次

10、假设某机器主要部件有:

程序计数器PC指令寄存器IR、通用寄存器R0〜R3暂存器

DD1和DD2ALU移位器、存储器地址寄存器MAF及存储器M

1)要求采用单总线结构,画出包含上述部件的逻辑框图,并注明数据流动方向。

2)画出ADD(R1),(R2)指令在取指和执行阶段的操作步骤流程图。

R1寄存器存放目标操作数地址,R2寄存器存放源操作数地址。

3)写出各操作步骤所需的全部微操作命令。

解:

(1)

(2)

算术右移

(3)

取ADD旨令的微指令

1PC-B#、B-MARPC+1

2M-R#B-IR

3指令译码信号MA#有效执行ADD指令的微指令

1R2-B#、B-MAR

2M-R#,B-DD1

3R1-B#、B-MAR

4M-R#,B-DD2

5“+”,ALU-B#,M-W#

11、假设某机共有76条指令,平均每一条指令由11条微指令组成,其中有一条取指令的微指令是所有指令公共的,该机共有微命令31个,微指令的微操作码采用直接控制法。

试问:

1)该机微指令长度为多少

2)控制存储器的容量应为多少

解:

设微指令共有N条,N=76*11-75=761条;下址字段长为X位,2X>761,则X>10

(1)所以,该机微指令长度=31+10=41位

(2)控制存储器的容量应该》761X41位,取1024X41位。

12、某机采用微程序控制方式,其存储器容量为512X48(位),微程序在整个控制存储器

中实现转移,可控制微程序的条件共4个,判别测试字段采用编译法。

微指令采用水平型格式,后继微指令地址采用判定方式,如图所示:

微命令字段

判别测试字段

下地址字段

J操作控制T

<顺序控制>

(1)微指令中的三个字段分别应多少位

(2)画出对应这种微指令格式的微程序控制器逻辑框图。

29

解:

(1)2=4,512=2

控制字段(48-9-2=37位)

判别测试字段(2位)

下址字段(9位)

(2)

图7-20判定方式产生后继微地址的原理图

14、图7—46为某模型机的微程序流程图,图中每一个框表示一条微指令。

在点

(1)处为

指令译码后转入指令的微程序入口的多路分支点,由指令寄存器IR的I5I4两位来决定转入

哪一个入口。

在点

(2)处根据状态条件F实现条件转移,微指令中判断测试位为直接控制法。

控存容量能容纳图7—46所列出的微指令即可。

微指令的判断测试位需要几位二进制微指令的下址字段需要几位在图中标出每条微指令的微地址。

写出每条微指令的下址字段内容及判断测试字段码。

画出微地址转移逻辑电路图。

判断测试字段码=1H:

顺序执行(后继微地址=下址字段)

判断测试字段码=2H:

微程序入口散转(后继微地址=下址字段末两位ANDI5I4)

判断测试字段码=4H:

条件转移(后继微地址=下址字段第1位ANDF)

16H.

Y

(3)设3位判断测试字段

码:

微指令

判断测试字段码

下址字段内容

微指令

判断测试字段码

下址字段内容

A

1H

01H

N

1H

0CH

B

2H

10H

O

1H

15H

C

1H

02H

P

1H

16H

D

1H

06H

Q

1H

05H

E

1H

0AH

R

1H

09H

F

1H

0FH

S

1H

0DH

G

4H

18H

T

1H

0EH

H

1H

07H

U

1H

16H

I

1H

08H

V

1H

16H

J

1H

14H

W

1H

0EH

K

1H

03H

X

1H

16H

L

1H

04H

Y

1H

00H

M

1H

08H

(4)

图7-20判定方式产生后继微地址的原理图