DS1WM综合1Wire总线主控器.docx

《DS1WM综合1Wire总线主控器.docx》由会员分享,可在线阅读,更多相关《DS1WM综合1Wire总线主控器.docx(15页珍藏版)》请在冰豆网上搜索。

DS1WM综合1Wire总线主控器

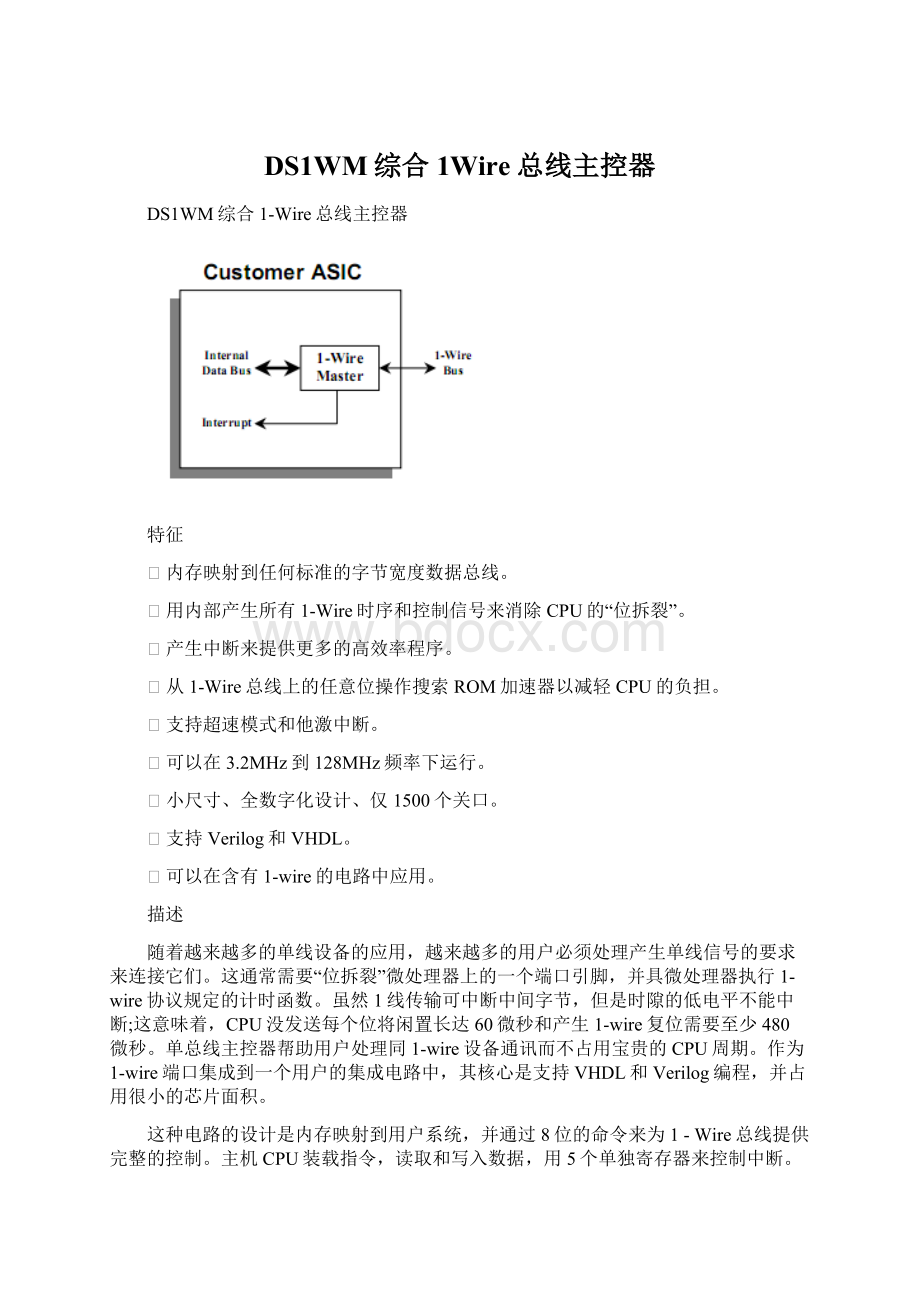

DS1WM综合1-Wire总线主控器

特征

Ø内存映射到任何标准的字节宽度数据总线。

Ø用内部产生所有1-Wire时序和控制信号来消除CPU的“位拆裂”。

Ø产生中断来提供更多的高效率程序。

Ø从1-Wire总线上的任意位操作搜索ROM加速器以减轻CPU的负担。

Ø支持超速模式和他激中断。

Ø可以在3.2MHz到128MHz频率下运行。

Ø小尺寸、全数字化设计、仅1500个关口。

Ø支持Verilog和VHDL。

Ø可以在含有1-wire的电路中应用。

描述

随着越来越多的单线设备的应用,越来越多的用户必须处理产生单线信号的要求来连接它们。

这通常需要“位拆裂”微处理器上的一个端口引脚,并具微处理器执行1-wire协议规定的计时函数。

虽然1线传输可中断中间字节,但是时隙的低电平不能中断;这意味着,CPU没发送每个位将闲置长达60微秒和产生1-wire复位需要至少480微秒。

单总线主控器帮助用户处理同1-wire设备通讯而不占用宝贵的CPU周期。

作为1-wire端口集成到一个用户的集成电路中,其核心是支持VHDL和Verilog编程,并占用很小的芯片面积。

这种电路的设计是内存映射到用户系统,并通过8位的命令来为1-Wire总线提供完整的控制。

主机CPU装载指令,读取和写入数据,用5个单独寄存器来控制中断。

所有的定时和控制信号是由1-Wire总线内部产生的。

主机仅仅需要装载指令或数据,然后就可以处理自己的工作。

当总线产生一个响应要CPU接受请求,1-wire主控器就置一个状态位,如果允许,则产生一个中断给CPU。

除了读写简化,1-wire主控器还提供了搜索ROM加速器功能,使CPU在执行1-Wire总线上任何单位操作时减轻负荷。

1-wire操作在BookofiButtonStandards[1]一书中详细介绍;因此,单总线操作细节在本文中就不再讲述。

每一个从设备,一般都有自己的一套指令,详细介绍了该装置的数据表。

用户是指那些文件详细的具体奴隶的实现。

结构图

端口说明

以下介绍所有单元I/O引脚的功能。

在下面的介绍中,0代表逻辑低电平,1代表逻辑高电平。

A0,A1,A2寄存器选择

地址信号连接到这三个寄存器的输入端口,为CPU选择一个寄存器在数据传输过程中读取或写入。

寄存器和地址表如下所示:

。

ADS,地址选通:

有效的地址选通信号的上升沿把寄存器选择(A0A1A2)锁存到内部锁存器中。

提供调整和保持定时器可视化,ads可以固定低电平使锁存器可用。

CLK,时钟输入:

这是一个(最好)的50%占空比的时钟,频率可以从3.2MHz到128MHz。

这个时钟为1-wire总线提供定时。

D7-D0,数据总线:

这个总线包含8个输入/输出线。

总线在1-wire主控器和CPU间支持双向通讯,数据、控制字,和状态信息通过D7-D0数据总线传递。

DQ,1-wire数据线:

这漏极开路线是1-wire双向数据总线。

1线外设连接到这个引脚。

此引脚必须接一上拉电阻,一般是5KΩ。

EN:

使能,当EN是低电平,1-wire主控器启用;这个信号作为设备芯片使能。

这使得1-wire和CPU之间能够通讯。

INTR,中断:

在任何时候任意一个中断类型在高电平激活状态或使能寄存器启用中断时这条线就有效。

当中断寄存器读时INTR信号复位

MR,主复位:

当这个引脚输入高电平时,它就清楚所有寄存器和1-wire主控器的控制逻辑。

并且置INTR为默认的关闭状态,高电平。

RD,读:

这个引脚使总线在一个读周期中。

当电路被激活,在RD为低电平时CPU能够从选定的寄存器读状态信息或数据。

RD和WR不能同时为低电平,如果同时低电平则WR具有优先权。

WR,写:

此引脚使总线在一个写周期。

当WR为低电平而电路已启用,CPU可以写入控制字或数据到选定的寄存器。

RD和WR绝不能同时为低电平,如果同时点电平则WR具有优先权。

运行-时钟因子

所有的1-wire定时模式是用一个频率为1MHZ的基准时钟生成。

1线主控器将在内部生成这个频率以供外部CLK引脚使用。

外部时钟必须有一个从3.2MHZ到128MHZ的频率和一个首先50%的占空比。

时钟因子寄存器控制内部的时钟分频器,并提供所需的参考频率。

这样做分两个阶段:

首先是预分频器分被1,3,5,或7除,那么剩下的电路被2,4,8,16,32,64,或128除。

时钟因子在1-Wire总线通讯发生之前必须配置。

如果主控器复位发生,。

这个寄存器设置为0x00h。

使用下面的表格,以找到基于CLK基准频率的寄存器特征值。

例如,当在15MHz的输入时钟条件下用户可以写入0x10h到这个位置,输入时钟速度的时钟因子寄存器设置

运行-传输/接收数据

数据发送和接收从1线主控器到发射/接收缓冲区。

1–wire实际上是有两个独立的传送和接收缓冲区。

写位置时传送缓冲器和数据总线连接。

读时接收缓冲器和数据总线连接。

传输缓冲区(写)/接收缓冲区(读)

写一字节

在1总线上发送一个字节,用户要在传送缓冲器中写入要发送的数据。

然后这些数据被传送到发送移位寄存器,首先它们在总线LSB上被转换成连续的数据这时数据的新字节被写入传送缓冲器,只要传送转换寄存器为空时,数据将从传送寄存器被传送,列队重复。

每个寄存器有一个标志,可以用作中断源。

当传送寄存器为空或准备接受一个新字节时传送寄存器空标志(TBE)置位。

只要一个字节写入传送缓冲器,TBE就清空。

当转换寄存器里面没有数据,或者准备接受一个新字节时,转换寄存器空标志置位。

只要有一个字节的数据从传送寄存器传送,TETM清空,TBE置位。

注意1-wire协议要求在总线通讯前要置位。

读一字节

从子设备读数据,设备必须依靠CPU中准备接收命令来准备传送数据。

数据从总线上检索和写操作方式相同。

主机通过写入传送缓冲器来加入一个读操作。

数据被转换后放入接收移位寄存器中,写好的数据和子设备中的数据线与。

因此,为了从子设备读一个字节主机必须写0xFFh,当接收移位寄存器装满要转换到接收缓冲器的数据,它就会被主机存取。

另外的字节通过重新发送0xFFh被读取。

如果自设备没有准备好传送,数据就像被传送那样被接收。

接收缓冲寄存器也能产生中断。

当数据从接收移位寄存器传送或当主机读寄存器清空时接收缓冲器标志(RBF)置位。

如果RBF置位,1-wire总线不产生传送,否则数据就会丢失,接收缓冲器中的字节将被下一个接收字节重写。

理解字节允许操作详细的时序图。

命令操作下在总线上产生一个1-wire复位。

中断标志在中断操作中将深入讲解。

写和读操作在时序图中详细讲述。

运行-指令

指令寄存器通过总线得到DS1WM的运行方式和处理特殊传送任务。

S1WM可以通过这个寄存器选择超速模式,搜索ROM加速器模式,或者标准模式。

这个寄存器还可以控制总线复位,1-Wire主控器复位和总线的直接读、写。

命令寄存器(读/写)

OD:

超速位。

这个位选择1总线上的通讯速率。

如果总线上所有的子设备支持超速模式,把这位置1将允许高速通讯。

如果是在标准1-wire通讯下这位必须置0。

RST:

软件复位。

设置这位将立即停止任何通讯和复位所有内部状态机控制通讯。

这条指令不能复位寄存器中的数据。

所有寄存器数据将被保持,否则中断寄存器就改变成1-wire主控器的新状态。

在正常操作下这位必须置0。

DQO:

DQ输出。

如果需要,这位可以用来绕开1-wire主控器操作和直接驱动总线。

把这位置高电平可以驱动总线为低电平知道它被清空或1-wire主控器复位。

当1-wire总线保持低电平时1-wire主控器的其他操作将不起作用。

通过控制时间长短,当这条线被抽样检测时这位置位和可寻址。

理解DQ1如下,主控制器产生任何1-wire通讯。

为了预防总线上突发的写操作,在DQO位起作用前中断允许寄存器中的DQOE位必须置1。

当上电或主控器复位时这一位被置0。

DQI:

DQ输入。

这一位是只读的,反映1-wire总线的现时状态。

当直接控制总线时它必须和DQO位一起使用。

这位的状态不影响1-wire主控器的其他操作。

DQOE状态不受这一位的影响。

1WR:

1-wire复位。

如果这一位置位,1-wire将复位。

设置这位自动清空SRA位。

只要1-wire复位完成1WR位将被自动清空。

当复位完成,并且查明时间已过,1-wire主控器将置当前的中断标志。

当前检测的结果将被放入中断寄存器的PDR位。

如果当前检测脉冲被接受,PDR就被清空,否则它将被置位。

SRA:

搜索ROM加速器。

当这位被置位,1-wire主控器将切换到搜索ROM加速器模式。

这个模式意味着搜索ROM指令(oxfoh)已经被分配到1-wire总线,然后复位。

1-wire系统搜索ROM的细节实际上是怎么做的,请看[1]。

简单的说明,运算法则规定总线主控器读两位(一个位和一个补充位)。

然后写一位,规定为了工作持续哪个设备应该在总线上保持。

在1-wire主控器运行搜索ROM模式后,CPU必须发送一个16字节来结束1-wire总线上的单个搜索ROM操作。

这些字节有如下构成:

第一个字节

第16 字节

在这个方案中,位标(值从0到63,“n”)标明了1-wire设备ROM中一个位的位置。

字符的“X”标志位作为填充物,并不需要一个特定的值(不必考虑位),在执行ROM搜索时如果产生冲突字符“R”指定一个选定的位写入那个特定的位。

1-wire主控器将在1-wire上为每个位的位置(从0到63)产生三个时隙。

Thesearereferencedas:

参考如下:

b0第一时隙(读数据)

b1第二时隙(读数据)

b2第三时隙(写数据)

1-wire主控器限定了时隙的类型,b2(写1或写0)如下:

如果冲突b2=m(主机选择),

如果没冲突b2=b0(没有对象选择),

如果错误b2=1(不响应)

字节的响应,将在数据寄存器为CPU读取一个完整的过程中,通过

搜索光盘功能使用搜索加速器包括16字节如下:

字节的响应,将在数据登记的CPU读取一个完整的过程中,通过

搜索光盘功能使用搜索加速器包括16字节如下:

第一个字节

第16字节

像前面那样,位标标明了1-wire设备ROM中一个位的位置。

字符“d”表示一个不符的标志在一个特定的位置上。

如果在特定位的位置有冲突或者不响应不符标志将是1否则是0。

字符“r”表示在特定位的位置实际选择方式。

选择的方式是和ROMID特定位上b2相同。

执行一个搜索次序一开始要把所有的“r”置0.如果出现错误,所有后面的响应“R”位为1,直到搜索加速器被指令寄存器写0到为1的位而停止。

这样,如果R63和D63都为1,在搜索程序和DS1WM的15个中的8个要重复时会出现一个错误。

否则Rn(n=0…63)要为可被寻址设备的ROM指令。

当搜索ROM进程完成后,为了把1-wire主控器从搜索ROM加速器模式释放出来,SRA位应该清空。

为了下个搜索ROM次序重新使用,必须把前面的设置Rn(n=0…63)用“M”设置Rm到1。

作为最高误差标志指数,为1和设置所有Ri为0(i>m)。

这个进程重复直到最高误差出现在两个连续衰减的相同位

例子----加速ROM搜索

在这个例子中,主机将用1-wire主控器识别1-wire总线上四个不同的设备设备上ROM数据如下所示(LSB优先)

ROM1=00110101…

ROM2=10101010…

ROM3=11110101…

ROM4=00010001…

1)主机通过向指令寄存器写0x01h发出一个复位脉冲。

所有子设备查到后同时响应。

2)主机通过向传送缓冲器写0xF0h发出一个搜索ROMa指令。

3)ThehostplacestheMasterinAcceleratormodebywritingtotheCommandRegister.主机通过向指令寄存器写0x02把1-Wire主控器置加速器模式。

4)机向传送缓冲器写0x00h和从接收缓冲器读返回数据。

这个过程在16位中重复。

读数据将包含R位置的ROM4,误差位置d0和d2如下(R位置被强调,最重要误差明显):

接收的数据1=1000100100000001….

5)主机这时去交错这些数据到代码为00010001的ROM,还有d2位置最后的误差位。

6)主机通过往指令寄存器中写0x00h来退出搜索加速器模式。

这时主机就可以发送指令或者从设备中直接读取数据。

7)重复1-6步来寻址下一个设备。

这时16位的数据被同时传送到ROM4,直到最后的误差位(这种情况下是d2)显示为0。

误差位倒置的,后接所有数据。

被接收的数据包含R位置的ROM1,d0位和d2位将被重新置位:

发送的数据2=0000010000000000…

接收的数据2=1000110100010001…

8)最重要的误差(d2)没改变后,次重要的(d0)会被使用和重复进程。

更多的控制数据如下:

TRANSMITTEDDATA3=0100000000000000…

RECEIVEDDATA3=1110010001000100…

TRANSMITTEDDATA4=0101000000000000…

RECEIVEDDATA4=1111010100010001…

9)在这一条,最重要的误差(d1)没有变化,所以次重要的(d0)会被使用。

然而,d0这时被第二次使用,因为没有其他重要的误差了,四个设备的搜索完成。

操作---标志和中断

传送,接收和1-Wire复位操作产生的中断被放到中断寄存器中。

当中断寄存器读操作时只有当前响应的标志(PD)被清空,当从传送和接收缓冲器中写入或读取数据时其他标志被自动清空。

如果中断允许寄存器中使能位一致,标志会在中断引脚产生一个中断。

读取中断寄存器一直设置INTR引脚为不活动状态即使所有的标志都被清空。

PD:

存在检测。

在发出1-wire复位之后,适当时间的存在检测脉冲被检测到之后,这个标志被置位。

这一位系统设定状态为0.当中断寄存器读操作时这一位被清空。

PDR:

存在检测结果。

当一个存在检测被检测,这一位将反映存在检测读的结果。

如果一个子设备被发现这一位被置0,没有设备时为1。

这一位系统默认为1。

TBE:

传送缓冲器空。

当向传送缓冲器写数据或向传送移位寄存器传数据时这个标志就会被清空。

系统默认这一位是1。

TEMT:

传送移位寄存器空。

当数据从传送寄存器被移位到传送移位寄存器时这一位被清空,在1-wire上最后一位被传送后这一位置位。

这一位系统默认为1。

RBF:

接收缓冲器满。

当接收缓冲器中有数据等待被读时这位被置位。

当数据从接收缓冲寄存器被读时这个标志被清空。

这一位系统默认为0。

SINT:

辅助中断。

当1-wire总线被子设备保持低电平远大于960us时这个标志为被置位。

当寄存器读操作时这一位被清空。

这一位系统默认为0。

NBSY:

不忙。

这一位系统默认为1时表明当前内部没有操作占用1-wire主控器。

无论任何时候读、写、复位和中断发生时这一位被清空。

当操作结束这一标志回到1状态。

DQI:

DQ输入。

这一位是指令寄存器第三位的映像。

这要求主机和总线所有状态视中断寄存器为只读。

这一位在中断允许寄存器中没有对应的使能位。

中断允许寄存器允许系统程序指定中断源,那种情况下INTR引脚起作用和确定INTR引脚活动状态。

当一个主机复位被接受,这个寄存器中的所有位被清空为0,禁止所有中断源和置INTR引脚的活动状态为低电平。

这意味着当所有中断被屏蔽时INTR引脚电位将被拉高。

读中断寄存器时INTR引脚复位成待用状态。

EPD:

现场检测使能。

如果这一位是1.并且现场检测标志置位。

那么,无论什么时候发出1-wire复位信号和发出合适的现场检测脉冲,INTR引脚都将变为有效状态。

IAS:

INTR活动状态。

这一位测定INTR引脚的活动状态。

如果这一位是1.INTR引脚高电平起作用。

如果是0,INTR引脚低电平起作用。

EBTE:

传送缓冲器空中断使能。

如果这一位是1.并且传送缓冲器空标志置位。

那么INTR引脚将起作用。

ETMT:

传送移位寄存器空中断使能。

如果这一位是1传送一位寄存器空标志置位。

INTR引脚就会变为有效状态。

ERBF:

接收缓冲器满中断使能。

如果这一位是1,接收缓冲器满标志置位,那么INTR引脚就有效。

ESINT:

辅助中断使能。

如果这一位是1辅助中断标志置位,INTR引脚就会有效。

ENBSY:

不忙中断使能。

如果这位是1,不忙标志置位,INTR引脚就会有效。

DQOE:

DQ输出使能。

这一位作为DQ总线的控制选择位。

当置0(默认)时,总线被1-Wire主控器正常控制。

当置1时,指令寄存器的DQ0位直接控制总线的状态。

系统上电或复位后这一位被默认为0,除非用户要通过DQ0位手动控制总线,否则这一位应该一直为0。

I/0信号传输

1-wire要求精确的信号传输协议以保证数据的完整传输。

1wire初始化系列用到4个协议。

(复位脉冲接着是现场脉冲),写0写1和读数据。

主机接收所有类型的信号传输除了现场脉冲。

初始化序列要求开始所有通讯,总线受控情况如图1所示。

现场脉冲接着复位脉冲表明子设备准备接受ROM指令。

1-wire主控器给tRSTL发出一个复位脉冲。

1-Wire总线被上拉电阻拉到高电平。

检测DQ引脚的上升沿之后,子设备等待tPDH,然后给tPDL传送现场脉冲。

自设备起作用后主机在tPDS抽样检测总线来检测一个有效的现场脉冲。

抽样的结果存在中断寄存器的PDR位。

主控器释放总线后复位时隙结束tRSTH

写时隙

当1-wire主控器把1-wire总线并从逻辑高电平拉到逻辑低电平时写时隙启动。

主机通过在tLOW1时刻释放线路同时允许线路拉到逻辑低电平产生一个写1时隙。

线路保持在tLOW0发出一个写0时隙。

一个子设备将在线路降落后15µs和60_s(超速模式2µs到6µs)之间抽样检测1-wire总线。

如果抽样检测到线路高电平,就产出一个写1.如果抽样检测低就产生一个0(看图2)。

读时隙

当1-wire在至少1µs把总线拉到低电平时读时启动一个读时隙,然后释放读时隙。

如果子设备正在响应0,它将继续保持线路低电平长达60µs(在超速模式下是6µs),否则它将立即释放响应。

主机在读时隙开始就抽样检测tRDV数据。

主机在tSLOT时刻后结束读时隙。

详细内容看图2。

图21-Wire读/写时隙

写循环

读循环

产生1-Wire复位

注意:

1)这些值将取决于用在现实电路的进程。

这些值仅作为例子。

2)复位后1-wire主控器将等待一个在DQ线路上的下降沿脉冲以被检测到,时长60µs或者超速模式下6µss。

3)如果ADS被约束在低电平,tAR和tAW被视为由tES而来;总之,在EN变为低电平后至少tES+tAR或者tES+tAW时刻

或者WR必须发生。

4)定时器视1-wire子设备而定。