数字逻辑设计及应用复习题.docx

《数字逻辑设计及应用复习题.docx》由会员分享,可在线阅读,更多相关《数字逻辑设计及应用复习题.docx(12页珍藏版)》请在冰豆网上搜索。

数字逻辑设计及应用复习题

一、填空题(每空1分,共20分)

1、请完成如下的进制转换:

22.7510=10110.112=26.68=16.C16;

2、F6.A16=246.62510=001001000110.0110001001018421BCD=010101111001.100101011000余3码

3、-9910的8位(包括符号位)二进制原码是11100011,8位二进制反码是10011100,8位二进制补码是10011101;

4、请问逻辑F=A/B+(CD)/+BE/的反函数F/=

;

解:

5、F(A,B,C)=Σm(2,4,6)=ПM(0,1,3,4,7);

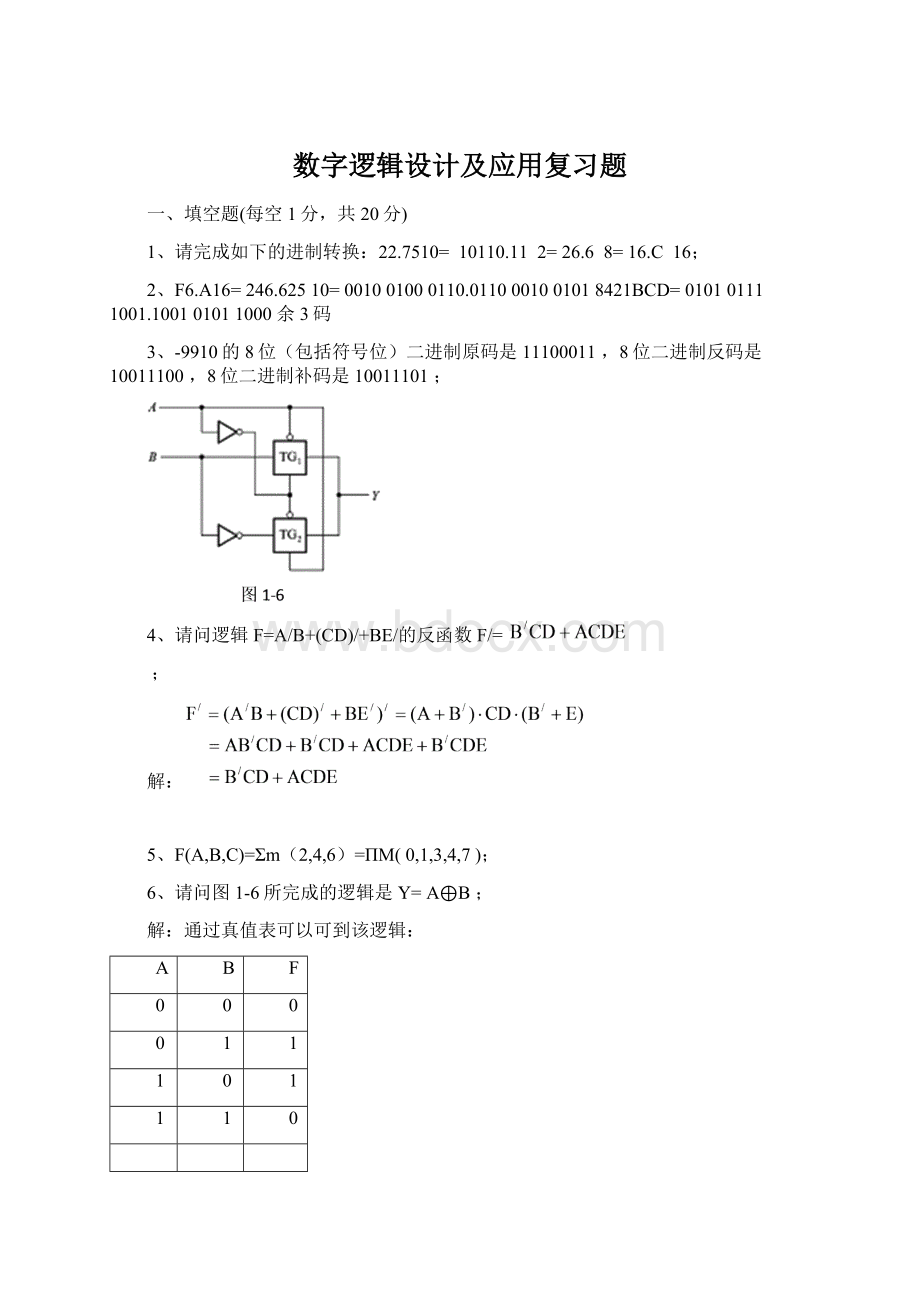

6、请问图1-6所完成的逻辑是Y=A⊕B;

解:

通过真值表可以可到该逻辑:

A

B

F

0

0

0

0

1

1

1

0

1

1

1

0

7、74148器件是一个3-8编码器,它采用的编码方式是优先编码或数大优先编码;

8、74283器件是一个4位全加器,它的内部逻辑电路与串行加法器不同,采用的是超前进位或先行进位方法来实现全加逻辑。

9、如果一个与或逻辑电路的函数式为:

,该逻辑存在静态冒险,现通过添加冗余项的方式来消除该冒险,则该冗余项为(A/+C);

10、请写出JK触发器的特性方程:

=JQ/+K/Q;

11、请写出T触发器的特性方程:

=T⊕Q或者TQ/+T/Q;

12、请写出D触发器的特性方程:

=D;

13、请写出SR触发器的特性方程:

=S+R/Q;

14、如果某组合逻辑的输入信号的个数为55个,则需要6位的输入编码来实现该逻辑。

解:

采用的公式应该是log255,向上取整

二、选择题(每题1分,共10分)

1、下面有关带符号的二进制运算,描述正确的是,其中X是被加数,Y是加数,S为和:

①.[X]原码+[Y]原码=[S]原码②.[X]补码+[Y]补码=[S]补码

③.[X]反码+[Y]反码=[S]反码④.[X]原码+[Y]原码=[S]补码

2、逻辑函数式AC+ABCD+ACD/+A/C=

①.AC②.C③.A④.ABCD

3、请问F=A⊕B的对偶式

①.A+B②.A⊙B③.AB④.AB/+A/B

4、已知门电路的电平参数如下:

请问其高电平的噪声容限为:

①.2.2V②.1.2V③.0.7V④.0.3V

5、下面描述方法,对于一个组合逻辑而言,具备唯一性的是:

①.逻辑函数式②.真值表

③.卡诺图④.逻辑电路图

6、下面电路中,属于时序逻辑电路的是:

①.移位寄存器②.多人表决电路

③.比较器④.码制变换器

7、一个D触发器的驱动方程为

,则其逻辑功能与以下哪种触发器相同:

①.JK触发器②.SR触发器

③.D触发器④.T触发器

8、n位环形计数器,其计数循环圈中的状态个(模)数为:

①.n个②.2n个

③.2n个④.2n-1个

9、n位扭环计数器,其计数循环圈中的状态个(模)数为:

①.n个②.2n个

③.2n个④.2n-1个

10、用555时基电路外接定时阻容元件构成单稳态触发器,当增大阻容元件的数值时,将使:

①.输出脉冲的幅度增加

②.输出脉冲宽度增加

③.输出脉冲重复频率提高

④.以上说法都不对

三、判断题(每题1分,共10分)

1、CMOS集成逻辑OD门,可以用以线与操作;(√)

2、三态门的附加控制端输入无效时,其输出也无效;(Х)

3、三态门的三个状态分别为高电平、低电平和高阻态;(√)

4、施密特触发输入的门电路,当输入从高电平变换到低电平,和从低电平变换到高电平,它的输出变化轨迹相同;(Х)

5、组合逻辑和时序逻辑的区别主要在于前者与时间无关,而后者时间的因素必须考虑进去;(√)

6、一个逻辑的函数式并不唯一,但是最简的与或表达式是唯一的;(Х)

7、模拟信号是连续的,而数字信号是离散的;(√)

8、当两个组合逻辑的真值表相同是,则表明这两个逻辑是相等的;(√)

9、对于一个优先编码器而言,当输入多个有效时,其输出很难讨论;(Х)

10、串行加法器比超前进位加法器速度更快,且电路更为简单;(Х)

四、卡诺图化简(8分)

请将逻辑F(A,B,C,D)=m(0,2,3,5,7,8,10,11,13)化成最简与或式;

或者

五、组合逻辑分析,要求如下:

(8分)

该逻辑电路图如图5所示,具体要求如下:

1、

写出逻辑S和CO的逻辑函数式

2、画出将该逻辑的真值表

3、真值表

A

B

CI

S

CO

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

六、时序逻辑分析,要求如下:

(14分)

逻辑电路图如图6所示,请完成:

1、写出驱动方程、状态方程;

2、画出状态转换图或者状态转换表。

解答:

3.状态表

或者状态图:

以上图表任画一个即得分。

七、组合逻辑设计,要求如下:

(8分)

利用一块74138芯片和一定的门电路实现如下逻辑:

其中74138为3-8二进制译码器

解题步骤:

八、时序逻辑设计,要求如下:

(10分)

利用74163和一定的门电路实现如下的七进制计数器。

74163为4位的同步二进制加计数器。

第一种方法:

在状态0111时,重置状态到0001或1001;电路图如下:

第二种方法:

在状态1111,通过行波输出重置状态到1001;电路图如右:

两种方法皆可

九、时序逻辑设计,要求如下:

(10分)

用mealy型时序逻辑电路设计一个101串行数据检测的时序状态机。

要求画出化简后的状态转换图。

一、选择题(请在答题纸上做答,每题2分,共20分)

1、十进制数128的8421BCD码是( B)。

A.10000000 B.000100101000 C.100000000 D.100101000

2、若输入变量A、B全为1时,输出F=1,则其输入与输出的关系是(B)。

A.异或B.同或C.或非D.与或

3、逻辑代数中的三种基本运算是(A)

A.与、或、非B.与非、或非、与或非

C.异或、同或、非D.加、减、乘

4、关于最小项,任意两个最小项的乘积为(A)

A.0B.1C.与变量输入值有关系D.无法确定

5、逻辑表达式A+BC=(C)。

A.A+BB.A+CC.(A+B)(A+C)D.B+C

6、函数F(A,B,C)=AB+BC+AC的最小项表达式为(B)。

A.F(A,B,C)=∑m(0,2,4)B.(A,B,C)=∑m(3,5,6,7)

C.F(A,B,C)=∑m(0,2,3,4)D.F(A,B,C)=∑m(2,4,6,7)

7、在下列逻辑电路中,不是组合逻辑电路的是(D)。

A.译码器B.编码器C.全加器D.寄存器

8、下列触发器中,抗干扰能力最强的是(D)

A.RS电平触发器B.主从RS触发器C.主从JK触发器D.边沿JK触发器

9、要使JK触发器的输出Q从1变成0,它的输入信号JK应为(B)。

A.00B.01C.10D.无法确定

10、关于组合逻辑电路与时序逻辑电路,下列表述错误的是(A)

A.组合逻辑电路有可能含有存储电路

B.时序逻辑电路含有组合逻辑电路

C.组合逻辑电路输出状态仅仅由当前输入状态有关系

D.时序逻辑电路输出的状态与过去的状态也有关系

二、填空题(请在答题纸上做答,每题2分,共20分)

1、将逻辑函数

转化为“与非—与非”形式:

____________。

2、将(25.75)10转化为二进制_____________;转化为16进制为:

_____________;用8421BCD码表示为:

_____________。

3、D触发器的特征方程为,JK触发器的特征方程为,T触发器的特征方程为。

4、把JK触发器改成T触发器的方法是__把J和K连接一起接为T___________

5、同步触发器在一个CP脉冲高电平期间发生多次翻转,称为空翻现象。

6、用n个触发器构成计数器,可得到最大计数长度是___2的n次方_________。

三、综合题(请在答题纸上做答,5小题,共60分)

1、将下面的表达式化简成最简与或式:

(10分)

2、用译码器74HC138和适当的逻辑门电路实现函数:

(10分)

注:

图174HC138芯片示意

表174HC138逻辑功能表

3、分析如图(a)所示时序电路,设电路的初始状态为0。

(1)画出其状态表和状态图(10分)

(2)画出在时钟脉冲作用下(见图(b)),Q和Z的波形图。

(5分)

4、用74160设计一个7进制计数器,其计数状态为自然二进制数1001~1111。

74160芯片示意图以及功能表如下图所示。

(10分)

注:

“L”表示低电平“0”;“H”表示高电平“1”;“x”表示“不关心”

5、试用上升沿触发的D触发器设计一个1111序列检测器,它有一个输入端A和一个输出端Y。

从A端输入串行的数据,如果连续输入四个“1”,则输出端Y输出高电平“1”,否则输出低电平“0”。

(15分)