FPGA实训作业程序实训报告.docx

《FPGA实训作业程序实训报告.docx》由会员分享,可在线阅读,更多相关《FPGA实训作业程序实训报告.docx(15页珍藏版)》请在冰豆网上搜索。

FPGA实训作业程序实训报告

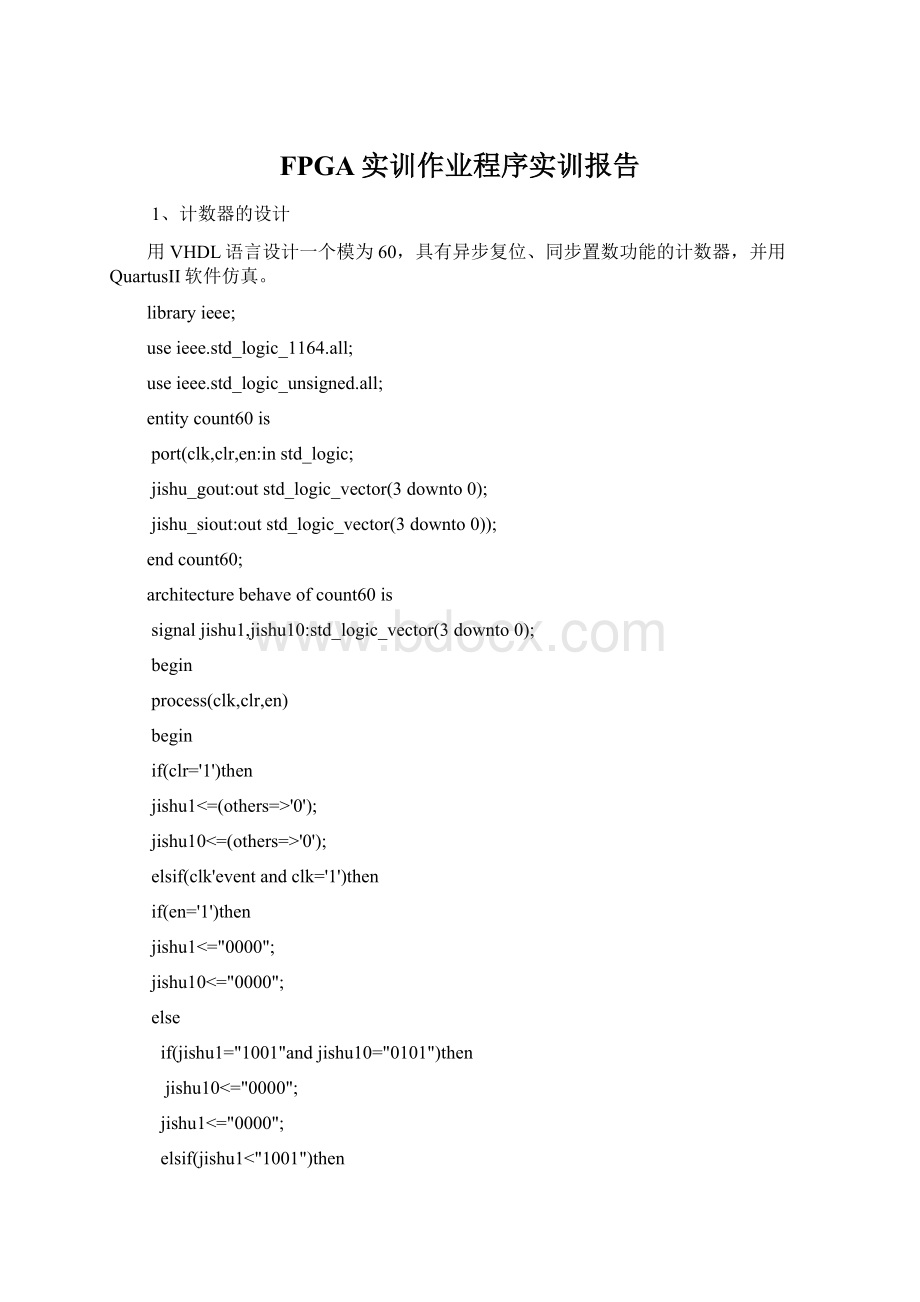

1、计数器的设计

用VHDL语言设计一个模为60,具有异步复位、同步置数功能的计数器,并用QuartusII软件仿真。

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitycount60is

port(clk,clr,en:

instd_logic;

jishu_gout:

outstd_logic_vector(3downto0);

jishu_siout:

outstd_logic_vector(3downto0));

endcount60;

architecturebehaveofcount60is

signaljishu1,jishu10:

std_logic_vector(3downto0);

begin

process(clk,clr,en)

begin

if(clr='1')then

jishu1<=(others=>'0');

jishu10<=(others=>'0');

elsif(clk'eventandclk='1')then

if(en='1')then

jishu1<="0000";

jishu10<="0000";

else

if(jishu1="1001"andjishu10="0101")then

jishu10<="0000";

jishu1<="0000";

elsif(jishu1<"1001")then

jishu1<=jishu1+1;

else

jishu1<="0000";

if(jishu10<"0101")then

jishu10<=jishu10+1;

else

jishu10<="0000";

endif;

endif;

endif;

endif;

jishu_gout<=jishu1;

jishu_siout<=jishu10;

endprocess;

endbehave;

60计数器的仿真结果:

2、分频器的设计:

用VHDL语言设计一个通用的可输出输入信号的2分频信号、4分频信号、8分频信号、16分频信号的分频电路,并用QuartusII软件仿真。

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityfenpinis

port(clk_in:

instd_logic;

clk2,clk4,clk8,clk16:

outstd_logic);

endfenpin;

architecturebehaveoffenpinis

signalq:

std_logic_vector(3downto0);

begin

process(clk_in)

begin

if(clk_in'eventandclk_in='1')then

q<=q+1;

endif;

endprocess;

clk2<=q(0);

clk4<=q

(1);

clk8<=q

(2);

clk16<=q(3);

end;

分频器的仿真结果:

3、编码器的设计:

用VHDL语言设计一个8-3编码器的VHDL程序,并用QuartusII软件仿真。

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitycode83is

port(din:

instd_logic_vector(7downto0);

code:

outstd_logic_vector(2downto0));

endcode83;

architecturebehaveofcode83is

begin

process(din)

begin

if(din(7)='0')thencode<="000";

elsif(din(6)='0')thencode<="001";

elsif(din(5)='0')thencode<="010";

elsif(din(4)='0')thencode<="011";

elsif(din(3)='0')thencode<="100";

elsif(din

(2)='0')thencode<="101";

elsif(din

(1)='0')thencode<="110";

elsif(din(0)='0')thencode<="111";

endif;

endprocess;

end;

编码器的仿真结果:

4、移位寄存器的设计:

用VHDL语言设计一个8位的移位寄存器,使其具有左移一位或右移一位,并行输入和同步复位的功能,并用QuartusII软件仿真。

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityyuweiis

port(clk,rst,shift_left,shift_right:

instd_logic;

data:

instd_logic_vector(7downto0);

code:

instd_logic_vector(1downto0);

q:

outstd_logic_vector(7downto0));

endyuwei;

architecturebehaveofyuweiis

begin

process(clk,rst)

begin

ifrising_edge(clk)then

if(rst='1')then

q<="00000000";

else

casecodeis

when"01"=>q<=data(6downto0)&shift_left;---zouyi

when"10"=>q<=data(7downto1)&shift_right;---youyi

when"11"=>q<=data;

whenothers=>null;

endcase;

endif;

endif;

endprocess;

end;

移位寄存器的仿真结果:

5、智力抢答器的设计:

用VHDL语言设计一款可容纳四组参赛者的数字智力抢答器,要求如下:

(1)每组设置一个抢答按钮供抢答者使用。

(2)电路具有第一抢答信号的鉴别和锁存功能。

在主持人将系统复位并发出抢答指令后,若参加者按抢答开关,则该组指示灯亮并用组别显示电路显示抢答者的组别,同时扬声器发出“嘟嘟”的双音音响,且持续2~3秒。

此时,电路应具备自锁功能,使别组的抢答开关不起作用。

(3)设置计分电路。

每组在开始时预置成100分,抢答后由主持人计分,答对一次加10分,否则减10分。

(4)设置犯规电路。

对提前抢答和超时抢答的组别鸣喇叭示警,并由组别显示电路显示出犯规组别。

(5)用QuartusII软件仿真,并下载到实验箱上硬件仿真。

(1)抢答器:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityqiangdais

port(rst,clk,a,b,c,d:

instd_logic;

tmp:

outstd_logic;

states:

bufferstd_logic_vector(3downto0));

endqiangda;

architectureoneofqiangdais

signalstat:

std_logic_vector(3downto0);

begin

p1:

process(a,b,c,d,rst,clk)

begin

if(rst='1')then

stat<="0000";

tmp<='0';

elsif(clk'eventandclk='1')then

if((a='1'orstat(0)='1')andnot(stat

(1)='1'orstat

(2)='1'orstat(3)='1'))then

stat(0)<='1';

endif;

if((b='1'orstat

(1)='1')andnot(stat(0)='1'orstat

(2)='1'orstat(3)='1'))then

stat

(1)<='1';

endif;

if((c='1'orstat

(2)='1')andnot(stat(0)='1'orstat

(1)='1'orstat(3)='1'))then

stat

(2)<='1';

endif;

if((d='1'orstat(3)='1')andnot(stat(0)='1'orstat

(1)='1'orstat

(2)='1'))then

stat(3)<='1';

endif;

tmp<=(aorborcord);

endif;

endprocessp1;

p2:

process(states(0),states

(1),states

(2),states(3))

begin

if(stat="0000")thenstates<="0000";

elsif(stat="0001")thenstates<="0001";

elsif(stat="0010")thenstates<="0010";

elsif(stat="0100")thenstates<="0011";

elsif(stat="1000")thenstates<="0100";

endif;

endprocessp2;

end;

仿真结果:

(2)显示:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitycodeis

port(ain4:

instd_logic_vector(3downto0);

codes:

outstd_logic_vector(6downto0));

endcode;

architectureoneofcodeis

--signalcodes:

std_logic_vector(6downto0);

begin

process(ain4)

begin

caseain4is

when"0001"=>codes<="0110000";--1

when"0010"=>codes<="1101101";--2

when"0011"=>codes<="1111001";--3

when"0100"=>codes<="0110011";--4

whenothers=>codes<="1111110";--0

endcase;

endprocess;

end;

仿真结果:

(3)计分器:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityjifenis

port(clk,rst1,add:

instd_logic;

chos:

instd_logic_vector(3downto0);

aa2,aa1,aa0,bb2,bb1,bb0:

outstd_logic_vector(3downto0);

cc2,cc1,cc0,dd2,dd1,dd0:

outstd_logic_vector(3downto0));

endjifen;

architectureoneofjifenis

begin

process(clk,rst1,add,chos)

variableal2:

std_logic_vector(3downto0):

="0001";

variableal1:

std_logic_vector(3downto0):

="0000";

variablebl2:

std_logic_vector(3downto0):

="0001";

variablebl1:

std_logic_vector(3downto0):

="0000";

variablecl2:

std_logic_vector(3downto0):

="0001";

variablecl1:

std_logic_vector(3downto0):

="0000";

variabledl2:

std_logic_vector(3downto0):

="0001";

variabledl1:

std_logic_vector(3downto0):

="0000";

begin

if(clk'eventandclk='1')then

if(rst1='1')then

al2:

="0001";al1:

="0000";

bl2:

="0001";bl1:

="0000";

cl2:

="0001";cl1:

="0000";

dl2:

="0001";dl1:

="0000";

elsif(chos="0001")then--a

if(add='1')then

if(al1="1001")then

al1:

="0000";

al2:

=al2+1;

if(al2="1001")then

al2:

="0000";

endif;

else

al1:

=al1+1;

endif;

endif;

elsif(chos="0010")then--b

if(add='1')then

if(bl1="1001")then

bl1:

="0000";

bl2:

=bl2+1;

if(bl2="1001")then

bl2:

="0000";

endif;

else

bl1:

=bl1+1;

endif;

endif;

elsif(chos="0011")then--c

if(add='1')then

if(cl1="1001")then

cl1:

="0000";

cl2:

=cl2+1;

if(cl2="1001")then

cl2:

="0000";

endif;

else

cl1:

=cl1+1;

endif;

endif;

elsif(chos="0100")then--d

if(add='1')then

if(cl1="1001")then

cl1:

="0000";

cl2:

=cl2+1;

if(cl2="1001")then

cl2:

="0000";

endif;

else

cl1:

=cl1+1;

endif;

endif;

endif;

endif;

aa2<=al2;aa1<=al1;aa0<="0000";

bb2<=bl2;bb1<=bl1;bb0<="0000";

cc2<=cl2;cc1<=cl1;cc0<="0000";

dd2<=dl2;dd1<=dl1;dd0<="0000";

endprocess;

end;

仿真结果:

(4)鸣响:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitymingxiangis

port(clk,ing:

instd_logic;

q:

outstd_logic);

endmingxiang;

architectureoneofmingxiangis

signalwarm:

std_logic;

signalnn:

integerrange0to10;

begin

q<=warm;

process(clk)

begin

if(clk'eventandclk='1')then

if(ing='0')then

warm<='0';

elsif(ing='1'andnn<=9)then

warm<=notwarm;

nn<=nn+1;

else

warm<='0';

endif;

endif;

endprocess;

end;

仿真结果:

(5)智力抢答器的元件例化;

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitychandaciis

port(clk,rst,rst1,a,b,c,d,add:

instd_logic;

q:

outstd_logic;

codes:

outstd_logic_vector(6downto0);

states:

outstd_logic_vector(3downto0);

aa2,aa1,aa0,bb2,bb1,bb0:

outstd_logic_vector(3downto0);

cc2,cc1,cc0,dd2,dd1,dd0:

outstd_logic_vector(3downto0));

endchandaci;

architecturebehaveofchandaciis

signaltmp1:

std_logic;

signalstat:

std_logic_vector(3downto0);

componentqiangda

port(clk,rst,a,b,c,d:

instd_logic;

tmp:

outstd_logic;

states:

outstd_logic_vector(3downto0));

endcomponent;

componentcode

port(ain4:

instd_logic_vector(3downto0);

codes:

outstd_logic_vector(6downto0));

endcomponent;

componentjifen

port(clk,add,rst1:

instd_logic;

chos:

instd_logic_vector(3downto0);

aa2,aa1,aa0,bb2,bb1,bb0:

outstd_logic_vector(3downto0);

cc2,cc1,cc0,dd2,dd1,dd0:

outstd_logic_vector(3downto0));

endcomponent;

componentmingxiang

port(clk,ing:

instd_logic;

q:

outstd_logic);

endcomponent;

begin

u0:

qiangdaportmap(clk,rst,a,b,c,d,tmp1,stat);

u1:

codeportmap(stat,codes);

u2:

jifenportmap(clk,rst1,add,stat,aa2,aa1,aa0,

bb2,bb1,bb0,cc2,cc1,cc0,dd2,dd1,dd0);

u3:

mingxiangportmap(clk,tmp1,q);

end;

仿真结果: