第一章EDA技术实验基础实验.docx

《第一章EDA技术实验基础实验.docx》由会员分享,可在线阅读,更多相关《第一章EDA技术实验基础实验.docx(9页珍藏版)》请在冰豆网上搜索。

第一章EDA技术实验基础实验

第一章技术实验基础实验

实验一用原理图输入法设计一位半加器

一、实验目的

.熟悉利用Ⅱ的原理图输入方法设计简单组合电路;

.通过一个半加器的设计把握利用软件进行电子线路设计的详细流程;

.学会对实验板上的进行编程下载,硬件验证自己的设计项目。

二、实验设备及器材配置

机一台

综合实验开发系统中:

基本核心板模块、发光管显示模块、普通键盘模块、下载器、下载线、十针连接线根。

三、实验原理

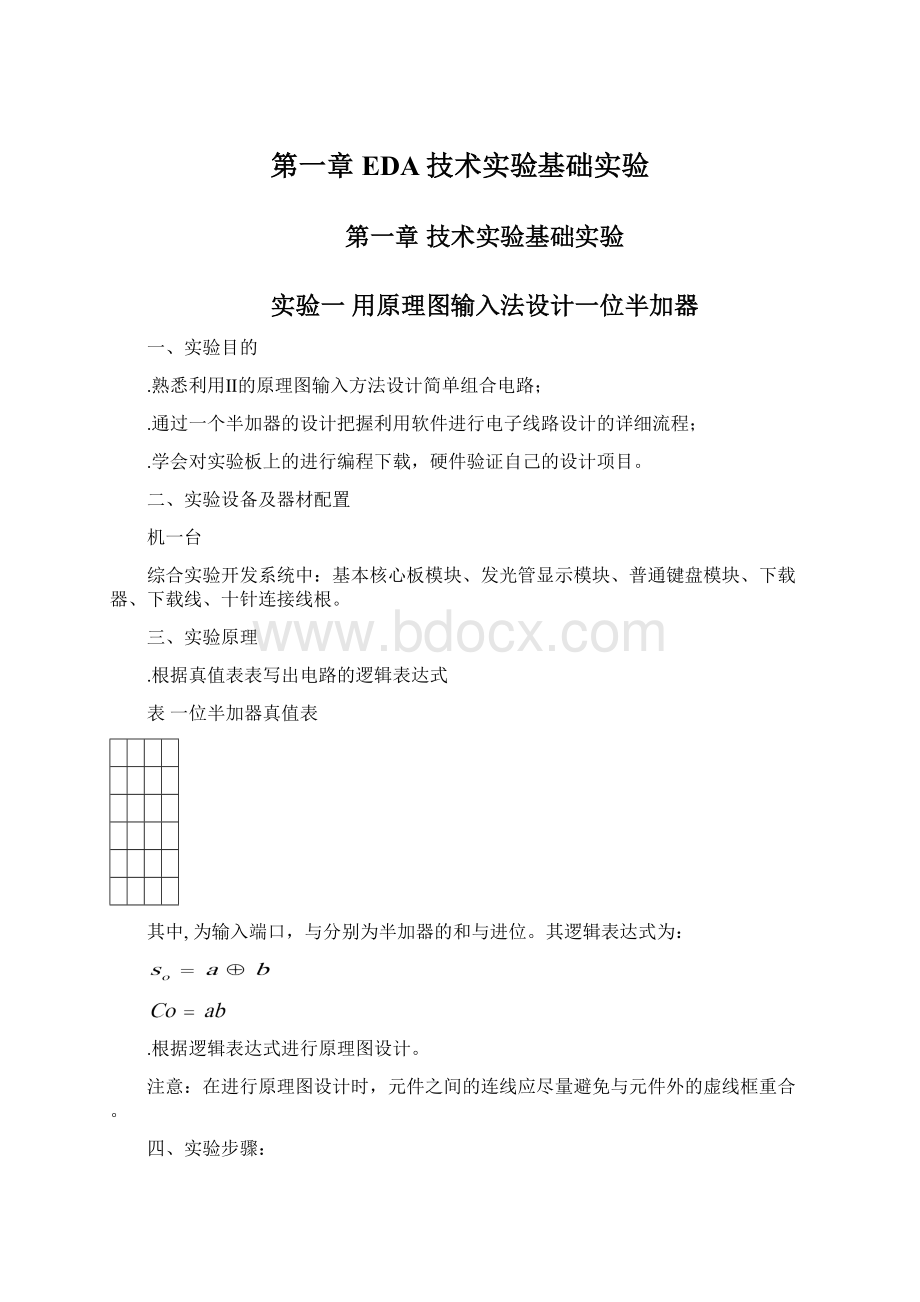

.根据真值表表写出电路的逻辑表达式

表一位半加器真值表

其中,为输入端口,与分别为半加器的和与进位。

其逻辑表达式为:

.根据逻辑表达式进行原理图设计。

注意:

在进行原理图设计时,元件之间的连线应尽量避免与元件外的虚线框重合。

四、实验步骤:

.为本项工程设计建立文件夹,注意文件夹名不能用中文,且不可带空格。

.根据半价器逻辑表达式进行原理图设计。

.对所设计的工程文件进行编译,排查错误。

.时序仿真,记录时序分析表。

.选择目标芯片。

.引脚锁定。

推荐锁定形式:

输入接口选择核心板上接口,与普通键盘模块相连,连接后,可任意选择按键所对应的引脚(例如,选择和,它们所对应的引脚编号为和;输出接口选择核心板上接口,与发光管显示模块相连,连接后,课任意选择发光二级管所对应的引脚(例如选择和,它们所对应的引脚编号为和)。

注:

输入输出接口可在核心板上十针接口中任意选择(白色接口除外),对应的引脚可在核心板上的引脚标注中查找。

.编程下载,观察硬件结果。

下载时请下载器形式请选择。

注:

如下载后硬件调试没有通过,需重新检查连接,如果修改后重新进行下载,请将下载界面中原有的*文件删除,重新加载一次,然后再下载。

.撰写实验报告册,思考如何利用半加器设计一位全加器。

五、练习题

.请用本实验所作的一位半加器设计一位全加器。

要求利用原理图输入方式。

.请利用一位全加器设计四位全加器。

要求利用原理图输入方式。

注:

本练习主要使学生牢固掌握原理图输入设计方法,同时掌握设计中有关层次的基本概念。

学会在工程中添加文件的方法。

实验二四位加法器设计

一、实验目的

.利用并行语句中的简单赋值语句,对四位加法器进行设计。

.掌握仿真分析中总线型数据的输入方法。

.掌握程序包中对于数据类型进行加法的基本原则。

为日后设计通用位加法器奠定基础。

二、实验设备及器材

.机一台

.综合实验开发系统中:

基本核心板模块、发光管显示模块、普通键盘模块、下载器、下载线、十针连接线根。

三、实验原理

.设计一个四位加法器,要求输入信号的数据类型为,位宽为(分别为,);输出信号为和,数据类型分别为及。

.利用并行语句中的简单赋值语句进行加法运算。

提示:

由于对数据类型进行“”运算,因此需要调用程序包;同时由于输入信号位宽为,进行加运算后,结果位宽会出现位,设计时要考虑如何将数据位进行扩展。

.设计中请合理定义信号及其数据类型,并注意信号定义的位置。

四、实验步骤

.为本项工程设计建立文件夹,注意文件夹名不能用中文,且不可带空格。

.根据二进制加法运算的原则,设计四位加法器。

.对所设计的工程文件进行编译,排查错误。

.选择目标芯片。

.引脚锁定。

推荐锁定形式:

输入接口选择核心板上接口,与普通键盘模块相连,连接后,可任意选择按键所对应的引脚(例如,输入信号的四位选择、、及,它们所对应的引脚编号为、、、。

输入信号的四位选择、、及,它们所对应的引脚编号为、、、;输出接口选择核心板上接口,与发光管显示模块相连,连接后,课任意选择发光二级管所对应的引脚(例如选择、、、及,它们所对应的引脚编号为、、、、)。

注:

输入输出接口可在核心板上十针接口中任意选择(白色接口除外),对应的引脚可在核心板上的引脚标注中查找。

.编程下载,观察硬件结果。

下载时请下载器形式请选择。

注:

如下载后硬件调试没有通过,需重新检查连接,如果修改后重新进行下载,请将下载界面中原有的*文件删除,重新加载一次,然后再下载。

.撰写实验报告册。

五、练习题

.设计四位减法器。

.设计四位加减法器。

(提示:

本习题可在学习完语句后进行设计,将语句与简单赋值语句进行组合后进行设计。

)

实验三七段数码显示译码器设计

一、实验目的

.学习段数码显示译码器设计。

.学习的语句应用及多层次设计方法。

二、实验设备及器材配置

机一台

.综合实验开发系统中:

基本核心板模块、普通键盘模块、七段数码管显示模块、下载器、下载线、十针连接线根。

三、实验原理及内容

.段数码显示译码器是纯组合电路,通常的小规模专用只能做十进制译码器,然而数字系统中的数据处理和运算都是二进制的,所以输出表达式都是十六进制的,为了满足十六进制数的译码显示,最方便的方法就是利用译码程序在中实现。

.设计时输入为位宽为的数据类型,输出为注意位宽为的数据类型。

这里没有考虑表示小数点的放光管,如果考虑,需要增加段,将源程序中的输入矢量七位改为八位。

.设计要求使用语句,配合语句,进行七段数码管驱动电路的设计,要求数码管显示。

图为共阴极数码管,程序中的编码顺序为(由高到低)。

图共阴极数码管及其电路

四、实验步骤

.为本项工程设计建立文件夹,注意文件夹名不能用中文,且不可带空格,文件名必须与设计实体名一致。

.按照实验原理及内容中的要求进行程序设计,在核心语句后面请进行注释。

.对所设计的工程文件进行编译,排查错误。

.选择目标芯片。

.引脚锁定。

推荐锁定形式:

输入接口选择核心板上接口,与普通键盘模块相连,连接后,可任意选择按键所对应的引脚(例如选择、、及,它们所对应的引脚编号为、、、;输出接口选择核心板上接口,与七段数码管显示模块连接后,按照顺序进行锁定(对应的引脚编号为、、、、、、)。

注:

输入输出接口可在核心板上十针接口中任意选择(白色接口除外),对应的引脚可在核心板上的引脚标注中查找。

.编程下载,观察硬件结果。

下载时请下载器形式请选择。

注:

如下载后硬件调试没有通过,需重新检查连接,如果修改后重新进行下载,请将下载界面中原有的*文件删除,重新加载一次,然后再下载。

.撰写实验报告册。

五、练习题

.利用语句对七段数码管驱动电路进行设计。

.针对七段数码管显示驱动电路不同设计方法(并行、顺序)进行比较。

实验四用文本输入法设计触发器和锁存器

一、实验目的

.熟悉Ⅱ的文本设计过程。

.学习简单时序电路的设计、仿真和硬件测试。

二、实验器材

机一台。

.综合实验开发系统中:

基本核心板模块、发光管显示模块、普通键盘模块、下载器、下载线、十针连接线根。

三、实验原理

.触发器的设计,根据触发器原理在文本编辑环境中编写源程序。

设计中,触发信号为时钟信号的上升沿或下降沿(建议设计中可以利用按键输入作为时钟信号,以便于观察)。

.锁存器的设计,根据锁存器原理在文本编辑环境中编写源程序。

设计中,触发信号为时钟信号高电平或低电平(建议设计中可以利用按键输入作为时钟信号,以便于观察)。

.比较两程序的异同,观察仿真波形文件的区别。

.在进行硬件测试时,请注意时钟信号的给定。

四、实验步骤

.为本项工程设计建立文件夹,注意文件夹名不能用中文,且不可带空格,文件名必须与设计实体名一致。

.说明源程序中各语句的含义,比较触发器与锁存器源程序的异同。

.对所设计的工程文件进行编译,排查错误。

.选择目标芯片。

.引脚锁定。

推荐锁定形式:

输入接口选择核心板上接口,与普通键盘模块相连,连接后,可任意选择按键所对应的引脚(例如选择、,它们所对应的引脚编号为、;输出接口选择核心板上接口,与发光管显示模块连接后,进行锁定(选择发光二级管,引脚编号为)。

注:

输入输出接口可在核心板上十针接口中任意选择(白色接口除外),对应的引脚可在核心板上的引脚标注中查找。

.编程下载,观察硬件结果。

下载时请下载器形式请选择。

注:

如下载后硬件调试没有通过,需重新检查连接,如果修改后重新进行下载,请将下载界面中原有的*文件删除,重新加载一次,然后再下载。

.撰写实验报告册。

五、练习题

.利用顺序语句设计触发器。

.利用顺序语句设计微分电路。

实验五含异步清和同步时钟使能的百进制加法计数器

一、实验目的

.学习计数器的设计方法,进而为设计通用计数器奠定基础。

.设计时可采用多种方法,从而达到灵活运用各类语句的目的。

二、实验器材

.机一台。

.综合实验开发系统中:

基本核心板模块、发光管显示模块、七段数码管模块、下载器、下载线、十针连接线根。

三、实验原理及内容

.设计含异步清和同步时钟使能的十进制加法计数器。

所谓同步或异步都是相对于时钟信号而言的,不依赖于时钟而有效的信号成为异步信号,否则成为同步信号。

.百进制加法计数器的设计方法可有多种。

可利用顺序语句直接进行设计,也可先设计十进制加法计数器,然后利用元件例化语句进行级联,还可以通过原理图方式进行顶层文件的设计。

同学可根据自己的设计习惯进行随意设计。

.设计中需要用到显示模块,实验室提供的显示模块类型较多,大家可以根据课程进度情况自行选择。

初期阶段建议选择如下形式:

利用七段数码管模块显示个位数,利用发光管显示模块显示十位。

四、实验步骤

.为百进制计数器工程设计建立文件夹,注意文件夹名不能用中文,且不可带空格,文件名必须与设计实体名一致。

.说明源程序中各语句的含义。

.对所设计的百进制加法计数器工程文件进行编译,排查错误。

.选择目标芯片。

.引脚锁定。

推荐锁定形式:

输出接口选择核心板上接口,与发光管模块相连显示计数器的高位,连接后,按照编码顺序进行引脚锁定(由高到低对应的发光管为,对应引脚为、、、、、、)。

输出接口选择核心板上的接口,与七段数码管模块连接,按照顺序进行引脚锁定(、、、、、、)。

复位信号可选择核心板上面的按键,对应引脚为。

时钟信号可选择引脚,用引线将此引脚与标准时钟信号源中的时钟相连,可任意选择时钟频率。

注:

输入输出接口可在核心板上十针接口中任意选择(白色接口除外),对应的引脚可在核心板上的引脚标注中查找。

.编程下载,观察硬件结果。

下载时请下载器形式请选择。

注:

如下载后硬件调试没有通过,需重新检查连接,如果修改后重新进行下载,请将下载界面中原有的*文件删除,重新加载一次,然后再下载。

.撰写实验报告册。

五、练习题

.设计百进制减法计数器。

.设计十进制加减计数器。

实验六状态机对的采样控制电路实现

一、实验目的

.熟练掌握状态机设计方法。

.全面掌握时序电路仿真分析方法。

二、实验器材

.机一台

.综合实验开发系统中:

基本核心板模块、模数转换模块模块、七段数码管显示模块、下载器、下载线、十针连接线根。

三、实验原理及内容

.是的位转换器,片内有路模拟开关,可控制个模拟量中的一个进入转换器中。

的分辨率为位,转换时间约,含锁存控制的路多路开关,输出有三态缓冲器控制,单电源供电。

.主要控制信号说明:

如图所示,是转换启动信号,高电平有效;是位通道选择地址(、、)信号的锁存信号。

当模拟量送至某一输入端(如或等),由位地址信号选择,而地址信号由锁存;是转换情况状态信号(类似于的),当启动转换约后,产生一个负脉冲,以示转换结束;在的上升沿后,若使输出使能信号为高电平,则控制打开三态缓冲器,把转换好的位数据结果输至数据总线。

至此的一次转换结束了。

图的工作时序

部分参考实验源程序:

;

;

(:

();

:

;

,,:

;

:

());

;

(,,,);定义各状态子类型

:

;

:

();

:

;

<'';

()规定各状态转换方式

><''<''<''<''<;

><''<''<''<''<启动采样信号

><''<''<''<'';

('')<;表明转换结束

<;转换结束未结束,继续等待

;

><''<''<''<''<;开启

><''<''<''<''<;开启数据锁存信号

><''<''<''<''<;

;

;

()

''<;

'''<;

;

;

()

'''<;

;

;

<;

;

.测试步骤:

建议引脚锁定为

()输入引脚锁定。

状态机时钟接(与标准时钟信号源中引脚相连);时钟与标准时钟信号源中的引脚相连;复位信号与相连;数据输入[]的链接方法为将核板上的接口与数模转换模块上的接口相连。

()输出引脚锁定。

数模转换模块上的接口中的接,接,接,接,,接(和都接),的位输出数据线接段数码管显示模块。

此部分的锁定请参考计数器设计的相关实验。

.模拟数据输入可通过改变模数转换模块中的旋钮改变。

四.实验步骤

.为需要设计的工程设计建立文件夹,注意文件夹名不能用中文,且不可带空格,文件名必须与设计实体名一致。

.说明源程序中各语句的含义。

.对所设计的采样控制电路工程文件进行编译,排查错误。

.选择目标芯片。

.引脚锁定,根据信号名与芯片引脚对照表查找。

.编程下载。

讲系统左下角的拨码开关、、向下拨,其余向上。

即使工作使能,及使能接收来自转换结束的信号。

.撰写实验报告册