电子节拍器的设计与实现.docx

《电子节拍器的设计与实现.docx》由会员分享,可在线阅读,更多相关《电子节拍器的设计与实现.docx(49页珍藏版)》请在冰豆网上搜索。

电子节拍器的设计与实现

电子节拍器的设计与实现

学院:

明光桥北技术学院

班级:

18

姓名:

文熙

学号:

2333

班内序号:

666

1、设计思想

本实验采用自顶向下设计的方法。

从整体上考虑系统的功能,划分出不同的功能模块,然后选用器件实现相应模块,反复改进、反复实践,最终完成系统的设计。

在前期,我主要是进行各个模块的测试,分别测试完成之后,再通过顶层文件进行电路的连接,实现全部的设计。

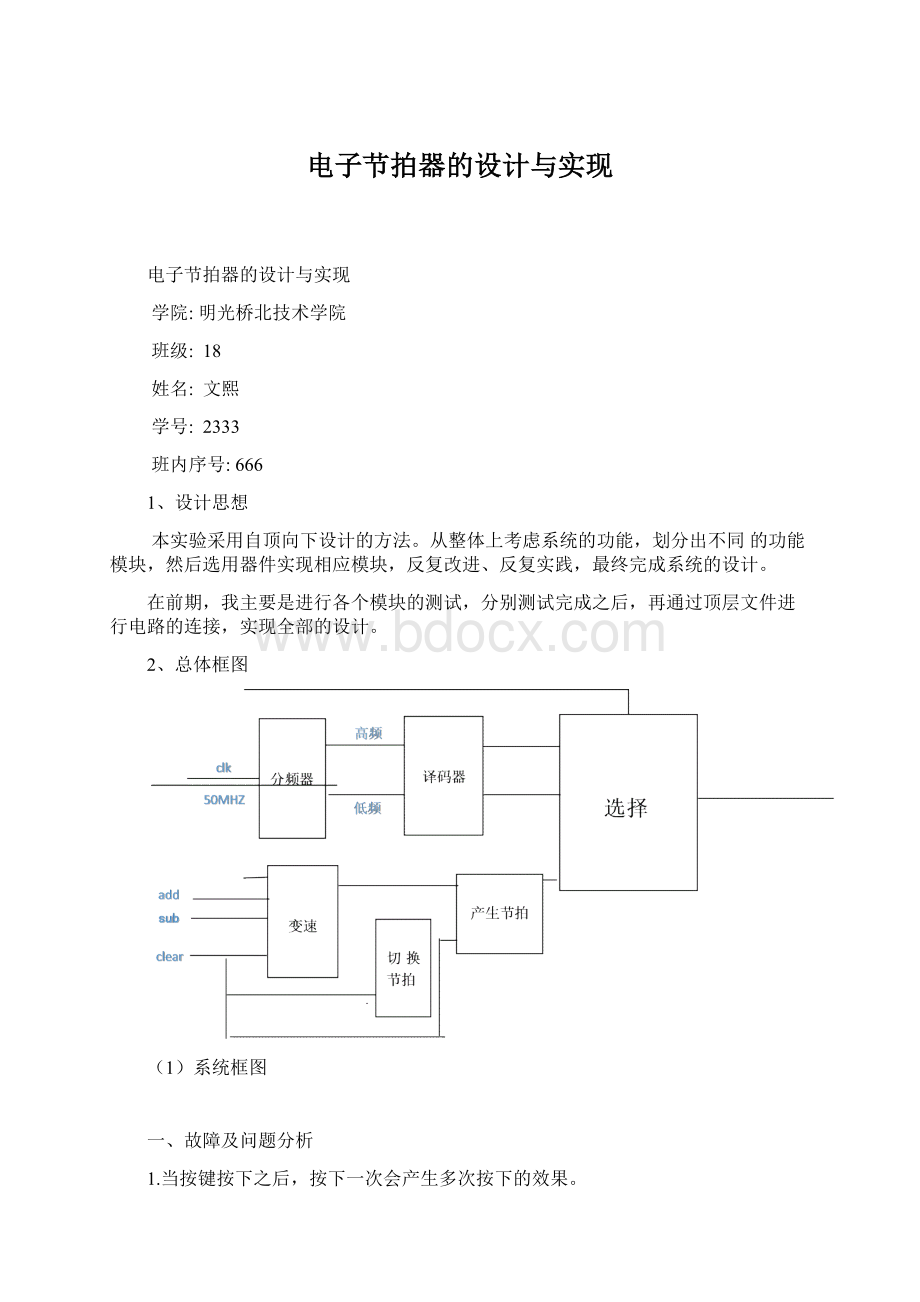

2、总体框图

(1)系统框图

一、故障及问题分析

1.当按键按下之后,按下一次会产生多次按下的效果。

问题分析与解决:

由于抖动的原因,需要加上一个防抖的程序。

2.速度加1加5的时钟计时时间偏小。

问题分析与解决:

通过实验室多次调试解决。

3.播放自制歌曲时无法进行节拍演示。

问题分析与解决:

case语句需要改进。

(由于此歌曲在验收实验前一天晚上才完成没有时间改进。

)

4.蜂鸣器一开始输入高低电平。

问题分析与解决:

后来查阅资料和同学沟通发现应该是输入不同频率的方波信号。

5.导致数码管显示不正常。

问题分析与解决:

对数码管扫描频率一开始过大,应该调整为10kHz

六、总结和结论

好人有好报----造福学弟学妹

七、源程序

顶层文件

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

ENTITYjiepaiqiIS

PORT

(

add:

INSTD_LOGIC;

sub:

INSTD_LOGIC;

clk:

INSTD_LOGIC;

clear:

INSTD_LOGIC;

state:

INSTD_LOGIC;

success:

instd_logic;

sw:

INSTD_LOGIC;

--sw1:

INSTD_LOGIC;

led1:

OUTSTD_LOGIC;

led2:

OUTSTD_LOGIC;

led3:

OUTSTD_LOGIC;

beeper0:

OUTSTD_LOGIC;

b:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

cat:

OUTSTD_LOGIC_VECTOR(5DOWNTO0)

);

ENDjiepaiqi;

ARCHITECTUREaOFjiepaiqiIS

COMPONENTbeeper

PORT(clk:

instd_logic;

clear:

instd_logic;

state:

instd_logic;

success:

instd_logic;

V1,V2,V3:

instd_logic;

show:

outstd_logic

);

ENDCOMPONENT;

COMPONENTfenpinqi

PORT(clk:

INSTD_LOGIC;

clear:

INSTD_LOGIC;

S:

INSTD_LOGIC_VECTOR(6DOWNTO0);

speed:

OUTSTD_LOGIC;

ms:

OUTSTD_LOGIC

);

ENDCOMPONENT;

COMPONENTled

PORT(speed:

INSTD_LOGIC;

clear:

INSTD_LOGIC;

J:

INSTD_LOGIC_VECTOR(2DOWNTO0);

V1:

OUTSTD_LOGIC;

V2:

OUTSTD_LOGIC;

V3:

OUTSTD_LOGIC

);

ENDCOMPONENT;

COMPONENTpace

PORT(sw:

INSTD_LOGIC;

clear:

INSTD_LOGIC;

J:

OUTSTD_LOGIC_VECTOR(2DOWNTO0)

);

ENDCOMPONENT;

COMPONENTsmgymq

PORT(clk:

INSTD_LOGIC;

clear:

INSTD_LOGIC;

J:

INSTD_LOGIC_VECTOR(2DOWNTO0);

S:

INSTD_LOGIC_VECTOR(6DOWNTO0);

b:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

cat:

OUTSTD_LOGIC_VECTOR(5DOWNTO0)

);

ENDCOMPONENT;

COMPONENTspeeder

PORT(add:

INSTD_LOGIC;

sub:

INSTD_LOGIC;

clear:

INSTD_LOGIC;

clk:

INSTD_LOGIC;

S:

OUTSTD_LOGIC_VECTOR(6DOWNTO0)

);

ENDCOMPONENT;

COMPONENTfenpinqismg

PORT(clk:

INSTD_LOGIC;

clear:

INSTD_LOGIC;

clkout:

OUTSTD_LOGIC

);

ENDCOMPONENT;

SIGNALSW_0:

STD_LOGIC;

SIGNALSW_1:

STD_LOGIC;

SIGNALSW_2:

STD_LOGIC;

SIGNALSW_10:

STD_LOGIC_VECTOR(6DOWNTO0);

SIGNALSW_4:

STD_LOGIC;

SIGNALSW_11:

STD_LOGIC_VECTOR(2DOWNTO0);

SIGNALSW_6:

STD_LOGIC;

SIGNALSW_9:

STD_LOGIC;

BEGIN

led1<=SW_0;

led2<=SW_1;

led3<=SW_2;

u1:

beeper

PORTMAP(clk=>clk,

clear=>clear,

state=>state,

success=>success,

V1=>SW_0,

V2=>SW_1,

V3=>SW_2,

show=>beeper0);

u2:

fenpinqi

PORTMAP(clk=>clk,

clear=>clear,

S=>SW_10,

speed=>SW_4,

ms=>SW_9);

u3:

led

PORTMAP(speed=>SW_4,

clear=>clear,

J=>SW_11,

V1=>SW_0,

V2=>SW_1,

V3=>SW_2);

u4:

pace

PORTMAP(sw=>sw,

clear=>clear,

J=>SW_11);

u5:

smgymq

PORTMAP(clk=>SW_6,

clear=>clear,

J=>SW_11,

S=>SW_10,

b=>b,

cat=>cat);

u6:

speeder

PORTMAP(add=>add,

sub=>sub,

clear=>clear,

clk=>SW_9,

S=>SW_10);

u7:

fenpinqismg

PORTMAP(clk=>clk,

clear=>clear,

clkout=>SW_6);

ENDa;

数码管分频器

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityfenpinqismgis

port(

clk,clear:

instd_logic;

clkout:

outstd_logic);

endfenpinqismg;

architectureaoffenpinqismgis

signaltemp:

integerrange0to2499;

signalclk_tmp:

std_logic;

begin

process(clk,clear)

begin

ifclear='0'then

temp<=0;

clk_tmp<='0';

else

ifclk'eventandclk='1'then

iftemp=2499then

temp<=0;

clk_tmp<=notclk_tmp;

else

temp<=temp+1;

endif;

endif;

endif;

clkout<=clk_tmp;

endprocess;

end;

速度调节

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityspeederis

port(

add,sub,clear,clk:

instd_logic;

S:

outstd_logic_vector(6downto0));

endspeeder;

architectureaofspeederis

signalS_temp:

std_logic_vector(6downto0);

signaltime1a:

integerrange0to2000;

signaltime1b:

integerrange0to2000;

signaltime2a:

integerrange0to2000;

signaltime2b:

integerrange0to2000;

begin

process(clk)

begin

if(clk'eventandclk='1')then

-----------add----------

ifS_temp<"1010000"then--节奏速度小于120

if(add='0')then

time1a<=0;

time1b<=0;

elsif(add='1'andtime1a=2000andS_temp<"1001100")then--节奏速度小于115按键1秒速度+5

S_temp<=S_temp+5;

time1a<=0;

elsif(add='1'andtime1b=0)then

S_temp<=S_temp+1;

time1b<=time1b+1;

elsif(add='1'andtime1a<2000)then

time1a<=time1a+1;

endif;

endif;

----------sub----------

ifS_temp>"0000000"then--节奏速度大于40

if(sub='0')then

time2a<=0;

time2b<=0;

elsif(sub='1'andtim