基于CPLD的简易数字频率计.docx

《基于CPLD的简易数字频率计.docx》由会员分享,可在线阅读,更多相关《基于CPLD的简易数字频率计.docx(18页珍藏版)》请在冰豆网上搜索。

基于CPLD的简易数字频率计

一.设计总体思路,基本原理和框图

1.1.设计总体思路

采用现场可编程门阵列(FPGA)为控制核心,利用VHDL语言编程,下载烧制实现。

将所有器件集成在一块芯片上,体积大大减小的同时还提高了稳定性,可实现大规模和超大规模的集成电路,测频测量精度高,测量频率范围大,而且编程灵活、调试方便.

1.2.基本原理

众所周知,频率信号易于传输,抗干扰性强,可以获得较好的测量精度。

因此,频率检测是电子测量领域最基本的测量之一。

频率计的基本原理是用一个频率稳定度高的频率源作为基准时钟,对比测量其他信号的频率。

通常情况下计算每秒内待测信号的脉冲个数,即闸门时间为1s。

闸门时间可以根据需要取值,大于或小于1s都可以。

闸门时间越长,得到的频率值就越准确,但闸门时间越长,则每测一次频率的间隔就越长。

闸门时间越短,测得的频率值刷新就越快,但测得的频率精度就受影响。

一般取1s作为闸门时间。

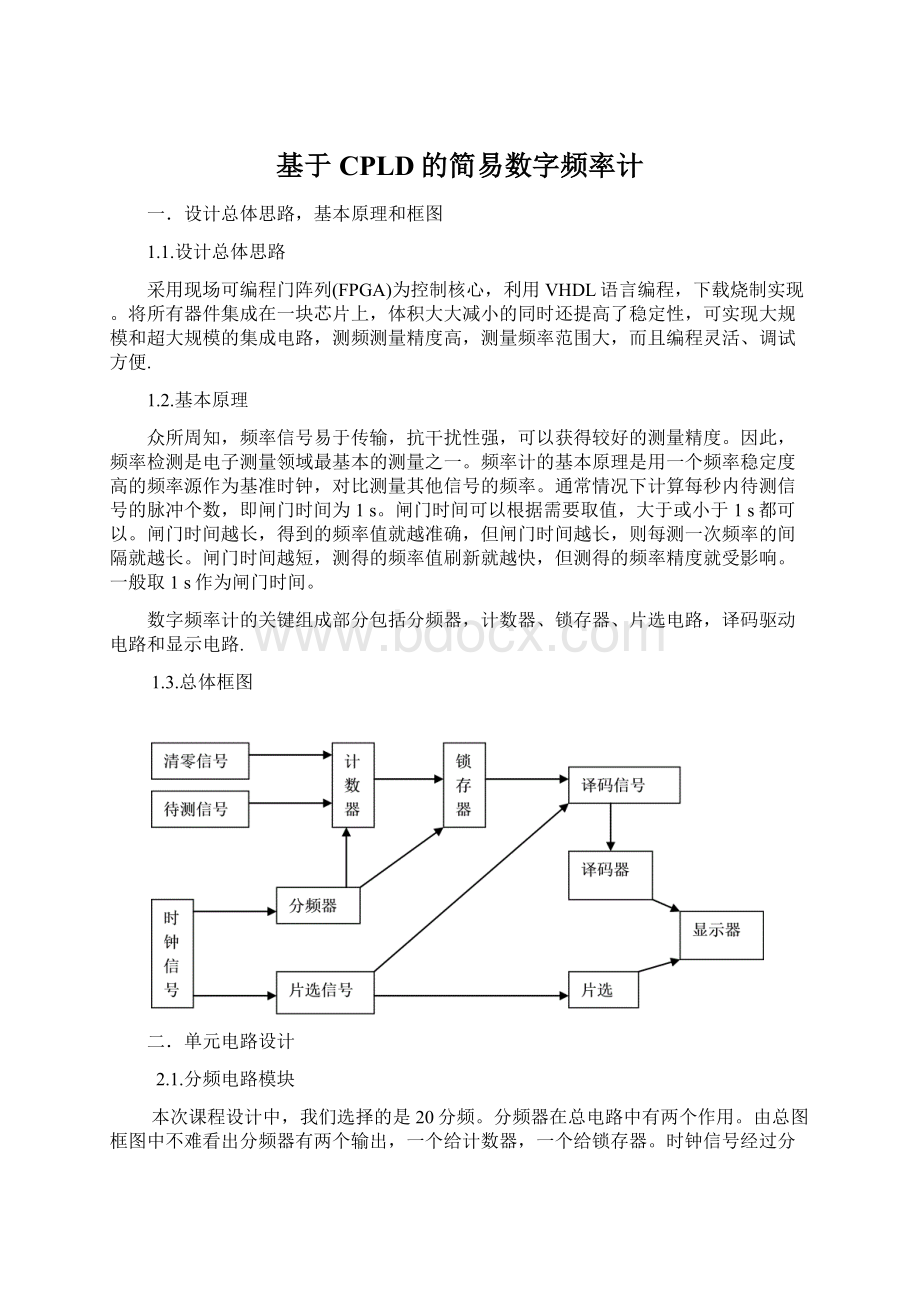

数字频率计的关键组成部分包括分频器,计数器、锁存器、片选电路,译码驱动电路和显示电路.

1.3.总体框图

二.单元电路设计

2.1.分频电路模块

本次课程设计中,我们选择的是20分频。

分频器在总电路中有两个作用。

由总图框图中不难看出分频器有两个输出,一个给计数器,一个给锁存器。

时钟信号经过分频电路形成了20分频后的门信号。

另一个给锁存器作锁存信号,当信号为低电平时就锁存计数器中的数。

其电路图如图1.

图1分频电路图

2.2.片选信号电路模块

此电路也有两用途。

一是为后面的片选电路产生片选信号,二则是为模块ch(译码信号)提供选择脉冲信号。

其电路图如图2.

图2片选信号电路图

2.3.计数器模块

计数器模块为该电路中的核心模块,它的功能是:

当门信号为上升沿时,电路开始计算半个周期内被测信号通过的周期数,到下升沿后结束。

然后送忘锁存器锁存。

其电路图如图3.

图3计数器电路图

2.4.锁存器模块

该模块在分频信号的下降沿到来时,将计数器的信号锁存,然后送给编译模块中。

其电路图如图4.

图4锁存器电路图

2.5.译码信号模块

该模块是对四个锁存器进行选择,按顺序的将四个锁存器中的数值送给译码模块中译码。

其电路图如图5.

图5译码信号电路图

2.6.片选模块

该模块接收到片选信号后,输出给显示器,选择显示那个显示管。

其电路图如图6.

图6片选电路图

2.7.译码模块

译码模块的作用就是将译码信号模块中选择出的信号进行译码,并将其送给显示器。

其电路图如图7.

图7译码电路图

三.设计仿真与调试

3.1.分频电路模块的仿真

打开quartusII后,建立工程文件,然后输入程序,保存后编译。

编译无错误既可以生成电路图。

其仿真图如图8.

图8分频电路仿真图

3.2.片选信号电路的仿真

其仿真图如图9.

图9片选信号电路仿真图

3.3.计算器模块的仿真

其仿真图如图10.

图10计算器电路仿真图

3.4.锁存器模块仿真

其仿真图如图11.

图11锁存器电路仿真图

3.5.译码信号模块的仿真

其仿真图如图12.

图12译码信号电路仿真图

3.6.片选模块的仿真

其仿真图如图13.

图13片选电路仿真图

3.7.译码器模块

其仿真图如图14.

图14译码电路仿真图

3.8.总电路图的仿真

将七个模块用导线相连,形成总电路图。

其仿真图如图15.

图15总电路仿真图

图15为总的电路图,图中alm为进位输出,clk为时钟信号,设为15us。

Clr为清零信号,点电平清零,高电平计数。

Q为显示输出端。

Sel为片选,sig为被测信号,设为1us。

图中显示结果为10011101111111101101为305.本电路为20分频。

结果应为300,考虑延时误差,测量结果正确。

3.9软件调试与硬件调试

(a)软件调试

仿真时,打开软件puartusII,建立工程文件,然后输入程序。

保存后,编译,无误后及可以仿真了。

进入界面后,先点击edict菜单,设置endtime,一般设为10ms,由于软件的缘故,endtime不要设的太小,否则延时会很大.

对总电路图仿真的时候也出现了一个问题,一开始我们怎么也仿真不出来,后来才知道总图仿真的时候也要建立工程文件,而且要将所有的模块文件加载到总电路图的文件夹中。

(b)硬件调试

软件仿真玩后,就的与硬件相连。

在这之前的先设置好管脚。

点击“assingmengt”菜单的“pinplanner”按照试验箱中的管脚设置好,确定后编译。

关闭puartus软件,将试验箱接入电脑,按提示安装。

重新打开软件,点击菜单“tools”中的”granmmer”确定接好USB接口。

将实验箱的线接好后就可以运行,看结果与仿真是否相符.

点击“start”将清零信号置低电平,显示器显示10000的字样。

将被侧信号与时钟信号设置合理的数值,将清理信号置为高电平。

显示器中就能显示器分频数值。

(c)调试结果

1.清零信号为低电平时候的显示结果如图16.

图16清零信号为低电平时的结果

图中为清零信号为低电平时,显示为0000,前面的1为在这种情况下只需要一个计数器工作。

2.清零信号置为高电平后的结果如下图图17.

图17清零信号为高电平时的显示结果

图中显示的为将被测信号为时钟信号的320倍的显示结果。

显示为0320.前面的3为需要用3个计数器工作。

四.编程下载

4.1.分频模块的程序

libraryieee;

useieee.std_logic_1164.all;

entityfenis

port(clk:

instd_logic;

q:

outstd_logic);

endfen;

architecturefen_arcoffenis

begin

process(clk)

variablecnt:

integerrange0to9;

variablex:

std_logic;

begin

ifclk'eventandclk='1'

thenifcnt<9then

cnt:

=cnt+1;

else

cnt:

=0;

x:

=notx;

endif;

endif;

q<=x;

endprocess;

endfen_arc;

4.2.片选信号模块的程序

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityselis

port(clk:

instd_logic;

q:

outstd_logic_vector(2downto0));

endsel;

architecturesel_arcofselis

begin

process(clk)

variablecnt:

std_logic_vector(2downto0);

begin

ifclk'eventandclk='1'then

cnt:

=cnt+1;

endif;

q<=cnt;

endprocess;

endsel_arc

4.3.计数器模块的程序

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitycornais

port(clr,sig,door:

instd_logic;

alm:

outstd_logic;

q3,q2,q1,q0,dang:

outstd_logic_vector(3downto0));

endcorna;

architecturecorn_arcofcornais

begin

process(door,sig)

variablec3,c2,c1,c0:

std_logic_vector(3downto0);

variablex:

std_logic;

begin

ifsig'eventandsig='1'then

ifclr='0'then

alm<='0';

c3:

="0000";

c2:

="0000";

c1:

="0000";

c0:

="0000";

elsifdoor='0'then

c3:

="0000";

c2:

="0000";

c1:

="0000";

c0:

="0000";

elsifdoor='1'then

ifc0<"1001"then

c0:

=c0+1;

else

c0:

="0000";

ifc1<"1001"then

c1:

=c1+1;

elsec1:

="0000";

ifc2<"1001"then

c2:

=c2+1;

else

c2:

="0000";

ifc3<"1001"then

c3:

=c3+1;

else

c3:

="0000";

alm<='1';

endif;

endif;

endif;

endif;

endif;

ifc3/="0000"then

q3<=c3;

q2<=c2;

q1<=c1;

q0<=c0;

dang<="0100";

elsifc2/="0000"then

q3<="0000";

q2<=c2;

q1<=c1;

q0<=c0;

dang<="0011";

elsifc1/="0000"then

q3<="0000";

q2<="0000";

q1<=c1;

q0<=c0;

dang<="0010";

else

q3<="0000";

q2<="0000";

q1<="0000";

q0<=c0;

dang<="0001";

endif;

endif;

endprocess;

endcorn_arc;

4.4.锁存器模块的程序

libraryieee;

useieee.std_logic_1164.all;

entitylockis

port(l:

instd_logic;

a4,a3,a2,a1,a0:

instd_logic_vector(3downto0);

q4,q3,q2,q1,q0:

outstd_logic_vector(3downto0));

endlock;

architecturelock_arcoflockis

begin

process(l)

variablet4,t3,t2,t1,t0:

std_logic_vector(3downto0);

begin

ifl'eventandl='0'then

t4:

=a4;

t3:

=a3;

t2:

=a2;

t1:

=a1;

t0:

=a0;

endif;

q4<=t4;

q3<=t3;

q2<=t2;

q1<=t1;

q0<=t0;

endprocess;

endlock_arc;

4.5.译码信号模块的程序

libraryieee;

useieee.std_logic_1164.all;

entitychis

port(sel:

instd_logic_vector(2downto0);

a3,a2,a1,a0,dang:

instd_logic_vector(3downto0);

q:

outstd_logic_vector(3downto0));

endch;

architecturech_arcofchis

begin

process(sel)

begin

caseselis

when"000"=>q<=a0;

when"001"=>q<=a1;

when"010"=>q<=a2;

when"011"=>q<=a3;

when"111"=>q<=dang;

whenothers=>q<="1111";

endcase;

endprocess;

endch_arc;

4.6.片选模块的程序

libraryieee;

useieee.std_logic_1164.all;

entityymis

port(d:

instd_logic_vector(2downto0);

q:

outstd_logic_vector(7downto0));

endym;

architectureym_arcofymis

begin

process(d)

begin

casedis

when"000"=>q<="00000001";

when"001"=>q<="00000010";

when"010"=>q<="00000100";

when"011"=>q<="00001000";

when"100"=>q<="00010000";

when"101"=>q<="00100000";

when"110"=>q<="01000000";

when"111"=>q<="10000000";

whenothers=>q<="00000000";

endcase;

endprocess;

endym_arc;

4.7.译码器模块的程序

libraryieee;

useieee.std_logic_1164.all;

entitydispis

port(d:

instd_logic_vector(3downto0);

q:

outstd_logic_vector(6downto0));

enddisp;

architecturedisp_arcofdispis

begin

process(d)

begin

casedis

when"0000"=>q<="0111111";

when"0001"=>q<="0000110";

when"0010"=>q<="1011011";

when"0011"=>q<="1001111";

when"0100"=>q<="1100110";

when"0101"=>q<="1101101";

when"0110"=>q<="1111101";

when"0111"=>q<="0100101";

when"1000"=>q<="1111111";

when"1001"=>q<="1101111";

whenothers=>q<="0000000";

endcase;

endprocess;

enddisp_arc;

五.总结与体会

通过为期两周的课程设计,完成了本次设计的技术指标,刚开始设计的时候,由于vhdl语言编写程序这部分比较难搞定,经过后来老师的指导,才慢慢掌握方向,最后顺利完成老师下达的任务。

本次实习让我们体味到设计电路、连接电路、调试电路过程中的乐苦与甜。

设计是我们将来必需的技能,这次实习恰恰给我们提供了一个应用自己所学知识的机会,从到图书馆查找资料到对电路的设计对电路的调试再到最后电路的成型,都对我所学的知识进行了检验。

在实习的过程中发现了以前学的知识掌握的不牢。

制作过程是一个考验人耐心的过程,不能有丝毫的急躁,马虎,对电路的调试要一步一步来,不能急躁,因为是在电脑上调试,比较慢,又要求我们有一个比较正确的调试方法,像把频率调准等等。

这又要我们要灵活处理,在不影响试验的前提下可以加快进度。

合理的分配时间。

在设计电路的时候,最重要的是要熟练地掌握课本上的知识,这样才能对试验中出现的问题进行分析解决。

在整个课程设计完后,总的感觉是:

有收获。

以前上课都是上一些最基本的东西而现在却可以将以前学的东西作出有实际价值的东西。

在这个过程中,我的确学得到很多在书本上学不到的东西,但也遇到了不少的挫折,有时遇到了一个错误怎么找也找不到原因所在,像puartusII软件仿真时,如果时间设计的不对,波形怎么也出不来。

在学习中的小问题在课堂上不可能犯,在动手的过程中却很有可能犯。

特别是在接电路时,一不小心就会犯错,而且很不容易检查出来。

但现在回过头来看,还是挺有成就感的。

我的动手能力又有了进一步的提高,我感到十分的高兴。

巩固了课堂上所学到的理论性的知识,通过紧张有序的设计实践,我觉得自己的动手能力有了很大的提高;自信心也增强了.在课程设计中自己动脑子解决遇到的问题,书本上的知识有了用武之地,这又巩固和深化了自己的知识结构。

由于种种原因,我们实习之前准备严重不足,包括心理上和自身能力上,在这之前同学们对实习内容了解的并不多,对实习中必须用到eda知识几乎没有多少,所以自然地就造成了许多不必要的时间上的浪费,我建议以后老师们能够在课堂外利用空闲的时间多讲解一下有关此方面的知识,让同学们提前有所准备,对实验内容有所了解,相信做的时候大家必会感到更加轻松吧。

最后还是要感谢老师的耐心指导,真是辛苦你了。

希望我做出来的成果能让你感到欣慰。

九.附录

总电路图如图18.

图15总电路图

十.参考文献

1.康华光主编.电子技术基础(数字部分),高等教育出版社。

2.阎石主编.电子技术基础(数字部分),清华大学出版社。

3.陈大钦主编,电子技术基础实验,高等教育出版社。

4.彭介华主编,电子技术课程设计指导,高等教育出版社。

5.张原编著,可编程逻辑器件设计及应用,机械工业出版社。

6.荀殿栋,徐志军编著,数字电路设计实用手册,电子工业出版社。

7.刘洪喜,陆颖编著.VHDL电路设计实用教程清华大学出版社