VHDL实验指导书.docx

《VHDL实验指导书.docx》由会员分享,可在线阅读,更多相关《VHDL实验指导书.docx(49页珍藏版)》请在冰豆网上搜索。

VHDL实验指导书

实验一QuartusII软件应用

一、实验目的

1、熟悉EDA开发平台的基本操作。

2、掌握EDA开发工具的图形设计方法。

3、掌握图形设计的编译与验证方法。

二、实验仪器

PC机一台 QuartusII 软件

三、实验内容

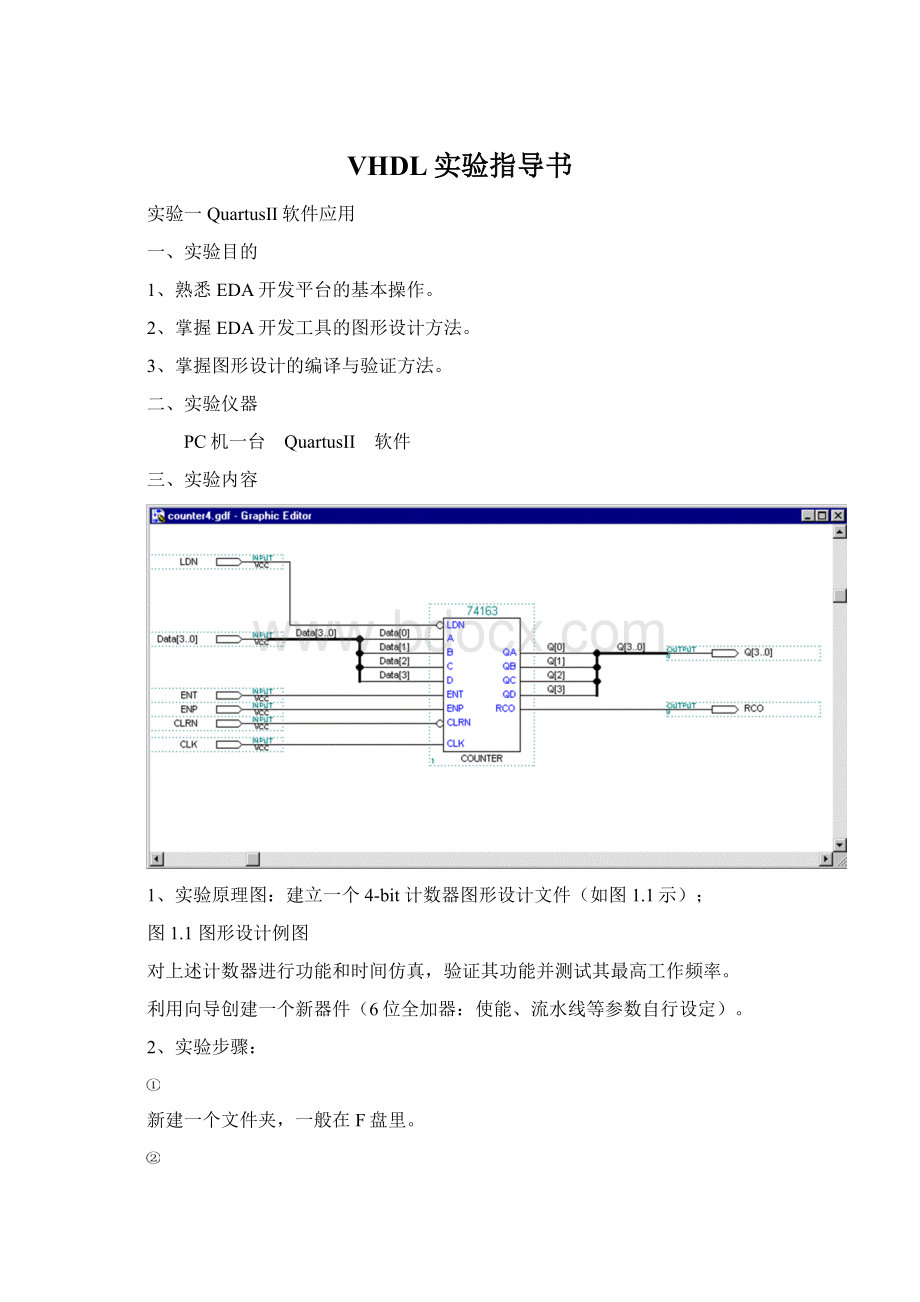

1、实验原理图:

建立一个4-bit计数器图形设计文件(如图1.1示);

图1.1图形设计例图

对上述计数器进行功能和时间仿真,验证其功能并测试其最高工作频率。

利用向导创建一个新器件(6位全加器:

使能、流水线等参数自行设定)。

2、实验步骤:

新建一个文件夹,一般在F盘里。

打开QuartusII软件,选择File/New,在弹出的窗口中选DeviceDesignFiles选项卡,再选择BlockDiagram/Schematic选项,单击OK后打开图形编辑窗口。

选择File/SaveAs命令,保存文件在已经创建的文件夹里。

当出现询问是否创建工程的窗口,应当单击是进入创建工程流程,否则要重新创建工程把文件添加进去。

打开工程中的原理图文件,在原理图编辑窗口的任何一个位置右击,将出现快捷菜单,选择Insert/Symbol命令,出现元件输入对话框,选择相应的器件,并连接好电路,然后分别在input和output的PINNAME上双击使其变黑色,再分别输入引脚名。

选择Processing/StartCompilation命令,进行全程编译。

打开波形编辑器,选择File/New,在New中选择OtherFiles中的VectorWaveformFile选项,单击OK,出现空白的波形编译窗口

选择File/SaveAs命令,存盘。

文件名一定要与原理图文件名一致。

然后添加相应的端口信号节点到波形编辑器中,设置合理的输入信号。

选择Processing/StartSimulation,进行波形仿真。

选择Processing/ClassicTimingAnalyzerTool测试最高工作频率。

选择Tools/MegaWizardPlug-InManager,根据向导提示创建一个6位全加器。

3、实验结果记录:

打印出实验原理图与仿真波形图,写出最高工作频率,打印出利用向导创建的新器件的图形,完成实验报告

四、实验研究与思考

1、延迟时间分析、最高工作频率分析等时间分析有何重要性?

2、流水线的作用是什么?

对那些性能有影响?

2、功能仿真、验证起到什么作用?

实验二VHDL软件设计

一、实验目的

1、熟悉EDA开发平台的基本操作。

2、掌握EDA开发工具的VHDL设计方法。

3、掌握硬件描述语言设计的编译与验证方法。

二、实验仪器

PC机一台 QuartusII 软件

三、实验内容

1、24进制加法计数器的程序:

LIBRARYIeee;

USEieee.std_logic_1164.ALL;

USEieee.std_logic_unsigned.ALL;

ENTITYcount24IS

PORT(en,clk:

INSTD_LOGIC;

qa:

outSTD_LOGIC_VECTOR(3DOWNTO0);

--个位数计数

qb:

outSTD_LOGIC_VECTOR(1DOWNTO0));

--十位数计数

ENDcount24;

ARCHITECTUREa1OFcount24IS

BEGIN

process(clk)

variabletma:

STD_LOGIC_VECTOR(3DOWNTO0);

variabletmb:

STD_LOGIC_VECTOR(1DOWNTO0);

begin

ifclk'eventandclk='1'then

ifen='1'then

iftma="1001"thentma:

="0000";tmb:

=tmb+1;

Elsiftmb="10"andtma="0011"thentma:

="0000";

tmb:

="00";

elsetma:

=tma+1;

endif;

endif;

endif;

qa<=tma;

qb<=tmb;

endprocess;

ENDa1;

2、实验步骤:

1)24进制计数器

新建一个文件夹,一般在F盘里。

打开QuartusII软件,选择File/New,在弹出的窗口中选DeviceDesignFiles选项卡,再选择VHDLFile选项,单击OK后打开程序编辑窗口。

选择File/SaveAs命令,保存文件在已经创建的文件夹里,文件名一定要与程序的实体名一致。

当出现询问是否创建工程的窗口,应当单击是进入创建工程流程,否则要重新创建工程把文件添加进去。

打开工程中的程序文件,把1中24进制加法计数器的程序输入。

选择Processing/StartCompilation命令,进行全程编译。

打开波形编辑器,选择File/New,在New中选择OtherFiles中的VectorWaveformFile选项,单击OK,出现空白的波形编译窗口。

选择File/SaveAs命令,存盘。

文件名一定要与原理图文件名一致。

然后添加相应的端口信号节点到波形编辑器中,设置合理的输入信号。

选择Processing/StartSimulation,进行波形仿真。

2)修改以上程序获得60进制加法计数器,并进行功能和时间仿真验证。

3、实验结果记录:

手写出24进制与60进制的加法器的实验程序,打印出仿真波形图,完成实验报告

四、实验研究与思考

1、比较图形设计和语言设计方法的差别和优缺点。

实验三3-8译码器

一、实验目的

1、掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、初步掌握EDA软件的基本操作与应用。

4、初步了解可编程器件的设计全过程。

二、实验仪器

PC机一台 QuartusII 软件

三、实验内容

1、新建一个设计工程;

2、输入并连接如图3.1所示原理图;

图3.13-8译码器原理图

3、选择目标器件(EP1C3T144C8);

4、编译与适配;

5、波形文件输入与设定,功能仿真与验证;

6、管脚锁定;

7、器件编程下载;

8、硬件测试;

9、采用VHDL语言描述以上3-8译码器,并重复以上4-8项;

9、自行设计纪录方式,完成实验报告

四、实验研究与思考

1、组合逻辑电路的设计应该注意什么问题?

实验四组合逻辑电路的VHDL描述

一、实验目的

1、掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、熟悉FPGA设计的过程,比较原理图输入和文本输入的优劣。

二、实验仪器

PC机一台 QuartusII 软件

三、实验内容

1、用VHDL语言设计一个四舍五入判别电路,其输入为8421BCD码,要求当输入大于或等于5时,判别电路输出为1,反之为0。

参考电路原理图如图4.1所示。

图4.1四舍五入判别参考电路

2、用VHDL语言设计四个开关控制一盏灯的逻辑电路,要求改变任意开关的状态能够引起灯亮灭状态的改变。

(即任一开关的合断改变原来灯亮灭的状态,参考电路原理图如图4.2所示。

)

图4.2灯控参考电路

3、用VHDL语言设计一个优先排队电路(参考电路原理图如图4.3所示),其中:

A=1,最高优先级;B=1,次高优先级;C=1,最低优先级。

要求输出端最多只能有一端为“1”,即只能是优先级较高的输入端所对应的输出端为“1”。

图4.3优先排队参考电路

4、自行设计纪录方式,完成实验报告

四、实验研究与思考

1、CPLD和FPGA有什么差别?

设计中应该注意什么问题?

2、图形设计方法中采用LPM设计有什么好处?

实验五触发器的VHDL描述

一、实验的目的

1、掌握触发器功能的测试方法。

2、掌握基本RS触发器的组成及工作原理。

3、掌握集成JK触发器和D触发器的逻辑功能及触发方式。

4、掌握几种主要触发器之间相互转换的方法。

5、通过实验、体会CPLD芯片的高集成度和多I/O口。

二、实验仪器

PC机一台 QuartusII 软件

三、实验内容

1、用VHDL语言设计基本RS触发器、同步RS触发器、J-K触发器、D触发器,并将这些触发器集成于一个电路(芯片)中(参考设计电路如图5.1所示),并研究其相互转换的方法。

图5.1触发器设计参考电路

2、编译、仿真、管脚锁定和器件编成下载后进行硬件测试并纪录测试结果到下列各触发器的真值表中。

表一:

RS寄存器

Rd

Sd

Q

NQ

说明

0

1

1

0

1

1

0

0

表二:

RS锁存器

R

S

CLK1

Rd

Sd

Qn

Qn+1

Qn-1

说明

X

X

X

1

0

X

X

X

0

1

X

X

X

0

0

X

X

0

1

1

0

0

1

1

1

0

1

1

1

1

1

0

1

1

1

1

1

1

1

1

表三:

D触发器

INPUTS

OUTPUTS

D

CLK2

Rd

Sd

Q

NQ

X

X

0

1

X

X

1

0

X

X

0

0

X

0

1

1

X

1

1

1

0

↑

1

1

1

↑

1

1

表四:

JK触发器

J

K

CLK1

Rd

Sd

Qn

Qn+1

NQn+1

X

X

X

0

1

X

X

X

1

0

X

X

X

0

0

X

X

0

1

1

X

X

1

1

1

0

0

※

1

1

0

1

※

1

1

1

0

↓

1

1

1

1

↓

1

1

4、分别将JK触发器和D触发器接成T触发器,模拟其工作状态,并画出其波形图。

5、自行设计纪录方式,完成实验报告

四、实验研究与思考

1、时序电路的设计与组合电路的设计有何差别?

2、时序电路的同步设计和异步设计有何不同?

3、异步设计的竞争冒险现象如何产生,应该如何克服竞争冒险现象?

实验六扫描显示驱动电路

一、实验目的

1、了解实验系统中8位八段数码管显示模块的工作原理;

2、掌握计数器和地址发生器的VHDL描述方法;

3、掌握LED数码管7段译码器的VHDL描述方法;

4、掌握编码器的VHDL描述方法;

5、设计标准扫描驱动电路模块,以备后面实验用。

二、实验仪器

PC机一台 QuartusII 软件EDA实验箱

三、实验内容

图6.1所示的是8位数码扫描显示电路,其中每个数码管的8个段:

h、g、f、e、d、c、b、a(h是小数点)都分别连在一起,8个数码管分别由8个选通信号k1、k2、…k8来选择。

被选通的数码管显示数据,其余关闭。

如在某一时刻,k3为高电平,其余选通信号为低电平,这时仅k3对应的数码管显示来自段信号端的数据,而其它7个数码管呈现关闭状态。

根据这种电路状况,如果希望在8个数码管显示希望的数据,就必须使得8个选通信号k1、k2、…k8分别被单独选通,并在此同时,在段信号输入口加上希望在该对应数码管上显示的数据,于是随着选通信号的扫变,就能实现扫描显示的目的。

其VHDL示例程序如程序10.1所示。

图6.18位数码扫描显示电路图

1、实验内容1:

理解程序中各语句的含义,以及该例的整体功能。

对该例进行编辑、编译、综合、适配、仿真,给出仿真波形。

实验方式:

若考虑小数点,SG的8个段分别与PIO49、PIO48、…、PIO42(高位在右)、BT的8个位分别与PIO34、PIO35、…、PIO41(高位在左);电路模式不限,引脚图参考附图11。

将GW48EDA系统左下方的拨码开关全部向上拨,这时实验系统的8个数码管构成图10.1的电路结构,时钟CLK可选择clock0,通过跳线选择16384Hz信号。

引脚锁定后进行编译、下载和硬件测试实验。

将实验过程和实验结果写进实验报告。

2、自行设计纪录方式,完成实验报告

【例5.1】

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYSCAN_LEDIS

PORT(CLK:

INSTD_LOGIC;

SG:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);--段控制信号输出

BT:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));--位控制信号输出

END;

ARCHITECTUREoneOFSCAN_LEDIS

SIGNALCNT8:

STD_LOGIC_VECTOR(2DOWNTO0);

SIGNALA:

INTEGERRANGE0TO15;

BEGIN

P1:

PROCESS(CNT8)--编码器

BEGIN

CASECNT8IS

WHEN"000"=>BT<="00000001";A<=1;

WHEN"001"=>BT<="00000010";A<=3;

WHEN"010"=>BT<="00000100";A<=5;

WHEN"011"=>BT<="00001000";A<=7;

WHEN"100"=>BT<="00010000";A<=9;

WHEN"101"=>BT<="00100000";A<=11;

WHEN"110"=>BT<="01000000";A<=13;

WHEN"111"=>BT<="10000000";A<=15;

WHENOTHERS=>NULL;

ENDCASE;

ENDPROCESSP1;

P2:

PROCESS(CLK)--计数器

BEGIN

IFCLK'EVENTANDCLK='1'THENCNT8<=CNT8+1;

ENDIF;

ENDPROCESSP2;

P3:

PROCESS(A)–-译码电路

BEGIN

CASEAIS

WHEN0=>SG<="0111111";WHEN1=>SG<="0000110";

WHEN2=>SG<="1011011";WHEN3=>SG<="1001111";

WHEN4=>SG<="1100110";WHEN5=>SG<="1101101";

WHEN6=>SG<="1111101";WHEN7=>SG<="0000111";

WHEN8=>SG<="1111111";WHEN9=>SG<="1101111";

WHEN10=>SG<="1110111";WHEN11=>SG<="1111100";

WHEN12=>SG<="0111001";WHEN13=>SG<="1011110";

WHEN14=>SG<="1111001";WHEN15=>SG<="1110001";

WHENOTHERS=>NULL;

ENDCASE;

ENDPROCESSP3;

END;

例6.1是扫描显示的示例程序,其中clk是扫描时钟;SG为7段控制信号,由高位至低位分别接g、f、e、d、c、b、a7个段;BT是位选控制信号,接图5-20中的8个选通信号:

k1、k2、…k8。

程序中CNT8是一个3位计数器,作扫描计数信号,由进程P2生成;进程P3是7段译码查表输出程序,与例5-18相同;进程P1是对8个数码管选通的扫描程序,例如当CNT8等于"001"时,K2对应的数码管被选通,同时,A被赋值3,再由进程P3译码输出"1001111",显示在数码管上即为“3”;当CNT8扫变时,将能在8个数码管上显示数据:

13579BDF。

四、实验研究与思考

1、字形编码的种类,即一个8段数码管可产生多少种字符,产生所有字符需多少根译码信号线?

2、字符显示亮度和扫描频率的关系,且让人感觉不出光烁现象的最低扫描频率是多少?

3、扫描显示和静态显示有什么差别?

使用扫描显示有什么好处?

实验七VHDL硬件设计

-------计数器及时序电路描述

一、实验目的

1、了解时序电路的经典设计方法(JK触发器和一般逻辑门组成的时序逻辑电路)。

2、了解同步计数器,异步计数器的使用方法。

3、了解同步计数器通过清零阻塞法和预显数法得到循环任意进制计数器的方法。

4、理解时序电路和同步计数器加译码电路的联系,设计任意编码计数器。

5、了解同步设计和异步设计的区别。

二、实验仪器

PC机一台 QuartusII 软件EDA实验箱

三、实验内容

实验内容中的六个实验均要通过实验十的“扫描显示电路”进行显示,具体连线根据每个实验内容完成时的管脚分配来定义,同相应的输入输出接口功能模块相连,扫描模块的设计参考实验十。

1、用JK触发器设计异步四位二进制加法计数器。

8位LED数码管16进制显示扫描显示驱动电路设计,实验参考原理图如图7.1所示。

其中,计数时钟频率CLK<2Hz;扫描时钟频率>40Hz;四位JK触发器接成异步计数器;SEL0~SEL2为扫描地址(控制八位数码管的扫描顺序和速度);A……G为显示译码输出,代表数码管的八个段位(a,b,c,d,e,f,g);八位数码管同时顺序显示0~F。

图7.1计数器设计参考原理图

3.绘制原理图后进行仿真验证,最后下载到实验箱。

4、自行设计纪录方式,完成实验报告

四、实验研究与思考

1、说明在FPGA设计中,同步设计和异步设计的不同之处。

2、图形设计和VHDL语言设计编程各有什么优点,混合编程时应注意些什么问题?

3、应用状态机设计时序电路需要注意哪些问题?

实验八模拟信号检测

一、实验目的

1、掌握状态机设计方法。

2、了解ADC0809的工作原理和采样控制时序。

3、设计A/D转换器ADC0809的采样控制电路。

4、掌握VHDL语言的仿真验证方法。

二、实验仪器

计算机、QuartusII软件、EDA试验箱、示波器。

三、实验内容

1、原理:

ADC0809是CMOS的8位A/D转换器,片内有8路模拟开关,可控制8个模拟量中的一个进入转换器中。

转换时间约100μs,含锁存控制的8路多路开关,输出有三态缓冲器控制,单5V电源供电。

主要控制信号如图81所示:

START是转换启动信号,高电平有效;ALE是3位通道选择地址(ADDC、ADDB、ADDA)信号的锁存信号。

当模拟量送至某一输入端(如IN1或IN2等),由3位地址信号选择,而地址信号由ALE锁存;EOC是转换情况状态信号,当启动转换约100μs后,EOC产生一个负脉冲,以示转换结束;在EOC的上升沿后,若使输出使能信号OE为高电平,则控制打开三态缓冲器,把转换好的8位数据结果输至数据总线,至此ADC0809的一次转换结束。

:

图81ADC0809工作时序

2、实验示例程序如81。

【例81】

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYADCINTIS

PORT(D:

INSTD_LOGIC_VECTOR(7DOWNTO0);--来自0809转换好的8位数据

CLK:

INSTD_LOGIC;--状态机工作时钟

EOC:

INSTD_LOGIC;--转换状态指示,低电平表示正在转换

ALE:

OUTSTD_LOGIC;--8个模拟信号通道地址锁存信号

START:

OUTSTD_LOGIC;--转换开始信号

OE:

OUTSTD_LOGIC;--数据输出3态控制信号

ADDA:

OUTSTD_LOGIC;--信号通道最低位控制信号

LOCK0:

OUTSTD_LOGIC;--观察数据锁存时钟

Q:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));--8位数据输出

ENDADCINT;

ARCHITECTUREbehavOFADCINTIS

TYPEstatesIS(st0,st1,st2,st3,st4);--定义各状态子类型

SIGNALcurrent_state,next_state:

states:

=st0;

SIGNALREGL:

STD_LOGIC_VECTOR(7DOWNTO0);

SIGNALLOCK:

STD_LOGIC;--转换后数据输出锁存时钟信号

BEGIN

ADDA<='1';--当ADDA<='0',模拟信号进入通道IN0;当ADDA<='1',则进入通道IN1

Q<=REGL;LOCK0<=LOCK;

COM:

PROCESS(current_state,EOC)

BEGIN--规定各状态转换方式

CASEcurrent_stateIS

WHENst0=>ALE<='0';START<='0';LOCK<='0';OE<='0';next_state<=st1;--0809初始化

WHENst1=>ALE<='1';START<='1';LOCK<='0';OE<='0';next_state<=st2;--启动采样

WHENst2=>ALE<='0';START<='0';LOCK<='0';OE<='0';

IF(EOC='1')THENnext_state<=st3;--EOC=1表明转换结束

ELSEnext_state<=st2;

ENDIF;--转换未结束,继续等待

WHENst3=>ALE<='0';START<='0';LOCK<='0';

OE<='1';next_state<=st4;--开启OE,输出转换好的数据

WHENst4=>ALE<='0';START<='0';LOCK<='1';OE<='1';next_state<=st0;

WHENOTHERS=>next_state<=st0;

ENDCASE;

ENDPROCE