PCIE详细设计.docx

《PCIE详细设计.docx》由会员分享,可在线阅读,更多相关《PCIE详细设计.docx(11页珍藏版)》请在冰豆网上搜索。

PCIE详细设计

PCIExpress

详细设计

PCIExpress详细设计

1PCIExpress介绍

PCIE设备按照一定的拓扑连接构成总线结构,设备与设备通过协议规定的事务包(TLP)进行通信。

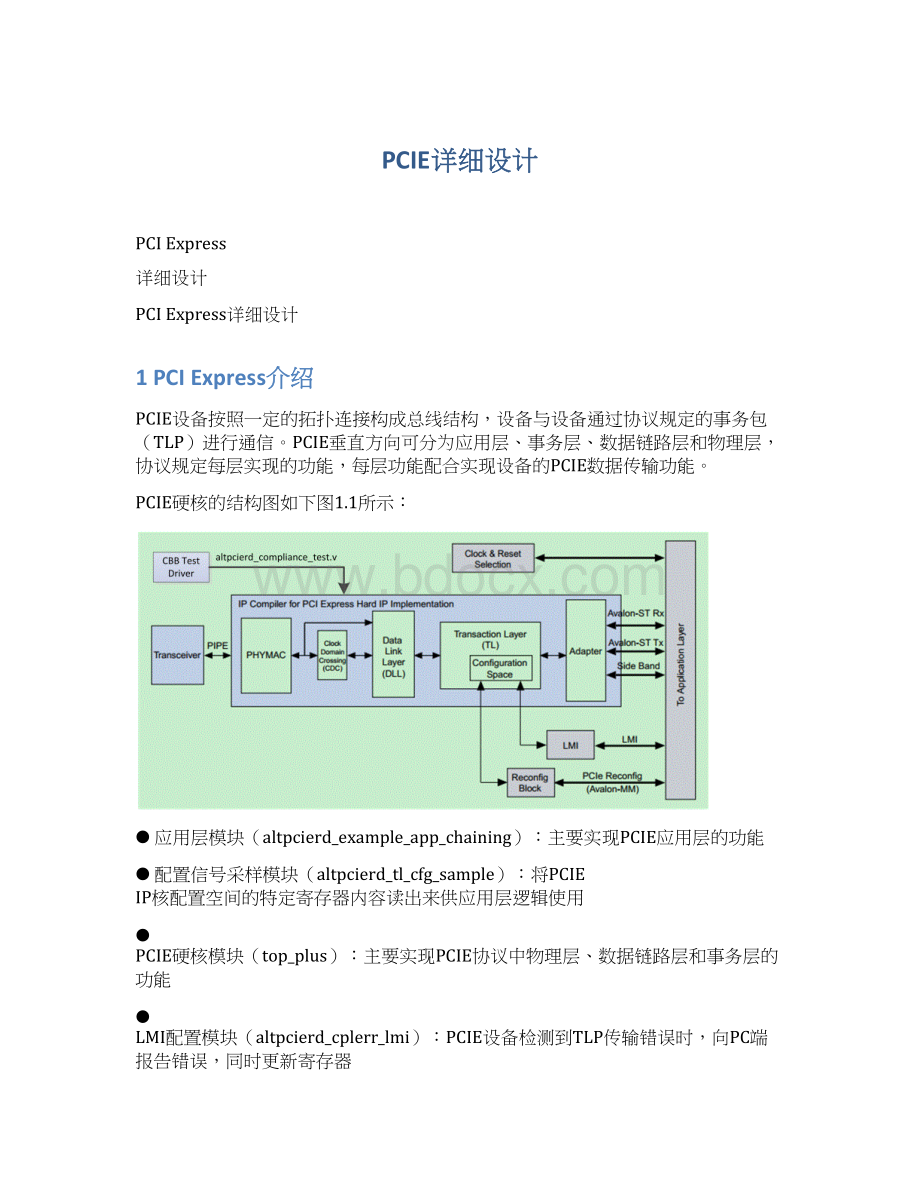

PCIE垂直方向可分为应用层、事务层、数据链路层和物理层,协议规定每层实现的功能,每层功能配合实现设备的PCIE数据传输功能。

PCIE硬核的结构图如下图1.1所示:

●应用层模块(altpcierd_example_app_chaining):

主要实现PCIE应用层的功能

●配置信号采样模块(altpcierd_tl_cfg_sample):

将PCIEIP核配置空间的特定寄存器内容读出来供应用层逻辑使用

●PCIE硬核模块(top_plus):

主要实现PCIE协议中物理层、数据链路层和事务层的功能

●LMI配置模块(altpcierd_cplerr_lmi):

PCIE设备检测到TLP传输错误时,向PC端报告错误,同时更新寄存器

●重新配置时钟模块(altpcierd_reconfig_clk_pll):

实现IP核和其他模块时钟的配置

●兼容性测试模块(altpcierd_compliance_test):

用于测试系统或设备的互操作性和一致性(通过按键完成CBB)

2PCIExpress参数与接口

表4-1PCIE模块接口

InterfaceName

Direction

Description

free_100MHz

in

本地时钟信号

local_rstn_ext

in

本地复位信号

pcie_rstn

in

PCIE复位信号

refclk

in

参考时钟

req_compliance_push_button_n

in

兼容性测试按键

rx_in0

in

数据输入信号

rx_in1

in

数据输入信号

rx_in2

in

数据输入信号

rx_in3

in

数据输入信号

alive_led

out

PCIE工作正常led显示

gen2_led

out

识别gen1或gen2使用led显示

lane_active_led[3:

0]

out

显示4条lane的状态

tx_out0

out

数据输出信号

tx_out1

out

数据输出信号

tx_out2

out

数据输出信号

tx_out3

out

数据输出信号

3PCIExpress中模块(功能)的原理与实现

3.1应用层模块

3.1.1模块介绍

该模块主要包括收发端口转换、收发缓存、链式DMA和RC_slave数据传输功能、MSI中断。

本模块实现端点设备的存储空间,通过该空间和系统主存储器交换数据从而实现数据传输。

3.1.2结构、算法(或原理)和实现

a)收发端口转换模块

Avalon-ST接口时序是数据流传输,将TLP的头标和数据均作为数据传输,本模块将接收信号转换成时序相对简单的data/descriptor接口,发送是其逆过程。

b)收发缓冲模块

本模块主要监控数据缓冲区可用空间大小,防止IP核发送数据过多,接收缓冲区溢出丢失数据。

当接收缓冲区空间较小时,应用层暂不发送读请求信号,避免接收缓冲区溢出。

为实现其功能,本模块主要例化一个10bit*32的双口RAM。

当应用层发送一个存储器读请求TLP时,提取TLP中Tag字段作为地址,将TLP中Length字段作为数据存入双口RAM中。

当接收到对应Tag带数据的TLP时,读取双口RAM中Tag值计算TLP所需缓冲空间大小,根据剩余缓冲区大小输出通知应用层,让其决定是否发送请求信号接收数据传输。

发送过程处理类似,不再赘述。

c)MSI中断缓冲模块

由于发送和接收数据时会对数据进行接口转换和缓冲,具有一定延时,在数据未完成传输就通知IP核产生中断会造成CPU误认为数据传输已经完成,且IP核处理数据也需要一定时间,所以要对中断信号缓冲处理。

d)数据传输模块

PCIE的数据传输主要通过Rc_slave或者DMA模块两种方式。

1)Rc_slave模块

本模块主要完成普通数据的传输,可在CPU的控制下直接访问BAR存储空间。

由于DMA模块不能访问存储控制状态信息的BAR空间,所以每次DMA传输之前CPU必须通过本模块对DMA寄存器进行设置和启动。

本模块主要有两个子模块完成,rxtx_mem_intf主要负责构建data/descriptor接口,若访问的是BAR0/1存储空间,则完成存储器读写请求;若访问的是BAR2/3存储空间,则交给另一模块reg_acess处理,由这个模块读写BAR2/3存储空间的信息,BAR2/3中主要是DMA控制状态寄存器中的内容,通过这个模块译码开始启动DMA。

控制状态寄存器中信息如下表所示:

2)DMA模块

本模块实现DMA传输功能,DMA可在没有CPU干预下一次执行多个DMA操作,提高传输效率。

DMA通过描述符表完成,主机系统在住存储器中开辟一块区域存储DMA的描述符表,通过Rc_slave模块控制DMA从主存储器中读取DMA描述符表并开始DMA操作,完成后通过MSI中断通知主机数据传输完成。

描述符表的内容如下表所示:

若传输的数据在一个双口RAM中存储,根据功能的不同需求,可将状态控制寄存器、DMA读数据存储和DMA写数据存储都用双口RAM实现,提高效率。

具体的改动也在应用模块中完成。

3.1.3参数和接口

一些端口的说明参看IPCompilerforPCIExpressUserGuide中AppendixB。

3.2配置信号采样模块

3.2.1模块介绍

本模块通过与IP核的配置信号线相连,将IP核配置空间的特定寄存器内容读出传送至应用层模块使用。

IP核的配置空间为4KB,为了方便应用层设计,将IP核中常用的寄存器组成一个特定的配置空间,通过tl_cfg_sts信号引出至应用层。

该信号的内容如下如所示:

3.2.2参数和接口

3.3PCIE硬核模块

3.3.1模块介绍

本模块实现PCIE数据传输的基本功能,实现了事务层、数据链路层和物理层的功能,以硬核的形式存在。

本模块按照PCIE协议实现事务层、数据链路层和物理层的功能,具体实现过程不再赘述。

与应用层的信息都是以TLP的形式进行交流,TLP的一种头标格式如下图所示:

3.3.2参数和接口

一些端口的说明参看IPCompilerforPCIExpressUserGuide中Table5–2。

3.4LMI配置模块

3.4.1模块介绍

当PCIE设备检测到一个TLP传送错误时,如果该错误寄存器未屏蔽,PCIEIP核会向跟复合体报告错误,同时将包头更新为错误的TLP头标,本模块由一个状态机实现。

3.4.2结构、算法(或原理)和实现

内容2的结构、算法(或原理)和实现,参考现有的文档,把内容讲清楚。

3.4.3参数和接口

3.5重新配置时钟模块

3.5.1模块介绍

本模块主要通过锁相环实现改变时钟频率的功能,长生不同的时钟供IP核和应用层使用。

3.5.2参数和接口

3.6兼容性测试模块

3.6.1模块介绍

当检测到兼容性测试按键按下时,开始执行兼容性模式,检查是否符合基板(ComplianceBaseBoard)

3.6.2参数和接口

Welcome!

!

!

欢迎您的下载,

资料仅供参考!