实验五Verilog设计组合电路.docx

《实验五Verilog设计组合电路.docx》由会员分享,可在线阅读,更多相关《实验五Verilog设计组合电路.docx(19页珍藏版)》请在冰豆网上搜索。

实验五Verilog设计组合电路

实验五Verilog设计组合电路

一、实验目的

1、学习非门、与门、与非门、或门、或非门、异或门和异或非门的VerilogHDL描述;

2、掌握基本组合逻辑电路的实现方法;

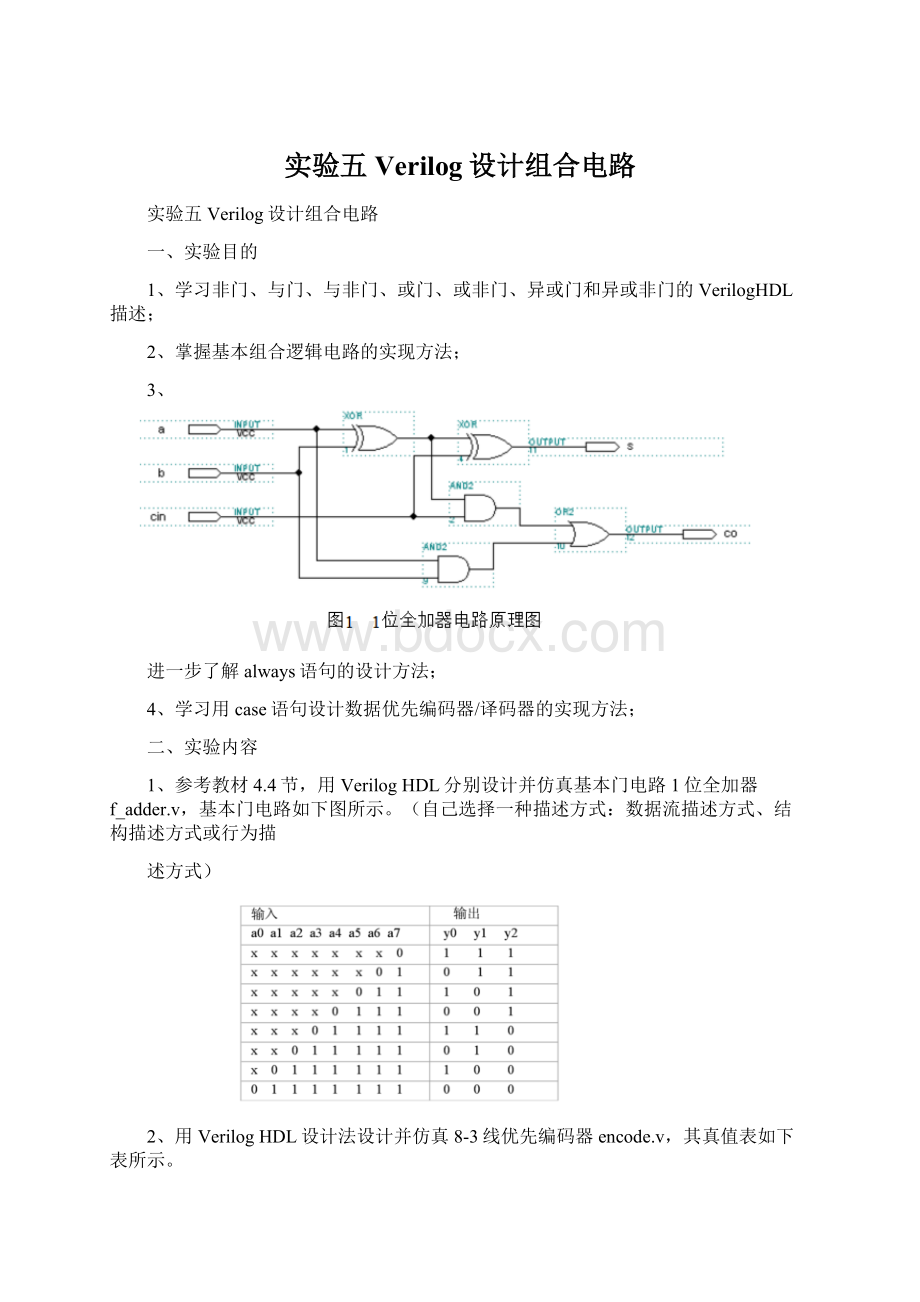

3、

进一步了解always语句的设计方法;

4、学习用case语句设计数据优先编码器/译码器的实现方法;

二、实验内容

1、参考教材4.4节,用Verilog HDL分别设计并仿真基本门电路1位全加器f_adder.v,基本门电路如下图所示。

(自己选择一种描述方式:

数据流描述方式、结构描述方式或行为描

述方式)

2、用Verilog HDL设计法设计并仿真8-3线优先编码器encode.v,其真值表如下表所示。

3、用Verilog语言编写3-8译码器的程序,符号如图所示,其中g1,g2a,g2b是使能控制输入端,当g1为高电平,g2a,g2b为低电平时,译码器工作,其他状态时,译码器被禁止工作,全部输出均为无效电平(高电平‘1’)。

当CBA=000时,Y0N=0,其余为1;当CBA=001时,Y1N=0,其余为1;依此类推,文件命名为decoder3_8.v。

(选做)

三、实验步骤:

第一个实验:

1、打开QuartusII,新建一个工程f_adderyjq

2、新建一个Verilog HDL文件

3、输入程序(数据流方式):

modulef_adder1(a,b,cin,s,co);

inputa,b,cin;

outputs,co;

assigns=(a^b)^cin;

assignco=(a&b)|(cin&(a^b));

endmodule

4、设置顶层实体名(点settings>general>下拉选)

5、编译

6、新建一个Verilog HDL文件输入文件f_adder2.v

7、输入程序(结构描述方式):

modulef_adder2(a,b,cin,s,co);

inputa,b,cin;

outputs,co;

wires1,s2,s3;

xor(s1,a,b);

and(s2,s1,cin);

and(s3,a,b);

xor(s,cin,s1);

or(co,s2,s3);

endmodule

8、设置顶层实体名(点settings>general>下拉选)

9、编译

10、新建一个Verilog HDL文件输入文件f_adder3.v

11、输入程序(行为描述方式):

modulef_adder3(a,b,cin,s,co);

inputa,b,cin;

outputs,co;

regs,co;

always@({a,b,cin})

begin

case({a,b,cin})

'b000:

s=0;

'b001:

s=1;

'b010:

s=1;

'b011:

s=0;

'b100:

s=1;

'b101:

s=0;

'b110:

s=0;

'b111:

s=1;

endcase

case({a,b,cin})

'b000:

co=0;

'b001:

co=0;

'b010:

co=0;

'b011:

co=1;

'b100:

co=0;

'b101:

co=1;

'b110:

co=1;

'b111:

co=1;

endcase

end

endmodule

12、设置顶层实体名(点settings>general>下拉选)

13、编译

14、执行file>Create/Update>CreateSymbolFilesforCurrentFlie为VHDI设计文件生成原件符号

15、建立波形文件

8、导入引脚

9、仿真结果如下:

总结根据电路图分析可知:

abc

sco

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

与仿真的波形相符。

第二个实验:

1、打开QuartusII,新建一个工程encodeyjq

2、新建一个Verilog HDL文件输入文件encodeyjq.v

3、输入程序

moduleencode(y,a);

input[7:

0]a;

output[2:

0]y;

reg[2:

0]y;

always@(a)

begin

if(~a[7])y='b111;

elseif(~a[6])y='b110;

elseif(~a[5])y='b101;

elseif(~a[4])y='b100;

elseif(~a[3])y='b011;

elseif(~a[2])y='b010;

elseif(~a[1])y='b001;

elseif(~a[0])y='b000;

end

endmodule

4、设置顶层文件(点settings>general>下拉选)

5、编译

6、执行file>Create/Update>CreateSymbolFilesforCurrentFlie为VHDI设计文件生成原件符号

7、建立波形文件

8、导入引脚

9、仿真结果如下:

总结:

结果与图片相同,仿真正确。

第三个实验

1、打开QuartusII,新建一个工程decoderyjq

2、新建一个Verilog HDL文件输入文件decoderyjq.v

3、输入程序

moduledecoder(g1,g2a,g2b,A,B,C,y);

inputA,B,C,g1,g2a,g2b;

output[7:

0]y;

reg[7:

0]y;

always@(g1org2aorg2borAorBorC)

begin

if(g1!

=1|g2a!

=0|g2b!

=0)y='b11111111;

else

begin

case({C,B,A})

'b000:

y<='b11111110;

'b001:

y<='b11111101;

'b010:

y<='b11111011;

'b011:

y<='b11110111;

'b100:

y<='b11101111;

'b101:

y<='b11011111;

'b110:

y<='b10111111;

'b111:

y<='b01111111;

endcase

end

end

endmodule

4、设置顶层文件(点settings>general>下拉选)

5、编译

6、执行file>Create/Update>CreateSymbolFilesforCurrentFlie为VHDI设计文件生成原件符号

7、建立波形文件

8、导入引脚

9、仿真

仿真结果与实验要求相同,故仿真正确。