Stm32时钟分析.pdf

《Stm32时钟分析.pdf》由会员分享,可在线阅读,更多相关《Stm32时钟分析.pdf(11页珍藏版)》请在冰豆网上搜索。

Stm32Stm32Stm32Stm32时钟分析时钟分析时钟分析时钟分析来源:

http:

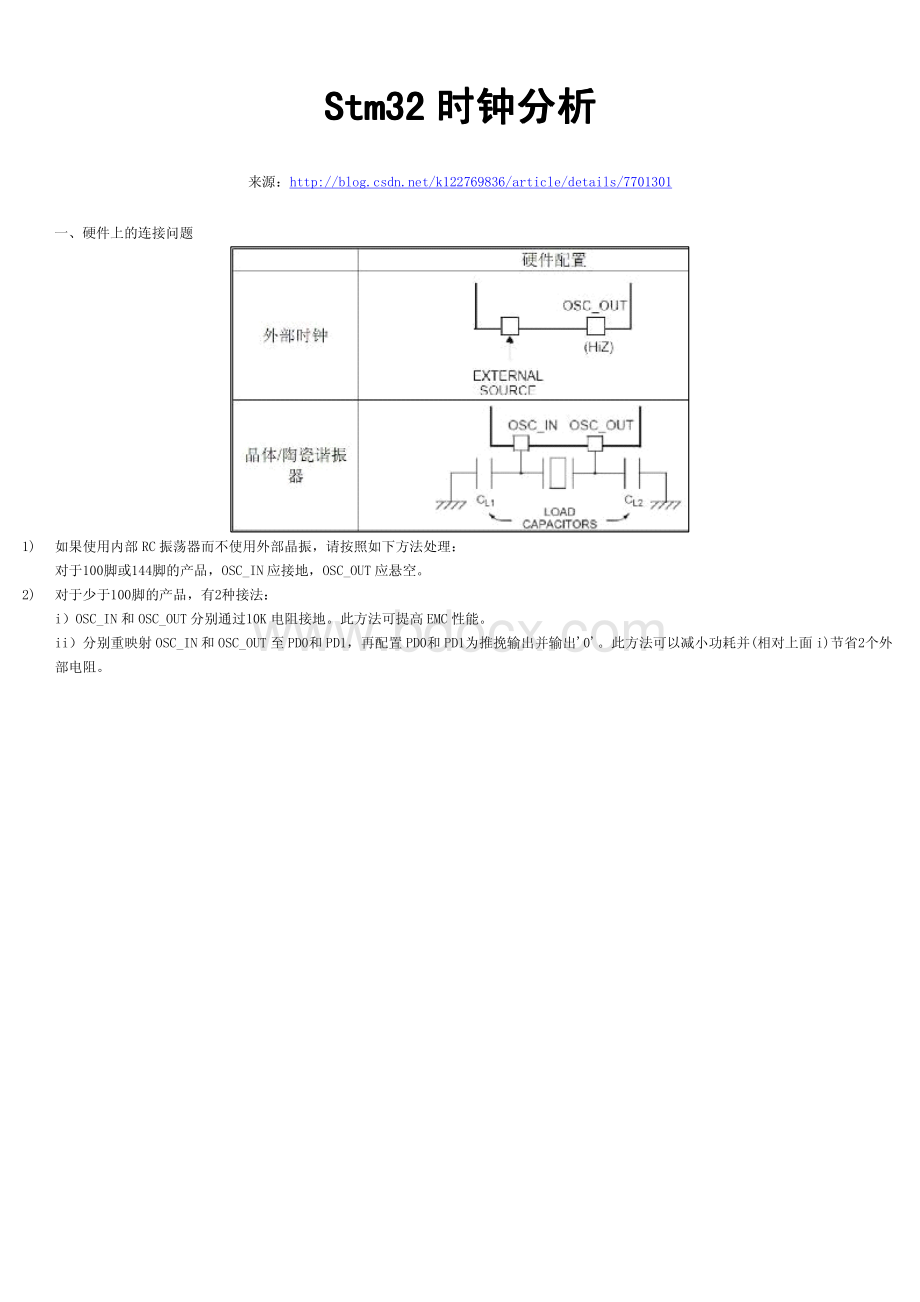

/RC振荡器而不使用外部晶振,请按照如下方法处理:

对于100脚或144脚的产品,OSC_IN应接地,OSC_OUT应悬空。

2)对于少于100脚的产品,有2种接法:

i)OSC_IN和OSC_OUT分别通过10K电阻接地。

此方法可提高EMC性能。

ii)分别重映射OSC_IN和OSC_OUT至PD0和PD1,再配置PD0和PD1为推挽输出并输出0。

此方法可以减小功耗并(相对上面i)节省2个外部电阻。

对上图的分析如下对上图的分析如下:

重要的时钟:

PLLCLK,SYSCLK,HCKL,PCLK1,PCLK2之间的关系要弄清楚:

1、HSI:

高速内部时钟信号stm32单片机内带的时钟(8M频率)(精度较差)2、HSE:

高速外部时钟信号精度高来源:

(1)HSE外部晶体/陶瓷谐振器(晶振)

(2)HSE用户外部时钟3、LSE:

低速外部晶体32.768kHz主要提供一个精确的时钟源一般作为RTC时钟使用在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。

、HSI是高速内部时钟,RC振荡器,频率为8MHz。

、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz16MHz。

、LSI是低速内部时钟,RC振荡器,频率为40kHz。

、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

、PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。

倍频可选择为216倍,但是其输出频率最大不得超过72MHz。

其中40kHz的LSI供独立看门狗IWDG使用,另外它还可以被选择为实时时钟RTC的时钟源。

另外,实时时钟RTC的时钟源还可以选择LSE,或者是HSE的128分频。

RTC的时钟源通过RTCSEL1:

0来选择。

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。

该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,PLL必须使能,并且时钟频率配置为48MHz或72MHz。

另外,STM32还可以选择一个时钟信号输出到MCO脚(PA8)上,可以选择为PLL输出的2分频、HSI、HSE、或者系统时钟。

系统时钟SYSCLK,它是供STM32中绝大部分部件工作的时钟源。

系统时钟可选择为PLL输出、HSI或者HSE。

系统时钟最大频率为72MHz,它通过AHB分频器分频后送给各模块使用,AHB分频器可选择1、2、4、8、16、64、128、256、512分频。

其中AHB分频器输出的时钟送给5大模块使用:

、送给AHB总线、内核、内存和DMA使用的HCLK时钟。

、通过8分频后送给Cortex的系统定时器时钟(滴答定时器)。

、直接送给Cortex的空闲运行时钟FCLK。

、送给APB1分频器。

APB1分频器可选择1、2、4、8、16分频,其输出一路供APB1外设使用(PCLK1,最大频率36MHz),另一路送给定时器(Timer)2、3、4倍频器使用。

该倍频器可选择1或者2倍频,时钟输出供定时器2、3、4使用。

、送给APB2分频器。

APB2分频器可选择1、2、4、8、16分频,其输出一路供APB2外设使用(PCLK2,最大频率72MHz),另一路送给定时器(Timer)1倍频器使用。

该倍频器可选择1或者2倍频,时钟输出供定时器1使用。

另外,APB2分频器还有一路输出供ADC分频器使用,分频后送给ADC模块使用。

ADC分频器可选择为2、4、6、8分频。

在以上的时钟输出中,有很多是带使能控制的,例如AHB总线时钟、内核时钟、各种APB1外设、APB2外设等等。

当需要使用某模块时,记得一定要先使能对应的时钟。

需要注意的是定时器的倍频器,当APB的分频为1时,它的倍频值为1,否则它的倍频值就为2。

连接在APB1(低速外设)上的设备有:

电源接口、备份接口、CAN、USB、I2C1、I2C2、UART2、UART3、SPI2、窗口看门狗、Timer2、Timer3、Timer4。

注意USB模块虽然需要一个单独的48MHz时钟信号,但它应该不是供USB模块工作的时钟,而只是提供给串行接口引擎(SIE)使用的时钟。

USB模块工作的时钟应该是由APB1提供的。

连接在APB2(高速外设)上的设备有:

UART1、SPI1、Timer1、ADC1、ADC2、所有普通IO口(PAPE)、第二功能IO口。

涉及的寄存器:

RCC寄存器结构,RCC_TypeDeff,在文件“stm32f10x_map.h”中定义如下:

typedefstructvu32CR;/HSI,HSE,CSS,PLL等的使能vu32CFGR;/PLL等的时钟源选择以及分频系数设定vu32CIR;/清除/使能时钟就绪中断vu32APB2RSTR;/APB2线上外设复位寄存器vu32APB1RSTR;/APB1线上外设复位寄存器vu32AHBENR;/DMA,SDIO等时钟使能vu32APB2ENR;/APB2线上外设时钟使能vu32APB1ENR;/APB1线上外设时钟使能vu32BDCR;/备份域控制寄存器vu32CSR;RCC_TypeDef;【注意:

typedefvolatileunsignedlongvu32】这些寄存器的具体定义和使用方式参见芯片手册,因为C语言的开发可以不和他们直接打交道,当然如果能够加以理解和记忆,无疑是百利而无一害。

如果外接晶振为8Mhz,最高工作频率为72Mhz,显然需要用PLL倍频9倍,这些设置都需要在初始化阶段完成。

为了方便说明,以例程的RCC设置函数,并用中文注释的形式加以说明:

staticvoidRCC_Config(void)RCC_DeInit();RCC_HSEConfig(RCC_HSE_ON);HSEStartUpStatus=RCC_WaitForHSEStartUp();if(HSEStartUpStatus=SUCCESS)FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);FLASH_SetLatency(FLASH_Latency_2);RCC_HCLKConfig(RCC_SYSCLK_Div1);RCC_PCLK2Config(RCC_HCLK_Div1);RCC_PCLK1Config(RCC_HCLK_Div2);RCC_ADCCLKConfig(RCC_PCLK2_Div6);/上面这句例程中缺失了,但却很关键RCC_PLLConfig(RCC_PLLSource_HSE_Div1,RCC_PLLMul_9);RCC_PLLCmd(ENABLE);while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY)=RESET);RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);while(RCC_GetSYSCLKSource()!

=0x08);/使能外围接口总线时钟,注意各外设的隶属情况,不同芯片的分配不同,到时候查手册就可以RCC_AHBPeriphClockCmd(RCC_AHBPeriph_FSMC,ENABLE);RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOD|RCC_APB2Periph_GPIOE|RCC_APB2Periph_GPIOF|RCC_APB2Periph_GPIOG|RCC_APB2Periph_AFIO,ENABLE);由上述程序可以看出系统时钟的设定是比较复杂的,外设越多,需要考虑的因素就越多。

同时这种设定也是有规律可循的,设定参数也是有顺序规范的,这是应用中应当注意的,例如PLL的设定需要在使能之前,一旦PLL使能后参数不可更改。

经过此番设置后,对于外置8Mhz晶振的情况下,系统时钟为72Mhz,高速总线和低速总线2都为72Mhz,低速总线1为36Mhz,ADC时钟为12Mhz,USB时钟经过1.5分频设置就可以实现48Mhz的数据传输。

一般性的时钟设置需要先考虑系统时钟的来源,是内部RC还是外部晶振还是外部的振荡器,是否需要PLL。

然后考虑内部总线和外部总线,最后考虑外设的时钟信号。

遵从先倍频作为CPU时钟,然后在由内向外分频,下级迁就上级的原则。

时钟控制寄存器(RCC_CR)31262524232019181716保留PLLRDYPLLON保留CSSONHSEBYPHSERDYHSEONeg:

RCC-CR|=0x00010000;/外部高速时钟使能HSEONRCC-CR|=0x01000000;/使能PLLONRCC-CR25;/等待PLL锁定时钟配置寄存器(RCC_CFGR)31:

2726:

24232221:

181716保留MCO2:

0保留USBPREPLLMUL3:

0PLLXTPREPLLSRC15:

1413:

1110:

87:

43:

21:

0ADCPRE1:

0PPRE22:

0PPRE12:

0HPRE3:

0SWS1:

0SW1:

0位26:

24MCO:

微控制器时钟输出(Microcontrollerclockoutput)由软件置1或清零。

0xx:

没有时钟输出;100:

系统时钟(SYSCLK)输出;101:

内部RC振荡器时钟(HSI)输出;110:

外部振荡器时钟(HSE)输出;111:

PLL时钟2分频后输出。

位22USBPRE:

USB预分频(USBprescaler)由软件置1或清0来产生48MHz的USB时钟。

在RCC_APB1ENR寄存器中使能USB时钟之前,必须保证该位已经有效。

如果USB时钟被使能,该位不能被清零。

0:

PLL时钟1.5倍分频作为USB时钟1:

PLL时钟直接作为USB时钟位21:

18PLLMUL:

PLL倍频系数(PLLmultiplicationfactor)由软件设置来确定PLL倍频系数。

只有在PLL关闭的情况下才可被写入。

注意:

PLL的输出频率不能超过72MHz0000:

PLL2倍频输出1000:

PLL10倍频输出0001:

PLL3倍频输出1001:

PLL11倍频输出0010:

PLL4倍频输出1010:

PLL12倍频输出0011:

PLL5倍频输出1011:

PLL13倍频输出0100:

PLL6倍频输出1100:

PLL14倍频输出0101:

PLL7倍频输出1101:

PLL15倍频输出0110:

PLL8倍频输出1110:

PLL16倍频输出0111:

PLL9倍频输出1111:

PLL16倍频输出位17PLLXTPRE:

HSE分频器作为PLL输入(HSEdividerforPLLentry)由软件置1或清0来分频HSE后作为PLL输入时钟。

只能在关闭PLL时才能写入此位。

0:

HSE不分频1:

HSE2分频位16PLLSRC:

PLL输入时钟源(PLLentryclocksource)由软件置1或清0来选择PLL输入时钟源。

只能在关闭PLL时才能写入此位。

0:

HSI振荡器时钟经2分频后作为PLL输入时钟1:

HSE时钟作为PLL输入时钟。

位15:

14ADCPRE1:

0:

ADC预分频(ADCprescaler)由软件置1或清0来确定ADC时钟频率00:

PCLK22分频后作为ADC时钟01:

PCLK24分频后作为ADC时钟10:

PCLK26分频后作为ADC时钟11:

PCLK28分频后作为ADC时钟位13:

11PPRE22:

0