芯片CD4051数据资料.pdf

《芯片CD4051数据资料.pdf》由会员分享,可在线阅读,更多相关《芯片CD4051数据资料.pdf(21页珍藏版)》请在冰豆网上搜索。

1DatasheetacquiredfromHarrisSemiconductorSCHS047GCAUTION:

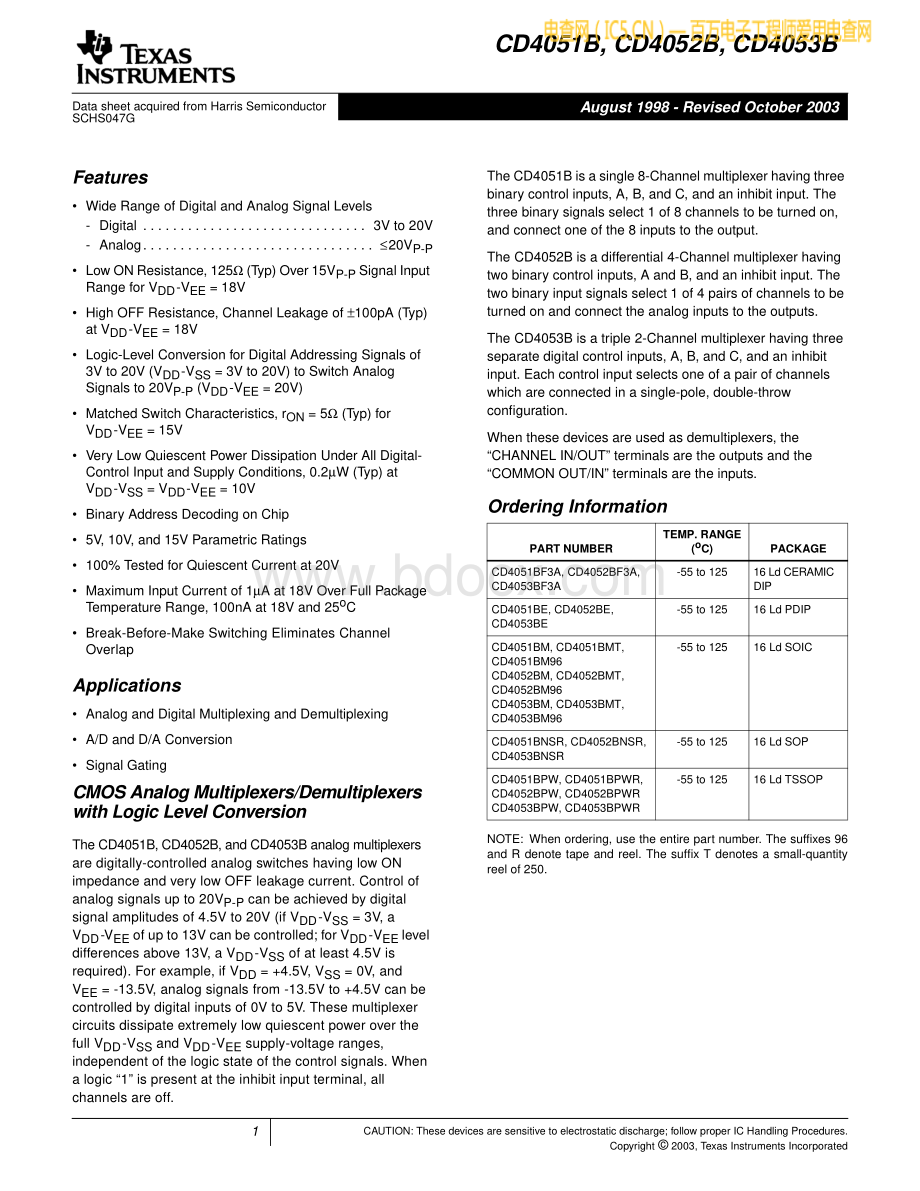

Thesedevicesaresensitivetoelectrostaticdischarge;followproperICHandlingProcedures.Copyright2003,TexasInstrumentsIncorporatedCD4051B,CD4052B,CD4053BFeaturesWideRangeofDigitalandAnalogSignalLevels-Digital.3Vto20V-Analog.20VP-PLowONResistance,125(Typ)Over15VP-PSignalInputRangeforVDD-VEE=18VHighOFFResistance,ChannelLeakageof100pA(Typ)atVDD-VEE=18VLogic-LevelConversionforDigitalAddressingSignalsof3Vto20V(VDD-VSS=3Vto20V)toSwitchAnalogSignalsto20VP-P(VDD-VEE=20V)MatchedSwitchCharacteristics,rON=5(Typ)forVDD-VEE=15VVeryLowQuiescentPowerDissipationUnderAllDigital-ControlInputandSupplyConditions,0.2W(Typ)atVDD-VSS=VDD-VEE=10VBinaryAddressDecodingonChip5V,10V,and15VParametricRatings100%TestedforQuiescentCurrentat20VMaximumInputCurrentof1Aat18VOverFullPackageTemperatureRange,100nAat18Vand25oCBreak-Before-MakeSwitchingEliminatesChannelOverlapApplicationsAnalogandDigitalMultiplexingandDemultiplexingA/DandD/AConversionSignalGatingCMOSAnalogMultiplexers/DemultiplexerswithLogicLevelConversionTheCD4051B,CD4052B,andCD4053Banalogmultiplexersaredigitally-controlledanalogswitcheshavinglowONimpedanceandverylowOFFleakagecurrent.Controlofanalogsignalsupto20VP-Pcanbeachievedbydigitalsignalamplitudesof4.5Vto20V(ifVDD-VSS=3V,aVDD-VEEofupto13Vcanbecontrolled;forVDD-VEEleveldifferencesabove13V,aVDD-VSSofatleast4.5Visrequired).Forexample,ifVDD=+4.5V,VSS=0V,andVEE=-13.5V,analogsignalsfrom-13.5Vto+4.5Vcanbecontrolledbydigitalinputsof0Vto5V.ThesemultiplexercircuitsdissipateextremelylowquiescentpoweroverthefullVDD-VSSandVDD-VEEsupply-voltageranges,independentofthelogicstateofthecontrolsignals.Whenalogic“1”ispresentattheinhibitinputterminal,allchannelsareoff.TheCD4051Bisasingle8-Channelmultiplexerhavingthreebinarycontrolinputs,A,B,andC,andaninhibitinput.Thethreebinarysignalsselect1of8channelstobeturnedon,andconnectoneofthe8inputstotheoutput.TheCD4052Bisadifferential4-Channelmultiplexerhavingtwobinarycontrolinputs,AandB,andaninhibitinput.Thetwobinaryinputsignalsselect1of4pairsofchannelstobeturnedonandconnecttheanaloginputstotheoutputs.TheCD4053Bisatriple2-Channelmultiplexerhavingthreeseparatedigitalcontrolinputs,A,B,andC,andaninhibitinput.Eachcontrolinputselectsoneofapairofchannelswhichareconnectedinasingle-pole,double-throwconfiguration.Whenthesedevicesareusedasdemultiplexers,the“CHANNELIN/OUT”terminalsaretheoutputsandthe“COMMONOUT/IN”terminalsaretheinputs.NOTE:

Whenordering,usetheentirepartnumber.Thesuffixes96andRdenotetapeandreel.ThesuffixTdenotesasmall-quantityreelof250.OrderingInformationPARTNUMBERTEMP.RANGE(oC)PACKAGECD4051BF3A,CD4052BF3A,CD4053BF3A-55to12516LdCERAMICDIPCD4051BE,CD4052BE,CD4053BE-55to12516LdPDIPCD4051BM,CD4051BMT,CD4051BM96CD4052BM,CD4052BMT,CD4052BM96CD4053BM,CD4053BMT,CD4053BM96-55to12516LdSOICCD4051BNSR,CD4052BNSR,CD4053BNSR-55to12516LdSOPCD4051BPW,CD4051BPWR,CD4052BPW,CD4052BPWRCD4053BPW,CD4053BPWR-55to12516LdTSSOPAugust1998-RevisedOctober2003/Title(CD4051B,CD4052B,CD4053B)/Sub-ject(CMOSAnalogMulti-plex-ers/Demultiplex-erswithLogicLevelConver-sion)/Author()/Key-words(HarrisSemi-conduc-tor,CD40002PinoutsCD4051B(PDIP,CDIP,SOIC,SOP,TSSOP)TOPVIEWCD4052B(PDIP,CDIP,SOP,TSSOP)TOPVIEWCD4053B(PDIP,CDIP,SOP,TSSOP)TOPVIEW1415169131211101234576846COMOUT/IN75INHVSSVEEVDD103ABC2CHANNELSIN/OUTCHANNELSIN/OUTCHANNELSIN/OUT1415169131211101234576802COMMON“Y”OUT/IN31INHVSSVEEVDD1COMMON“X”OUT/IN03AB2YCHANNELSIN/OUTYCHANNELSIN/OUTXCHANNELSIN/OUTXCHANNELSIN/OUT14151691312111012345768bybxcyOUT/INCXORCYIN/OUTCXINHVSSVEEVDDOUT/INaxORayayaxABCOUT/INbxORbyIN/OUTIN/OUTFunctionalBlockDiagramsCD4051B111096ABCINH134251121514TGTGTGTGTGTGTGTG3COMMONOUT/IN01234567BINARYTO1OF8DECODERWITHINHIBITLOGICLEVELCONVERSION87VSSVEE16VDDCHANNELIN/OUTAllinputsareprotectedbystandardCMOSprotectionnetwork.CD4051B,CD4052B,CD4053B3CD4052BCD4053BFunctionalBlockDiagrams(Continued)1211151401233210XCHANNELSIN/OUTYCHANNELSIN/OUTBINARYTO1OF4DECODERWITHINHIBIT133COMMONYOUT/INCOMMONXOUT/IN78166910ABINHVSSVEEVDDTGTGTGTGTGTGTGTG4251LOGICLEVELCONVERSION111096ABCINH12351213TGTGTGTGTGTG4COMMONOUT/INaxaybxbycxcy87VSSVEE16VDDIN/OUT1514BINARYTO1OF2DECODERSWITHINHIBITLOGICLEVELCONVERSIONVDDAllinputsareprotectedbystandardCMOSprotectionnetwork.COMMONOUT/INCOMMONOUT/INaxORaybxORbycxORcyCD4051B,CD4052B,CD4053B4TRUTHTABLESINPUTSTATES“ON”CHANNEL(S)INHIBITCBACD4051B00000000110010200113010040101501106011171XXXNoneCD4052BINHIBITBA0000x,0y0011x,1y0102x,2y0113x,3y1XXNoneCD4053BINHIBITAORBORC00axorbxorcx01ayorbyorcy1XNoneX=DontCareCD4051B,CD4052B,CD4053B5AbsoluteMaximumRatingsThermalInfo