Stm32寄存器列表.pdf

《Stm32寄存器列表.pdf》由会员分享,可在线阅读,更多相关《Stm32寄存器列表.pdf(105页珍藏版)》请在冰豆网上搜索。

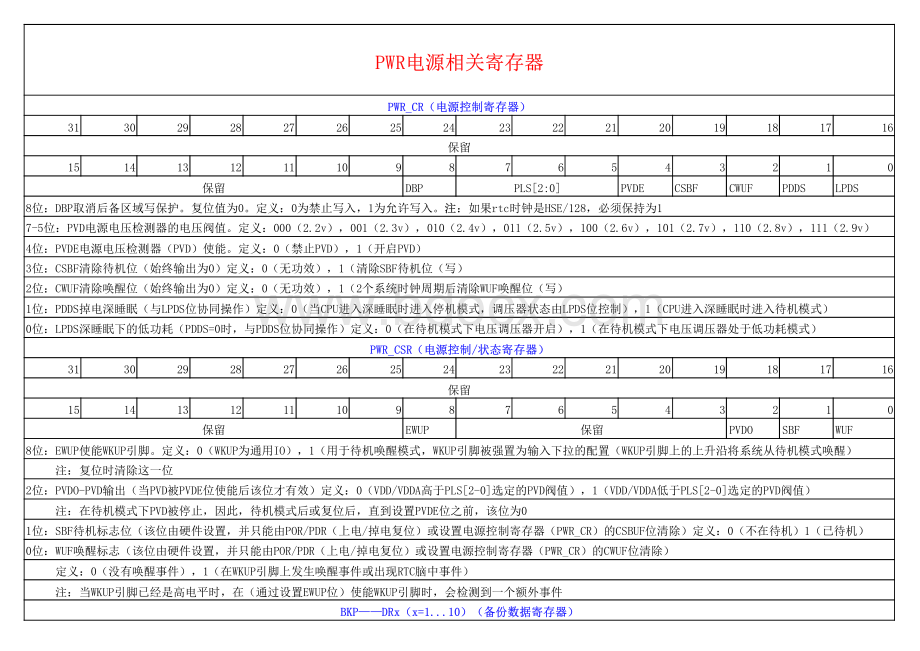

PWRPWR电源相关寄存器电源相关寄存器PWR_CRPWR_CR(电源控制寄存器电源控制寄存器)31302928272625242322212019181716保留1514131211109876543210保留DBPPLS2:

0PVDECSBFCWUFPDDSLPDS8位:

DBP取消后备区域写保护。

复位值为0。

定义:

0为禁止写入,1为允许写入。

注注:

如果rtc时钟是HSE/128,必须保持为17-5位:

PVD电源电压检测器的电压阀值。

定义:

000(2.2v),001(2.3v),010(2.4v),011(2.5v),100(2.6v),101(2.7v),110(2.8v),111(2.9v)4位:

PVDE电源电压检测器(PVD)使能。

定义:

0(禁止PVD),1(开启PVD)3位:

CSBF清除待机位(始终输出为0)定义:

0(无功效),1(清除SBF待机位(写)2位:

CWUF清除唤醒位(始终输出为0)定义:

0(无功效),1(2个系统时钟周期后清除WUF唤醒位(写)1位:

PDDS掉电深睡眠(与LPDS位协同操作)定义:

0(当CPU进入深睡眠时进入停机模式,调压器状态由LPDS位控制),1(CPU进入深睡眠时进入待机模式)0位:

LPDS深睡眠下的低功耗(PDDS=0时,与PDDS位协同操作)定义:

0(在待机模式下电压调压器开启),1(在待机模式下电压调压器处于低功耗模式)PWR_CSRPWR_CSR(电源控制电源控制/状态寄存器状态寄存器)31302928272625242322212019181716保留1514131211109876543210保留EWUP保留PVDOSBFWUF8位:

EWUP使能WKUP引脚。

定义:

0(WKUP为通用IO),1(用于待机唤醒模式,WKUP引脚被强置为输入下拉的配置(WKUP引脚上的上升沿将系统从待机模式唤醒)注:

复位时清除这一位2位:

PVDO-PVD输出(当PVD被PVDE位使能后该位才有效)定义:

0(VDD/VDDA高于PLS2-0选定的PVD阀值),1(VDD/VDDA低于PLS2-0选定的PVD阀值)注:

在待机模式下PVD被停止,因此,待机模式后或复位后,直到设置PVDE位之前,该位为01位:

SBF待机标志位(该位由硬件设置,并只能由POR/PDR(上电/掉电复位)或设置电源控制寄存器(PWR_CR)的CSBUF位清除)定义:

0(不在待机)1(已待机)0位:

WUF唤醒标志(该位由硬件设置,并只能由POR/PDR(上电/掉电复位)或设置电源控制寄存器(PWR_CR)的CWUF位清除)定义:

0(没有唤醒事件),1(在WKUP引脚上发生唤醒事件或出现RTC脑中事件)注:

当WKUP引脚已经是高电平时,在(通过设置EWUP位)使能WKUP引脚时,会检测到一个额外事件BKPBKPDRxDRx(x=1.10x=1.10)()(备份数据寄存器备份数据寄存器)151413121110987654321015-0位:

备份数据由用户来写数据。

注:

BKPDRx寄存器不会被系统复位,电源复位,待机唤醒所复位它可以由备份域复位来复位或(如果入侵检测引脚TAMPER功能被开启时)由浸入引脚事件复位BKP_RTCCRBKP_RTCCR(RTCRTC时钟校准寄存器时钟校准寄存器)1514131211109876543210保留ASOSASOECCOCAL6:

09位:

ASOS闹钟或秒输出(当设置ASOE位,ASOS位可用于选择在TAMPER引脚上输出的是RTC秒脉冲还是闹钟脉冲信号)定义:

0(输出RTC闹钟脉冲),1(输出秒脉冲)注:

8位:

ASOE允许输出闹钟或秒脉冲(根据ASOS位的置位,该位允许RTC闹钟或秒脉冲输出到TAMPER引脚。

脉冲宽度为1个RTC时钟周期。

置位时不能开启TAMPER功能)7位:

CCO校准时钟输出。

定义:

0(无影响),1(此位置1可在侵入检引脚输出经64分频后的RTC时钟。

当CCO位置1时,必须关闭侵入检测)注:

vdd断电,该位清除6-0位:

CAL校准值。

表示在每2的20次方个时钟脉冲内将有多少个脉冲被跳过。

这可用来对RTC进行校准,以1000000/(2的20次方比例减慢时钟)可用被减慢0-121ppmBKP_CR(BKP_CR(备份控制寄存器备份控制寄存器)1514131211109876543210保留TPALTPE1位:

TPAL侵入检测TAMPER引脚有效电平。

定义:

0(检测TAMPER脚高电平清除备份数据)1(检测TAMPER脚低电平清除备份数据)2位:

TPE启动入侵检测TAMPER引脚。

定义:

0(TAMPER脚为普通IO),1(开启检测)注:

TPAL、TPE同时置为可用,但同时清零则会出问题。

所以推荐在TPE为0时才改变TPAL位状态。

BKP_CSR(BKP_CSR(备份控制备份控制/状态寄存器状态寄存器)1514131211109876543210保留TIFTEF保留TPIECTICTE9位:

TIF侵入中断标志(当检测有侵入事件且TPIE为1时,此为硬件置1,通过向CTI位写1来清除标志位(同时也清除中断)。

如果TPIE被清除,此位也会被清除。

定义:

0(无侵入),1(检测到侵入)注:

仅当系统复位或由待机模式唤醒后才复位该位8位:

TEF侵入事件标志(当检测到侵入事件时此位由硬件置1。

通过向CTE位写1可清除此标志位)定义:

0(无侵入事件),1(有侵入事件)注:

侵入事件会复位所有的BKP_DRx寄存器。

只要TEF为1,所有的BKP_DRx寄存器就一直保持复位状态。

当此位被置1时,若对BKP_DRx写操作,则不会保存。

2位:

TPIE:

允许侵入TAMPER引脚中断。

定义0(禁止侵入检测中断),1(允许(BKP_CR寄存器TPE位也必须置1)注:

1、侵入检测无法将系统内核从低功耗模式唤醒,2、仅当系统复位或由待机模式唤醒后才复位该位1位:

CTI清除侵入检测中断(只能写入,读出值为0)定义:

0(无效)1(清除侵入检测中断和TIF侵入检测中断标志)0位:

CTE清除侵入检测事件(只能写入,读出值为0)定义:

0(无效)1(清除TEF侵入检测事件标志(并复位侵入检测器)RCCRCC时钟相关寄存器时钟相关寄存器RCC_CR(RCC_CR(时钟控制寄存器时钟控制寄存器)31302928272625242322212019181716保留PLLRDYPLLON保留CSSONHSEBYPHSERDYHSEON1514131211109876543210HSICAL7:

0HSITRIM4:

0保留HSIRDYHSION25位:

PLLRDY-PLL时钟就绪标志(PLL锁定后由硬件置1)定义:

0(未锁定),1(锁定)24位:

PLLON-PLL使能(手动)定义:

0(PLL关闭),1(PLL使能)。

进入待机或停机模式时,该位由硬件清零当PLL用作系统始终时,该位不能被清零。

19位:

CSSON时钟安全系统使能(由软件置1或清零)定义:

0(时钟监测器关闭),1(如果外部4-16M振荡器就绪,时钟监测器开启)18位:

HSEBYP外部高速时钟旁路。

定义:

0(晶振4-16M),1(有源晶振25M)。

调试模式下由软件控制。

只有在4-16M振荡器关闭情况下,才能写入该位。

17位:

HSERDY外部高速时钟就绪标志(自动)在HSEON位清零后,需6个外部4-25M振荡器周期清零。

定义:

0(4),16位:

HSEON外部高速时钟使能(软件控制)定义:

0(HSE关闭),1(HSE开启)。

待机或停机模式硬件清零,当用作系统系统时钟时,该位不能清零。

15-8位:

HSICAL7:

0-内部高速时钟校准。

系统启动时,这些位被自动初始化。

7-3位:

HSITRIM4:

0-内部高速时钟调整(软件控制,与HSICAL叠加,相当于手动微调)1位:

HSIRDY内部高速时钟就绪标志硬件置1,在HSION清零后,该位需要6个内部8M振荡周期清零。

定义:

0(没有就绪),1(有就绪)0位:

HSION内部高速时钟使能(软件控制)当从待机或停机返回用或外部振荡故障时由硬件置1。

若使用内部时钟做系统时钟则不能清零。

定义:

0(关),1(开)RCC_CFGR(RCC_CFGR(时钟配置寄存器时钟配置寄存器)31302928272625242322212019181716保留MCO3:

0保留OTGFSPREPLLMUL3:

0PLLXTPREPLLSRC1514131211109876543210ADCPRE1:

0PPRE22:

0PPRE12:

0HPRE3:

0SWS1:

0SW1:

027-24位:

MCO微控制器时钟输出(手动)注:

该时钟输出在启动和切换MCO时钟源时可能会被截断。

在系统时钟作为MCO引脚时,需保证输出不高于50M定义:

00xx(无输出),0100(系统时钟sysclk输出),0101(内部8M输出),0110(外部25M输出),0111(PLL时钟2分频输出),1000(PLL2输出)1001(PLL3时钟2分频输出),1010(XT1外部25M输出(为以太网),1011(PLL3时钟输出)22位:

OTGFSPRE全速USBOTG预分频(手动)在RCC_APB1ENR寄存器中使能全速OTG时钟之前,必须保证该位已经有效,如OTG时钟被使能则不能清0定义:

0(VCO时钟除3,但必须配置PLL输出为72M),1(VCO时钟除2,但必须配置PLL输出为48M)21-18位:

PLLMUL-PLL倍频系数(手动)注:

只有在PLL关闭的情况下才能被写入,且PLL的输出频率不能超过72M定义:

000x,10xx,1100(保留),0010(PLL4倍),0011(PLL5倍),0100(PLL6倍),0101(PLL7倍),0110(PLL8倍),0111(PLL9倍),1101(PLL6.5倍)17位:

PLLXTPRE-PREDIV1分频因子低位(软件控制)与RCC_CFGR2的0位为同一位。

如果RCC_CFGR23:

1为000,则该位控制PREDIV1对输入时钟进行2分频(PLLXPRE=1),或不对输入时钟分频(PLLXPRE=0),只能在关闭PLL时才写入此位16位:

PLL输入时钟源(软件控制,且只能在关闭PLL时才写入此位)定义:

0(HIS时钟2分频做PLL输入),1(PREDIV1输出做PLL输入)注:

当改变主PLL的输入时钟源时,必须在选定了新的时钟源后才能关闭原来的时钟源15/14位:

ADCPRE-ADC预分频(手动)定义:

00(PCLK2-2分频),01(PCLK2-4分频),10(PCLK2-6分频),11(PCLK2-8分频)13-11位:

PPRE22:

0-APB2预分频(手动)定义:

0xx(HCLK不分频),100(HCLK2分频),101(HCLK4分频),110(HCLK8分频),111(HCLK16分频)10-8位:

PPRE12:

0-APB1预分频(手动)定义:

0xx(HCLK不分频),100(HCLK2分频),101(HCLK4分频),110(HCLK8分频),111(HCLK16分频),注小于367-4位:

HPRE3:

0-AHB预分频(手动)定义:

0xxx(SYSCLK不分频),1000(2分频),1001(4分频),1010(8分频),1011(16分频)1100(64分频),1101(128分频),1110(256分频),1111(512分频).注:

AHB时钟预分频大于1时,必须开预取缓冲器。

当使用以太网模块时,频率至少25M3-2位:

SWS1:

0系统时钟切换状态(自动)定义:

00(HIS作为系统时钟),01(HSE做系统时钟),10(PLL做系统时钟),11(不可用)1-0位:

SW系统时钟切换(手动,自动,自动时时钟安全须开启)定义:

00(HIS做系统时钟),01(HSE做系统时钟),10(PLL做系统时钟),11(不可用)RCC_CIR(RCC_CIR(时钟中断寄存器时钟中断寄存器)31302928272625242322212019181716保留CSSC保留PLLRDYCHSERDYCHISRDY