显示电路研发设计VHDL编程.docx

《显示电路研发设计VHDL编程.docx》由会员分享,可在线阅读,更多相关《显示电路研发设计VHDL编程.docx(14页珍藏版)》请在冰豆网上搜索。

显示电路研发设计VHDL编程

第9章显示电路设计

本章重点讨论输出结果在数码管上的显示。

电子线路输出一般都是用灯的亮与不亮来表示输出的高低电平,这种显示不直观。

数码管显示能够更加直观、形象的描述现象。

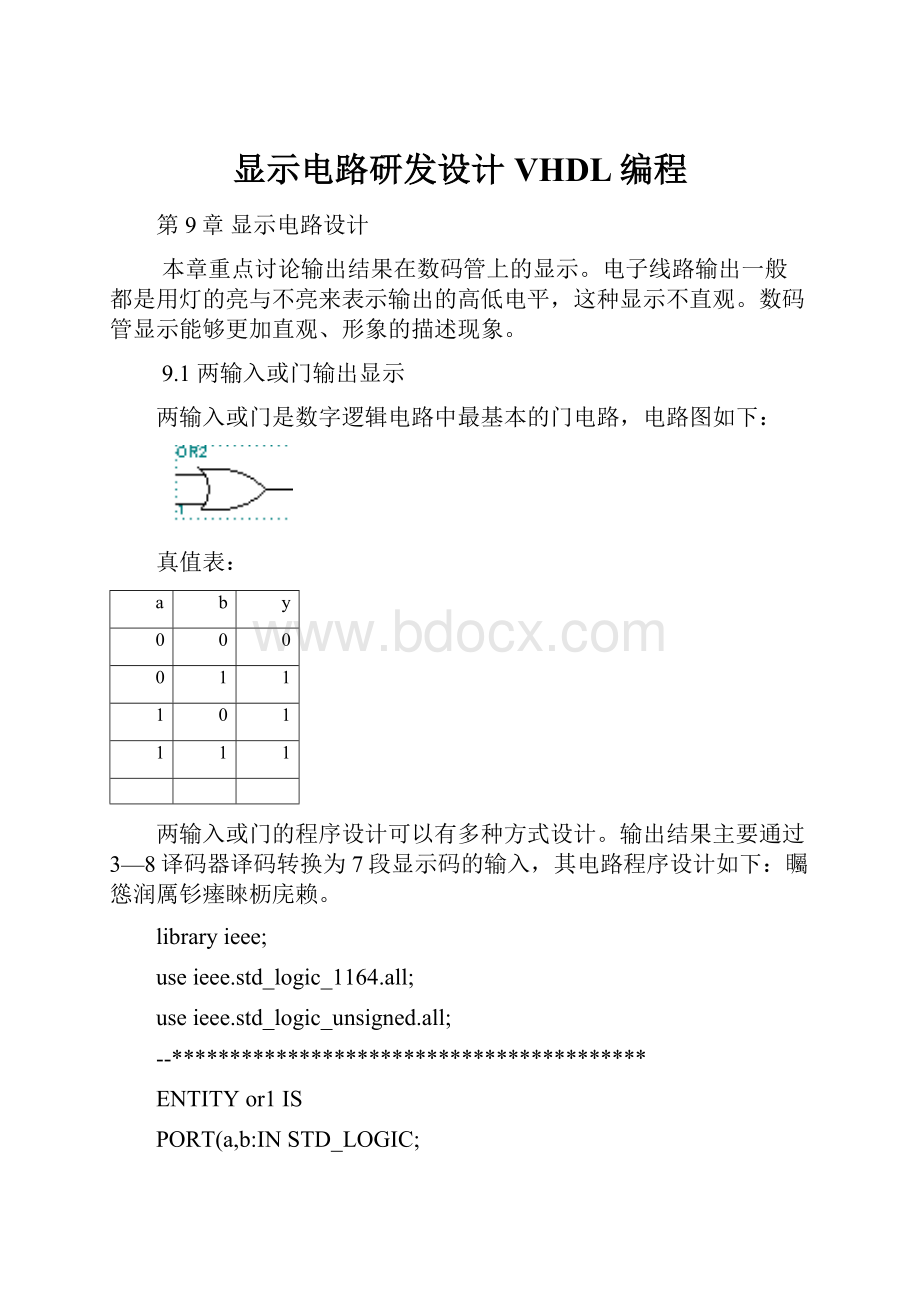

9.1两输入或门输出显示

两输入或门是数字逻辑电路中最基本的门电路,电路图如下:

真值表:

a

b

y

0

0

0

0

1

1

1

0

1

1

1

1

两输入或门的程序设计可以有多种方式设计。

输出结果主要通过3—8译码器译码转换为7段显示码的输入,其电路程序设计如下:

矚慫润厲钐瘗睞枥庑赖。

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

--*****************************************

ENTITYor1IS

PORT(a,b:

INSTD_LOGIC;

out_c:

outstd_logic_vector(7downto0);

out_38:

outstd_logic_vector(2downto0)

);

ENDor1;

--*******************************************

architecturertlOFor1IS

signaly:

std_logic;

begin

y<=aORb;

out_38<="000";

out_c<="00111111"wheny='0'else

"00000110";

ENDrtl;

波形图如下:

9.23进制计数器

上一章讲到过3进制计数器的设计原理,按照一般的显示需要两个灯显示结果,在这里我们用一个数码管显示。

让读者能够更加直观的理解3进制计数器的记数过程。

其程序设计如下:

聞創沟燴鐺險爱氇谴净。

顶层文件设计:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYdsp3IS

PORT(enable:

INSTD_LOGIC;

clk:

INSTD_LOGIC;

out_38:

outstd_logic_vector(2downto0);

segment:

OUTSTD_LOGIC_VECTOR(6DOWNTO0)

);

ENDdsp3;

ARCHITECTURErt1OFdsp3IS

COMPONENTcount3

PORT(enable:

INSTD_LOGIC;

clk:

INSTD_LOGIC;

q:

OUTSTD_LOGIC_VECTOR(1DOWNTO0));

ENDCOMPONENT;

SIGNALq:

STD_LOGIC_VECTOR(1DOWNTO0);

BEGIN

U0:

count3PORTMAP(enable,clk,q);

out_38<="000";

segment<="00111111"whenq="00"else

"00000110"whenq="01"else

"1011011";

ENDrt1;

再该程序中用COMPONENT命令调用了3进制计数器的设计程序,其程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYcount3IS

PORT(

enable:

INSTD_LOGIC;

clk:

INSTD_LOGIC;

q:

OUTSTD_LOGIC_VECTOR(1DOWNTO0));

ENDcount3;

ARCHITECTURErt1OFcount3IS

SIGNALq_tmp:

STD_LOGIC_VECTOR(1DOWNTO0);

BEGIN

process(clk)

begin

IF(clk'eventandclk='1')then

if(enable='1')then

if(q_tmp="10")then

q_tmp<=(others=>'0');

else

q_tmp<=q_tmp+1;

endif;

endif;

endif;

q<=q_tmp;

endprocess;

endrt1;

波形图如下:

9.324进制计数器

24进制计数器显示和3进制计数器的显示思路一样。

不同之处在于前者需要两个数码管,在设计时必须考虑选择数码管。

在任何自顶向下的VHDL设计描述中,设计人员常常将整个设计的系统划分为几个模块,然后采用结构描述方式对整个系统进行描述。

残骛楼諍锩瀨濟溆塹籟。

9.3.1顶层结构体的VHDL源代码

24进制计数器显示程序设计过程中就包含了记数部分、显示部分。

另外为了使记数准确,我们必须要获得稳定的频率,即还包括稳定的频率源部分。

下面我们给出顶层结构体的VHDL源代码。

其中3个模块以元件的形式给出,首先在结构体的说明部分进行元件说明,然后在结构体中进行例化调用。

同时在结构体的说明部分定义了中间信号,主要用来在模块之间传递信息。

酽锕极額閉镇桧猪訣锥。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYclockIS

PORT(

clk:

INSTD_LOGIC;

enable:

INSTD_LOGIC;

sel:

OUTSTD_LOGIC_VECTOR(2DOWNTO0);

segment:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDclock;

ARCHITECTURErt1OFclockIS

COMPONENTclk_div1000

PORT(clk:

INSTD_LOGIC;

clk_div:

outSTD_LOGIC);

endcomponent;

componentcount24

PORT(

enable:

INSTD_LOGIC;

clk0:

INSTD_LOGIC;

qh:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

ql:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

endcomponent;

componentdisplay

PORT(

clk:

INSTD_LOGIC;

qh:

INSTD_LOGIC_VECTOR(3DOWNTO0);

ql:

INSTD_LOGIC_VECTOR(3DOWNTO0);

sel:

outSTD_LOGIC_VECTOR(2DOWNTO0);

segment:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

endcomponent;

signalqh:

STD_LOGIC_VECTOR(3DOWNTO0);

signalql:

STD_LOGIC_VECTOR(3DOWNTO0);

signalclk0:

STD_LOGIC;

begin

u0:

clk_div1000PORTMAP(clk,clk0);

u1:

count24PORTMAP(enable,clk0,qh,ql);

u2:

displayPORTMAP(clk,qh,ql,sel,segment);

endrt1;

9.3.2频率源VHDL源代码

为了获得的稳定的频率源,我们才用1000赫兹频率作为输入,用1000进制计数器分频得到1赫兹频率。

其程序如下:

彈贸摄尔霁毙攬砖卤庑。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYclk_div1000IS

PORT(clk:

INSTD_LOGIC;

clk_div:

outSTD_LOGIC);

ENDclk_div1000;

ARCHITECTURErt1OFclk_div1000IS

SIGNALq_tmp:

integerrange0to999;

BEGIN

process(clk)

begin

IF(clk'eventandclk='1')then

if(q_tmp=999)then

q_tmp<=0;

else

q_tmp<=q_tmp+1;

endif;

endif;

endprocess;

process(clk)

begin

IF(clk'eventandclk='1')then

if(q_tmp=999)then

clk_div<='1';

else

clk_div<='0';

endif;

endif;

endprocess;

endrt1;

9.3.3计数部分VHDL源代码

24进制计数器的计数主要是24进制,在这里我们把24分为个位和十位设计。

其VHDL源代码如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYcount24IS

PORT(

enable:

INSTD_LOGIC;

clk0:

INSTD_LOGIC;

--cout:

outSTD_LOGIC;

qh:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

ql:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDcount24;

ARCHITECTURErt1OFcount24IS

SIGNALqh_temp,ql_temp:

STD_LOGIC_VECTOR(3DOWNTO0);謀荞抟箧飆鐸怼类蒋薔。

BEGIN

process(clk0)

begin

IF(clk0'eventandclk0='1')then

if(enable='1')then

if(qh_temp="0010"andql_temp="0011")then

qh_temp<="0000";

ql_temp<="0000";

else

if(ql_temp="1001")then

ql_temp<="0000";

qh_temp<=qh_temp+1;

else

ql_temp<=ql_temp+1;

endif;

endif;

endif;

endif;

qh<=qh_temp;

ql<=ql_temp;

endprocess;

endrt1;

9.3.4显示模块VHDL源代码

显示模块的输入信号主要来自于计数部分的输出信息。

在输出信号中,我们采用循环点亮两个LED七段显示数码管显示输出。

我们通过信号来进行2个LED七段显示数码的选择,从而将输出信号送到相应的LED七段显示数码上完成24进制计数器的结果显示。

模块框图如下:

厦礴恳蹒骈時盡继價骚。

从图中可以看出,显示模块有四个部分构成:

八进制计数器、计时位选择电路、七段显示译码电路。

在外部时钟信号clk的作用下,8进制计数器的输出从000到111按顺序循环变化,输出信号为sel。

信号sel作为计时位选择电路的选择信号,用来选择对应位的数据并将其转换为四位位矢量。

最后将计时位选择电路的输出信号q送到七段显示译码电路的输入端口,将其转换成用来点燃LED七段显示数码管的segment信号。

茕桢广鳓鯡选块网羈泪。

下面描述显示模块中的四个子电路,然后描述其总体功能。

8进制计数器VHDL源代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYcount8IS

PORT(

clk:

INSTD_LOGIC;

sel:

OUTSTD_LOGIC_VECTOR(2DOWNTO0));

ENDcount8;

ARCHITECTURErt1OFcount8IS

SIGNALsel_tmp:

STD_LOGIC_VECTOR(2DOWNTO0);

BEGIN

process(clk)

begin

IF(clk'eventandclk='1')then

if(sel_tmp="111")then

sel_tmp<=(others=>'0');

else

sel_tmp<=sel_tmp+1;

endif;

endif;

sel<=sel_tmp;

endprocess;

endrt1;

计时位选择电路的功能是根据8进制计数器的计数输出的选择信号来选择对应计时显示位的计时数据,作为送致七段显示译码电路的输入数据。

在计时位选择电路中我们要将输入数据都转化成4位宽度的数据。

其VHDL源代码如下:

鹅娅尽損鹌惨歷茏鴛賴。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYtime_chooseIS

PORT(sel:

INSTD_LOGIC_VECTOR(2DOWNTO0);

qh:

INSTD_LOGIC_VECTOR(3DOWNTO0);

ql:

INSTD_LOGIC_VECTOR(3DOWNTO0);

q:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDtime_choose;

ARCHITECTURErt1OFtime_chooseIS

BEGIN

PROCESS(sel,qh,ql)

BEGIN

CASEselIS

WHEN"000"=>q<=ql;

WHEN"001"=>q<=qh;

WHENOTHERS=>q<="XXXX";

ENDCASE;

ENDPROCESS;

ENDrt1;

七段显示译码电路的功能是将显示的数据转换成用来点燃

LED七段显示数码管的segment信号。

其VHDL源代码如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYseg7IS

PORT(q:

INSTD_LOGIC_VECTOR(3DOWNTO0);

segment:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDseg7;

ARCHITECTURErt1OFseg7IS

BEGIN

PROCESS(q)

BEGIN

CASEqIS

WHEN"0000"=>segment<="0111111";

WHEN"0001"=>segment<="0000110";

WHEN"0010"=>segment<="1011011";

WHEN"0011"=>segment<="1001111";

WHEN"0100"=>segment<="1100110";

WHEN"0101"=>segment<="1101101";

WHEN"0110"=>segment<="1111101";

WHEN"0111"=>segment<="0100111";

WHEN"1000"=>segment<="1111111";

WHEN"1001"=>segment<="1101111";

WHENOTHERS=>segment<="XXXXXXX";

ENDCASE;

ENDPROCESS;

ENDrt1;

下面对24进制计数器显示模块总体功能描述。

在描述24进制计数器显示模块时,我们以引用元件的形式来调用以上描述的子电路。

其VHDL源代码如下:

籟丛妈羥为贍偾蛏练淨。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYdisplayIS

PORT(

clk:

INSTD_LOGIC;

qh:

INSTD_LOGIC_VECTOR(3DOWNTO0);

ql:

INSTD_LOGIC_VECTOR(3DOWNTO0);

sel:

OUTSTD_LOGIC_VECTOR(2DOWNTO0);

segment:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDdisplay;

ARCHITECTURErt1OFdisplayIS

COMPONENTcount8

PORT(clk:

INSTD_LOGIC;

sel:

OUTSTD_LOGIC_VECTOR(2DOWNTO0));

ENDCOMPONENT;

COMPONENTtime_choose

PORT(sel:

INSTD_LOGIC_VECTOR(2DOWNTO0);

qh:

INSTD_LOGIC_VECTOR(3DOWNTO0);

ql:

INSTD_LOGIC_VECTOR(3DOWNTO0);

q:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDCOMPONENT;

COMPONENTseg7

PORT(q:

INSTD_LOGIC_VECTOR(3DOWNTO0);

segment:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDCOMPONENT;

SIGNALsel_tmp:

STD_LOGIC_VECTOR(2DOWNTO0);

SIGNALq:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALsegment_tmp:

STD_LOGIC_VECTOR(6DOWNTO0);

BEGIN

U0:

count8PORTMAP(clk,sel_tmp);sel<=sel_tmp;

U2:

time_choosePORTMAP(sel_tmp,qh,ql,q);

U3:

seg7PORTMAP(q,segment_tmp);

segment<=segment_tmp;

ENDrt1;