fpga设计方案1 (1).doc

《fpga设计方案1 (1).doc》由会员分享,可在线阅读,更多相关《fpga设计方案1 (1).doc(8页珍藏版)》请在冰豆网上搜索。

FPGA设计方案

一、功能概述

业务接口模块FPGA实现以下功能:

l与MCU通信的模块

l业务接口模块的初始化信息模块

l控制以太网芯片通信的模块

l与610通信的模块

二、结构框图

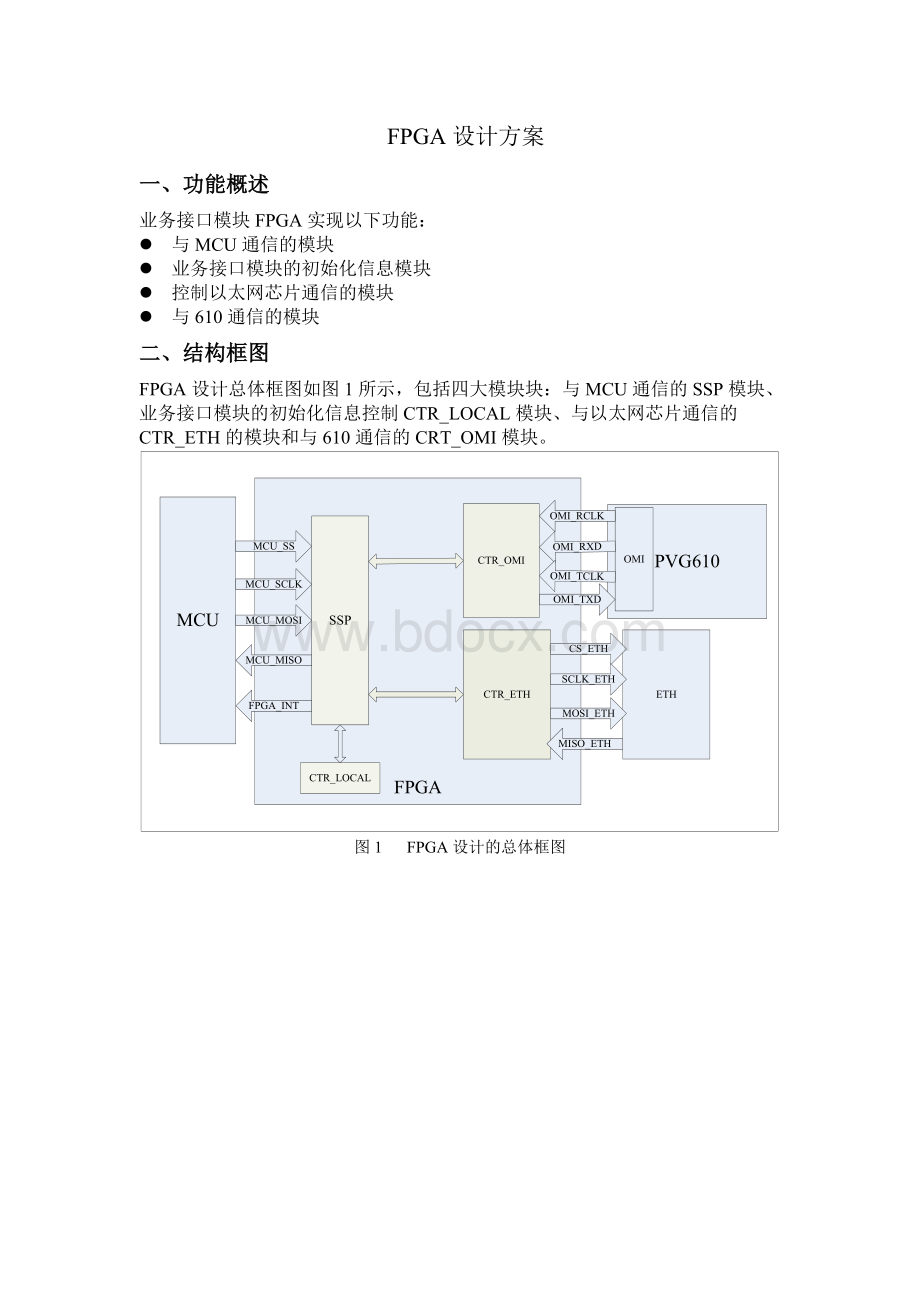

FPGA设计总体框图如图1所示,包括四大模块块:

与MCU通信的SSP模块、业务接口模块的初始化信息控制CTR_LOCAL模块、与以太网芯片通信的CTR_ETH的模块和与610通信的CRT_OMI模块。

图1FPGA设计的总体框图

三、接口说明

表1输入输出接口说明表:

信号名称

IO方向

信号说明

MCU_SS

I

网管监控模块MCU输给业务接口模块FPGA的片选信号,低电平有效。

MCU_SCLK

I

网管监控模块MCU输给业务接口模块FPGA的时钟信号,上升/下降沿采集数据。

MCU_MOSI

I

网管监控模块MCU输给业务接口模块FPGA的数据。

MCU_MISO

O

业务接口模块FPGA输出给网管监控模块MCU的数据。

FPGA_INT

O

业务接口模块FPGA输出给网管监控模块MCU的中断信号,低电平有效。

OMI_RCLK

I

PVG610的OMI给业务接口模块FPGA的接收时钟,上升/下降沿采集数据。

OMI_RXD

I

PVG610的OMI给业务接口模块FPGA的数据信号

OMI_TCLK

I

PVG610的OMI给业务接口模块FPGA的发送时钟,上升/下降沿采集数据。

OMI_TXD

O

业务接口模块FPGA给PVG610的OMI的数据信号

CS_ETH

O

ETH芯片的片选信号,低电平有效

SCLK_ETH

O

业务接口模块FPGA给ETH芯片的时钟

MOSI_ETH

O

业务接口模块FPGA给发送数据ETH芯片

MISO_ETH

I

业务接口模块ETH芯片发送数据给FPGA

四、各模块功能、接口及时序说明

4.1FPGA与MCU通信模块

图2FPGA与MCU通信模块框图

MCU与FPGA之间传输数据方式为SPI,MCU作主片,FPGA为从片;业务接口模块需要中断时,由FPGA产生中断请求信号。

SSPI—INSTREG表示指令寄存器,FPGA对该寄存器中的指令进行解析

4.1.1指令解析单元

1.设计框图

图3指令解析单元框图

2.实现方案

MCU_CS有效,接收单元接收数据,第一个字节接收完毕后FIR_BYTE_RECIED有效,使能指令解析单元,接受的第一个自己放入指令解析单元的指令寄存器。

表2标识位含义说明表:

r/w

A0

A1

使能信号(高有效)

0

0

0

wren_OMI

1

0

0

rden_OMI

0

0

1

wren_ETH

1

0

1

rden_ETH

1

1

x

rden_LOCAL

4.1.2数据接收单元

图4SSP模块接收数据单元

4.1.3数据发送单元

图5SSP模块接收数据单元

4.1.4中断产生单元

图6SSP模块中断产生单元

4.2业务接口模块初始信息模块

图7业务接口模块初始信息模块框图

系统上电后,控制单元发中断信号LOCAL_CONF_INT,MCU响应该中断后,该控制单元收到rden_LOCAL有效信号时,产生rd_en,按照时钟rd_clk读出INIT_CONF_ROM中的业务接口模块的初始配置信息,并送到SSP_TX单元。

由于INIT_CONF_ROM中的数据时预先存的,在控制单元中设置一个减计数器LOCAL_rd_cnt,它的初始值为要读的数据个数,当该计数器为LOCAL_rd_cnt=0时,rd_en为低,配置信息发送完毕。

4.3FPGA与ETH芯片通信模块

图8FPGA与ETH芯片通信设计框图

4.3.1给ETH芯片发送数据模块

图9给ETH芯片发送数据的实现框图

4.3.1读ETH芯片配置信息模块

图10读ETH芯片配置信息实现框图

4.4FPGA与PVG610的OMI通信模块

图11FPGA与PVG610的OMI通信

4.4.1发OMI数据的设计与实现

图12发OMI数据的实现框图

4.4.2收OMI数据的设计与实现

图13收OMI数据的实现框图