Cadence SPB使用经验总结.docx

《Cadence SPB使用经验总结.docx》由会员分享,可在线阅读,更多相关《Cadence SPB使用经验总结.docx(16页珍藏版)》请在冰豆网上搜索。

CadenceSPB使用经验总结

CadenceSPB使用方法

1.在用OrCadCaptureCIS画电路原理图时,不同电路图页面之间的信号互联,单信号线(wire)用分页端口连接器(OffPageConnector)实现互联,总线(Bus)用端口(Port)实现互连(也可以用分页端口连接器(OffPageConnector))。

2.特别注意:

在FPGA原理图设计中,在为FPGA设计原理图符号时,一般要将FPGA分为多个部分,这时一定要注意在管脚功能划分时,要将Bank2中用于配置的管脚,包括:

配置模式选择管脚M0、M1,CCLK,DIN,INIT_B等与TMS,TCK,TDO,TDI等一起划分到FPGA的配置(Configuration)部分。

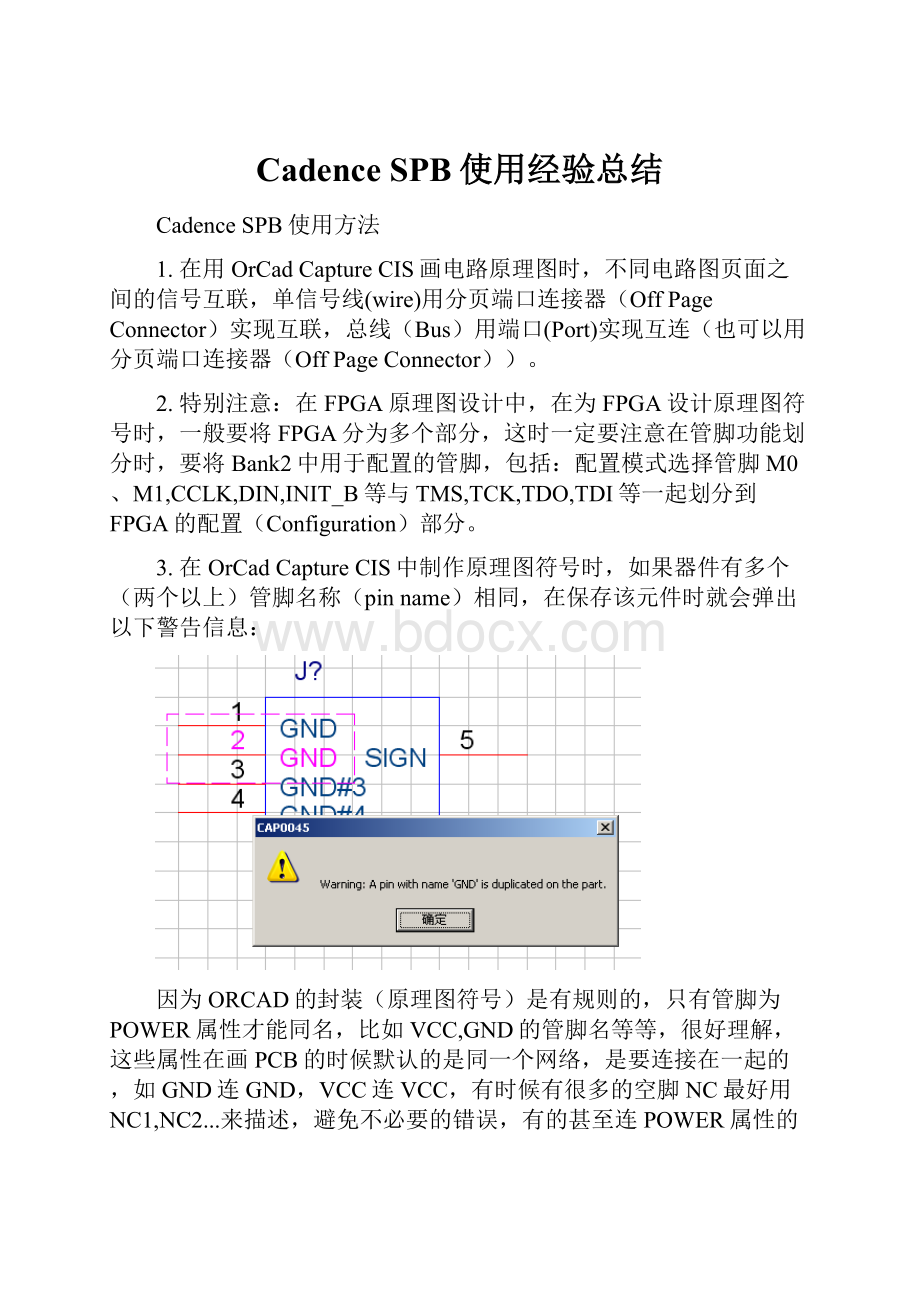

3.在OrCadCaptureCIS中制作原理图符号时,如果器件有多个(两个以上)管脚名称(pinname)相同,在保存该元件时就会弹出以下警告信息:

因为ORCAD的封装(原理图符号)是有规则的,只有管脚为POWER属性才能同名,比如VCC,GND的管脚名等等,很好理解,这些属性在画PCB的时候默认的是同一个网络,是要连接在一起的,如GND连GND,VCC连VCC,有时候有很多的空脚NC最好用NC1,NC2...来描述,避免不必要的错误,有的甚至连POWER属性的管脚名都不做重复的。

如果忽略这些这些警告信息,则当使用这些元件符号画电路图,在生成网表(CreateNetlist)时就会产生错误:

#79Error[ALG0050]DuplicatePinName"SW"foundonPackageLM2852Y,U21PinNumber9:

SCHEMATIC1,POWERSUPLLY(1.80,3.20).Pleaserenumberoneofthese.

这时选中设计,可以利用accessories菜单的libcorrectionutil->libraryverification/correction来批量修改重复管脚定义(即:

批量把重复的管脚名改为不同)。

(accessories->libcorrectionutil->libraryverification/correction)但是通过这种方法只能修改元件库Library中的元件,不能更新到原理图页面中。

如图所示,选中DuplicatePinNames复选框。

当然也可以手动把重复管脚名称改过来,即加数字编号:

1,2,3……。

或者把重复管脚名称管脚的属性改为POWER,因为CIS里面只允许POWER属性的管脚同名。

出现这个问题,另外一个可能的原因是因为制作元件时Partname和Partnumber混了。

于其后期出现了问题再修改,就不如在最初设计原理图符号时就把问题解决了,即:

要把PinName改成互不相同,如加上0,1,2,3...的编號,例如:

NC1,NC2,NC3……,等,还有PinNumber不可为空或者为0。

总之,allegro的netlist不能有相同的管脚名,除了power类型的管脚。

在做零件的過程,可以先將vcc或vss設成powerpin,這樣了,既使都叫vcc也不會有問題。

但是如果是I/O,建議你乖乖的給它名字,要不然它可是不會讓你轉netlists的。

#79Error[ALG0050]DuplicatePinName"SW"foundonPackageLM2852Y,U21PinNumber9:

SCHEMATIC1,POWERSUPLLY(1.80,3.20).Pleaserenumberoneofthese.

这个意思是说,你的原理图VDD有重复的名字,处理方法点上这个U21,点右键.出现EDITPART,把VDD有些重复的改成VDD1,VDD2,还有些GND改成GND1.

这样操作了是更新了图上的器件的引脚,怎么给它更新到库里呢?

编辑完成后,关闭对话框,会弹出信息问你要不要更新。

你可以选择更新当前或所有同样的封装。

要想保存到库里去,防止以后现有这样的事发生:

1你编辑好以后关悼对话框,你先更新所有的吧;

2编辑好之后.到原理图看下图操作。

如果你要更新你库文件里的,可以在DESIGNCache里面复制你更新的封装,粘贴到你的库文件复盖你的原封装就行了。

每个Part的PinName是不可以重复的,你要修改一下的。

只有当他们的Type为Power时才可以重复。

如果在前期原理图符号设计中忽略了重复管脚的问题,在出现错误时,在原理图中修改错误的最简捷的处理方法如下例所示:

#1Error[ALG0050]DuplicatePinName"PVIN"foundonPackageLM20123MH,U22PinNumber7:

SCHEMATIC1,POWERSUPLLY(6.60,4.00).Pleaserenumberoneofthese.

错误信息提示,U22PinNumber7为DuplicatePinName"PVIN",则在相应的原理图页面找到该元件U22,选中它。

单击鼠标右键,在弹出菜单中选择EditPart,

打开元件编辑页面,

按住Ctrl键选中所有重复名称的管脚(DuplicatePinName),点击右键选择EditProperties,

弹出管脚属性编辑窗口:

给其中的重复管脚重新命名,编号。

单击OK按钮关闭,关闭PartEdit窗口:

在弹出的SavePartInstance提示窗口中,选择UpdateAll,

其余两个提示都选YES,更新全部,则在原理图中的所有元件都得到更新。

4.OrcadCaptureCIS中原理图符号的管脚编号(PinNumber而不是管脚名称PinName)与AllegroPCBDesign中的PCB封装管脚相对应。

例如:

与

就不能匹配,PCB封装是以字母开头编号的,所以要把原理图封装的管脚编号与管脚名称改为一致。

其实在原理图元件符号设计中,管脚名只是用作用户识别,并不起与PCB封装管脚对应的作用。

5.每次替换元件,包括把原理图中原来的元件删除,再重新放置,都要使用Tools->Annnotate,对设计重新编号。

负责软件认为是放置了一个元件的两个部分,从而产生Error[ALG0045]错误。

6.在OrcadCaptureCIS原理图生成元件清单时,从菜单Reports->CISBillofMaterials->Standard生成的元件清单和点击工具栏的“Billofmaterials”图标生成的元件清单是不同的,通过后者生成的元件清单包括每种具有相同元件值和相同封装的同种元件的个数。

在实际中更实用些。

利用后种方法生成元件清单时的设置:

在其中输入:

Header:

Item\tQuantity\tReference\tPart\PCBFootprint

Combinedpropertystring:

{Item}\t{Quantity}\t{Reference}\t{Value}\t{PCBFootprint}

生成的元件清单:

7.可以在库文件夹下直接右击“Rename”元件。

在Cache中用库中修改后的元件Replace原来的元件。

8.在用OrcadCaptureCIS设计元件符号,给元件管脚命名(PinName)时,不能用以下符号:

/;!

<>:

\",*。

而且不能出现同名的管脚。

同名管脚加数字1,2,3……来区分,最好是用#1,#2,#3来区分,这样就知道是同一个地上的不同引脚,如果用1,2,3来分的话,DATA1,DATA2,DATA3,它也是用1,2,3来分的,名字也都是data,但不是同一网络。

Cadence的Help文档:

(1)Wheneverappropriatetheinputpinsshouldbeplacedontheleftsideofthesymbolwithoutputsontheright.

(2)PinNaming

Pinsshouldbedesignatedwithfunctionalnames.Eachpinnamemustbeuniquetothatsymbolandmusthaveamatchingentryinthechips.prtfile.Typically,apinnamemustbealphanumeric,butyoucanhavenumbersaspinnamesforscalarpins.Theothercharactersthataresupported.byDesignEntryHDLasvalidcharactersinpinnamesareasfollows:

-#$%+=|?

^_.().

Thefollowingarenotvalidforpinnames:

Allextendedcharactersets/;!

<>:

\",*.

Whencreatingpartsmanually,placetheSIG_NAMEpropertiesoutsidethesymbol,nexttothepinitisattachedto.Textsizeisnottooimportantonthesepropertiessincetheyarenotdisplayedontheschematic.

Followlowassertedpinnameswithanasterisk(*)(forexample,OE*)or_N(forexampleOE_N).Donotdifferentiatelowassertedpinswithany

othernomenclature.Alllowassertedpinsshouldappearasbubblesandnotstraightpinstubs.

9.在使用PCBEditor设计PCB时,在放置(Place)元件之前,要确定PCB在波峰焊或者回流焊时的移动方向,尤其是贴片元件SMD,要使其两侧焊盘的连线与焊接时PCB的移动方向相垂直,从而可以确定元件的放置方向,然后选择Setup—>DesignParameters

在DesignParameterEditor窗口的Design选项卡中的Symbol选项中设置元件的放置角度。

如果在放置前没有确定元件的放置角度,则在布局时需要逐个调整,很费时间。

10.在用PCBEditor设计PCB,利用AntiEtch分割电源平面或者地平面时,选择Display—>Color/Visibility,

在ColorDialog中的Stack-Up选项组中,选中要分割的层subclasses与AntiEtch相交叉的复选框,否则,所画的AntiEtch分割线不可见。

11.对于在同一内电层有多个不同电压电源的PCB,在布局时就应该考虑尽可能将同等级的电压靠近放置,否则会给平面分割带来困难,或者造成电源走线过长,影响电源完整性。

可以用不同的颜色高亮显示所有不同的VCC电源,这样在布局的时候,尽可能将同等级的电压靠近放置,或者他们之间有连通,当然,这要综合考虑外部接口的位置。

12.在PCBEditor中,可以设置显示或者不显示电源和地网络的飞线。

选择Editor->Properties,在右侧控制面板的Find选项卡中的Findbyname中选择Net,单击More按钮,弹出FindbyNameorProperty对话框,点击左侧列表中的电源网络,使其出现在右侧的“Selectedobjects”列表中,点击Apply按钮。

在EditProperty对话框中,选择AvalilableProperties列表中的Ratsnest_Schedule,在右侧的Value中选择飞线的显示(与否)方式。

所以,有时PCBEditor不显示飞线,不是连接不存在,而是由于设置使其没有显示。

13.在约束规则PhysicalConstraintSet中的ByLayers可以根据阻抗计算的结果设置每一层的走线宽度,以及差分线的走线宽度和间距。

14.对于多引脚的BGA,CPG等封装,再设计焊盘时尽量将其设计的最小,扇出Fanout用的过孔也要与PCB各层对应起来(与焊盘设计相同),并且孔径尽量小。

否则会给扇出和走线带来困难。