计算机组成原理第四版课后题答案三四章.docx

《计算机组成原理第四版课后题答案三四章.docx》由会员分享,可在线阅读,更多相关《计算机组成原理第四版课后题答案三四章.docx(11页珍藏版)》请在冰豆网上搜索。

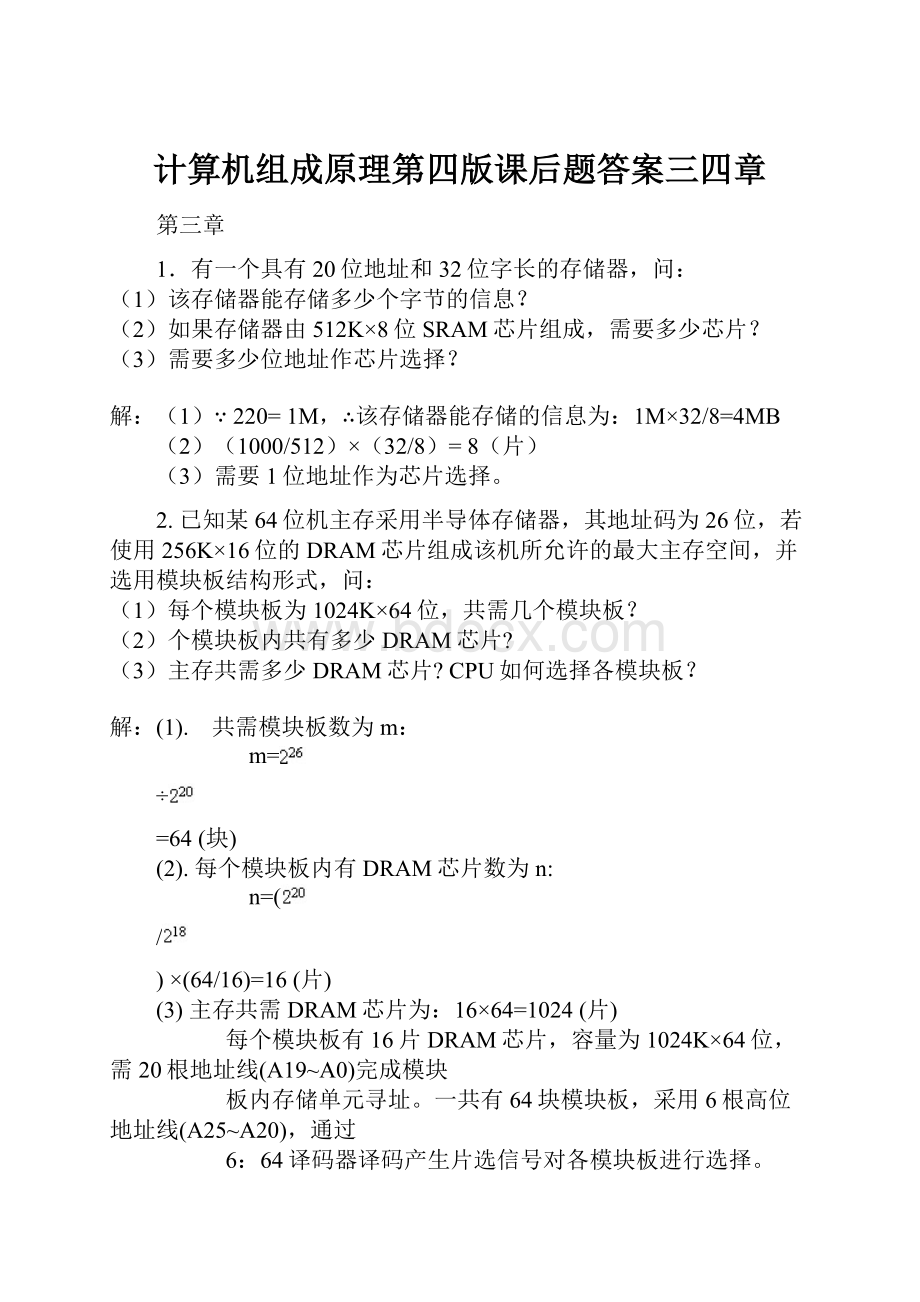

计算机组成原理第四版课后题答案三四章

第三章

1.有一个具有20位地址和32位字长的存储器,问:

(1)该存储器能存储多少个字节的信息?

(2)如果存储器由512K×8位SRAM芯片组成,需要多少芯片?

(3)需要多少位地址作芯片选择?

解:

(1)∵220=1M,∴该存储器能存储的信息为:

1M×32/8=4MB

(2)(1000/512)×(32/8)=8(片)

(3)需要1位地址作为芯片选择。

2.已知某64位机主存采用半导体存储器,其地址码为26位,若使用256K×16位的DRAM芯片组成该机所允许的最大主存空间,并选用模块板结构形式,问:

(1)每个模块板为1024K×64位,共需几个模块板?

(2)个模块板内共有多少DRAM芯片?

(3)主存共需多少DRAM芯片?

CPU如何选择各模块板?

解:

(1). 共需模块板数为m:

m=

÷

=64(块)

(2).每个模块板内有DRAM芯片数为n:

n=(

/

)×(64/16)=16(片)

(3)主存共需DRAM芯片为:

16×64=1024(片)

每个模块板有16片DRAM芯片,容量为1024K×64位,需20根地址线(A19~A0)完成模块

板内存储单元寻址。

一共有64块模块板,采用6根高位地址线(A25~A20),通过

6:

64译码器译码产生片选信号对各模块板进行选择。

3.用16K×8位的DRAM芯片组成64K×32位存储器,要求:

(1)画出该存储器的组成逻辑框图。

(2)设存储器读/写周期为0.5μS,CPU在1μS内至少要访问一次。

试问采用哪种刷新方式比较合理?

两次刷新的最大时间间隔是多少?

对全部存储单元刷新一遍所需的实际刷新时间是多少?

解:

(1)组成64K×32位存储器需存储芯片数为

N=(64K/16K)×(32位/8位)=16(片)

每4片组成16K×32位的存储区,有A13-A0作为片内地址,用A15A14经2:

4译码器产生片选信号

,逻辑框图如下所示:

(2)依题意,采用异步刷新方式较合理,可满足CPU在1μS内至少访问内存一次的要求。

设16K×8位存储芯片的阵列结构为128行×128列,按行刷新,刷新周期T=2ms,则异步

刷新的间隔时间为:

则两次刷新的最大时间间隔发生的示意图如下

可见,两次刷新的最大时间间隔为tmax

tmax=15.5-0.5=15(μS)

对全部存储单元刷新一遍所需时间为tR

tR=0.5×128=64 (μS)

7.某机器中,已知配有一个地址空间为0000H-3FFFH的ROM区域。

现在再用一个RAM芯片(8K×8)形成40K×16位的RAM区域,起始地址为6000H,假定RAM芯片有

和

信号控制端。

CPU的地址总线为A15-A0,数据总线为D15-D0,控制信号为R/

(读/写),

(访存),要求:

(1)画出地址译码方案。

(2)将ROM与RAM同CPU连接。

解:

(1)依题意,主存地址空间分布如右图所示,可选用2片27128(16K×8位)的EPROM作为

ROM区;10片的8K×8位RAM片组成40K×16位的RAM区。

27128需14位片内地址,而RAM需13位

片内地址,故可用A15-A13三位高地址经译码产生片选信号,方案如下:

(2)

8.存储器容量为64M,字长64位,模块数m=8,分别用顺序方式和交叉方式进行组织。

存储周期T=100ns,数据总线宽度为64位,总线周期τ=10ns.问顺序存储器和交叉存储器的带宽各是多少?

解:

信息总量:

q=64位×8=512位

顺序存储器和交叉存储器读出8个字的时间分别是:

t2=mT=8×100ns=8×10

(s)

t1=T+(m-1)

=100+7×10=1.7×10

(s)

顺序存储器带宽是:

W2=q/t2=512÷(8×10

)=64×10

(位/S)

交叉存储器带宽是:

W1=q/t1=512÷(1.7×10

)=301×10

(位/S)

9.CPU执行一段程序时,cache完成存取的次数为2420次,主存完成存取的次数为80

次,已知cache存储周期为40ns,主存存储周期为240ns,求cache/主存系统的效率和平均访问时间。

解:

先求命中率h

h=nc/(nc+nm)=2420÷(2420+80)=0.968

则平均访问时间为ta

ta=0.968×40+(1-0.968)×240=46.4(ns)

r=240÷40=6

cache/主存系统的效率为e

e=1/[r+(1-r)×0.968]=86.2%

10.已知Cache存储周期40ns,主存存储周期200ns,Cache/主存系统平均访问时间为50ns,求Cache的命中率是多少?

解:

∵ta=tc×h+tr×(1-h)

∴h=(ta-tr)/(tc-tr)=(50-200)/(40-200)=15/16=0.94

11.主存容量为4MB,虚存容量为1GB,则虚存地址和物理地址各为多少位?

如页面大小为4KB,则页表长度是多少?

解:

已知主存容量为4MB,虚存容量为1GB

∵

=4M∴物理地址为22位

又∵

=1G∴虚拟地址为30位

页表长度为1GB÷4KB=230÷212=218=256K

14.假设主存只有a,b,c三个页框,组成a进c出的FIFO队列,进程访问页面的序列是0,1,2.4,2,3,0,2,1.3,2号。

用列表法求采用LRU替换策略时的命中率。

解:

∴命中率为

15.从下列有关存储器的描述中,选择出正确的答案:

A.多体交叉存储主要解决扩充容量问题;

B.访问存储器的请求是由CPU发出的;

C.Cache与主存统一编址,即主存空间的某一部分属于Cache;

D.Cache的功能全由硬件实现。

解:

D

16.从下列有关存储器的描述中,选择出正确的答案:

A.在虚拟存储器中,外存和主存一相同的方式工作,因此允许程序员用比主存空间大得

多的外存空间编程;

B.在虚拟存储器中,逻辑地址转换成物理地址是由硬件实现的,仅在页面失效时才由操

作系统将被访问页面从外存调到内存,必要时还要先把被淘汰的页面内容写入外存;

C.存储保护的目的是:

在多用户环境中,既要防止一个用户程序出错而破坏系统软件或

其他用户程序,又要防止一个用户访问不是分配给他的主存区,以达到数据安全和保

密的要求。

解:

C

第四章

1.ASCll码是7位,如果设计主存单元字长为32位,指令字长为12位,是否合理?

为什

么?

解:

指令字长设计为12位不是很合理。

主存单元字长为32位,一个存储单元可存放4个ASCII码,

余下4位可作为ASCII码的校验位(每个ASCII码带一位校验位),这样设计还是合理的。

但是,设计指令字长为12位就不合理了,12位的指令码存放在字长32位的主存单元中,

造成19位不能用而浪费了存储空间。

2.假设某计算机指令长度为20位,具有双操作数、单操作数、无操作数三类指令形式,每个操作数地址规定用6位表示。

问:

若操作码字段固定为8位,现已设计出m条双操作数指令,n条无操作数指令,在此情况下,这台计算机最多可以设计出多少条单操作数指令?

解:

这台计算机最多可以设计出256-m-n条单操作数指令

3.指令格式结构如下所示,试分析指令格式及寻址方式特点。

解:

指令格式及寻址方式特点如下:

①单字长二地址指令;

②操作码OP可指定

=64条指令;

③RR型指令,两个操作数均在寄存器中,源和目标都是通用寄存器(可分别指定16个寄存器

之一);

④这种指令格式常用于算术逻辑类指令。

4.指令格式结构如下所示,试分析指令格式及寻址方式特点。

解:

指令格式及寻址方式特点如下:

①双字长二地址指令;

②操作码OP可指定

=64条指令;

③RS型指令,两个操作数一个在寄存器中(16个寄存器之一),另一个在存储器中;

④有效地址通过变址求得:

E=(变址寄存器)±D,变址寄存器可有16个。

5.指令格式结构如下所示,试分析指令格式及寻址方式特点。

解:

指令格式及寻址方式特点如下:

①单字长二地址指令;

②操作码OP可指定

=16条指令;

③有8个通用寄存器,支持8种寻址方式;

④可以是RR型指令、SS型指令、RS型指令、

6.一种单地址指令格式如下所示,其中I为间接特征,X为寻址模式,D为形式地址。

I,X,D组成该指令的操作数有效地址E。

设R为变址寄存器,R1为基值寄存器,PC为程序计数器,请在下表中第一列位置填入适当的寻址方式名称。

解:

①直接寻址

②相对寻址

③变址寻址

④基址寻址

⑤间接寻址

⑥基址间址寻址

7.某计算机字长16位,主存容量为64K字,采用单字长单地址指令,共有40条指令,试采用直接、立即、变址、相对四种寻址方式设计指令格式。

解:

40条指令需占用操作码字段(OP)6位,这样指令余下长度为10位。

为了覆盖主存640K字的地

址空间,设寻址模式(X)2位,形式地址(D)8位,其指令格式如下:

寻址模式定义如下:

X=00直接寻址有效地址E=D(直接寻址为256个存储单元)

X=01立即寻址D字段为操作数

X=10变址寻址有效地址E=(RX)+D(可寻址64K个存储单元)

X=11相对寻址有效地址E=(PC)+D(可寻址64K个存储单元)

其中RX为变址寄存器(16位),PC为程序计数器(16位),在变址和相对寻址时,位移量D可 正可负。

8.某机字长为32位,主存容量为1M,单字长指令,有50种操作码,采用页面寻址、立即、直接等寻址方式。

CPU中有PC,IR,AR,DR和16个通用寄存器,页面寻址可用PC高位部分与形式地址部分拼接成有效地址。

问:

(1)指令格式如何安排?

(2)主存能划分成多少页面?

每页多少单元?

(3)能否增加其他寻址方式?

解:

(1)依题意,指令字长32位,主存1M字,需20位地址A19-A0。

50种操作码,需6位OP,指令

寻址方式Mode为2位,指定寄存器Rn需4位。

设有单地址指令、双地址指令和零地址指

令,现只讨论前二种指令。

单地址指令的格式为:

Mode=00时为立即寻址方式,指令的23-0位为立即数;

Mode=01时为直接寻址方式,指令的19-0位为有效地址。

双地址指令的格式为:

Mode1=01时为寄存器直接寻址方式,操作数S=(Rn);

Mode1=11时为寄存器间址寻址方式,有效地址E=(Rn)。

Mode2=00时为立即寻址方式,指令的13-0位为立即数;

Mode2=01时为页面寻址方式;

Mode2=10时为变址寻址方式,E=(Rn)+D;

Mode2=11时为变址间址寻址方式,E=((Rn)+D)。

(2)由于页面寻址方式时,D为14位,所以页面大小应为

=16K字,则1M字可分为

=64个页面。

可由PC的高6位指出页面号。

(3)能增加其它寻址方式,例上述间址方式、变址间址寻址方式。

14.从以下有关RISC的描述中,选择正确答案。

A.采用RISC技术后,计算机的体系结构又恢复到早期的比较简单的情况。

B.为了实现兼容,新设计的RISC,是从原来CISC系统的指令系统中挑选一部分实现的。

C.RISC的主要目标是减少指令数,提高指令执行效率。

D.RISC设有乘、除法指令和浮点运算指令。

解:

C

15.根据操作数所在位置,指出其寻址方式(填空):

(1)操作数在寄存器中,为(A)寻址方式。

(2)操作数地址在寄存器,为(B)寻址方式。

(3)操作数在指令中,为(C)寻址方式。

(4)操作数地址(主存)在指令中,为(D)寻址方式

(5)操作数的地址,为某一寄存器内容与位移量之和可以是(E,F,G)寻址方式。

解:

A:

寄存器直接;B:

寄存器间接;C:

立即;

D:

直接; E:

相对; F:

基值;G:

变址