电子琴实验报告乐曲硬件演奏电路设计.docx

《电子琴实验报告乐曲硬件演奏电路设计.docx》由会员分享,可在线阅读,更多相关《电子琴实验报告乐曲硬件演奏电路设计.docx(15页珍藏版)》请在冰豆网上搜索。

电子琴实验报告乐曲硬件演奏电路设计

武夷学院实验报告

课程名称:

逻辑设计与FPGA项目名称:

乐曲硬件演奏电路设计

姓名:

专业:

微电子学班级:

14微电子学号:

04实验日期

一、实验预习部分:

1.实验目的:

学习利用数控分频器设计硬件乐曲演奏电路。

2.实验原理:

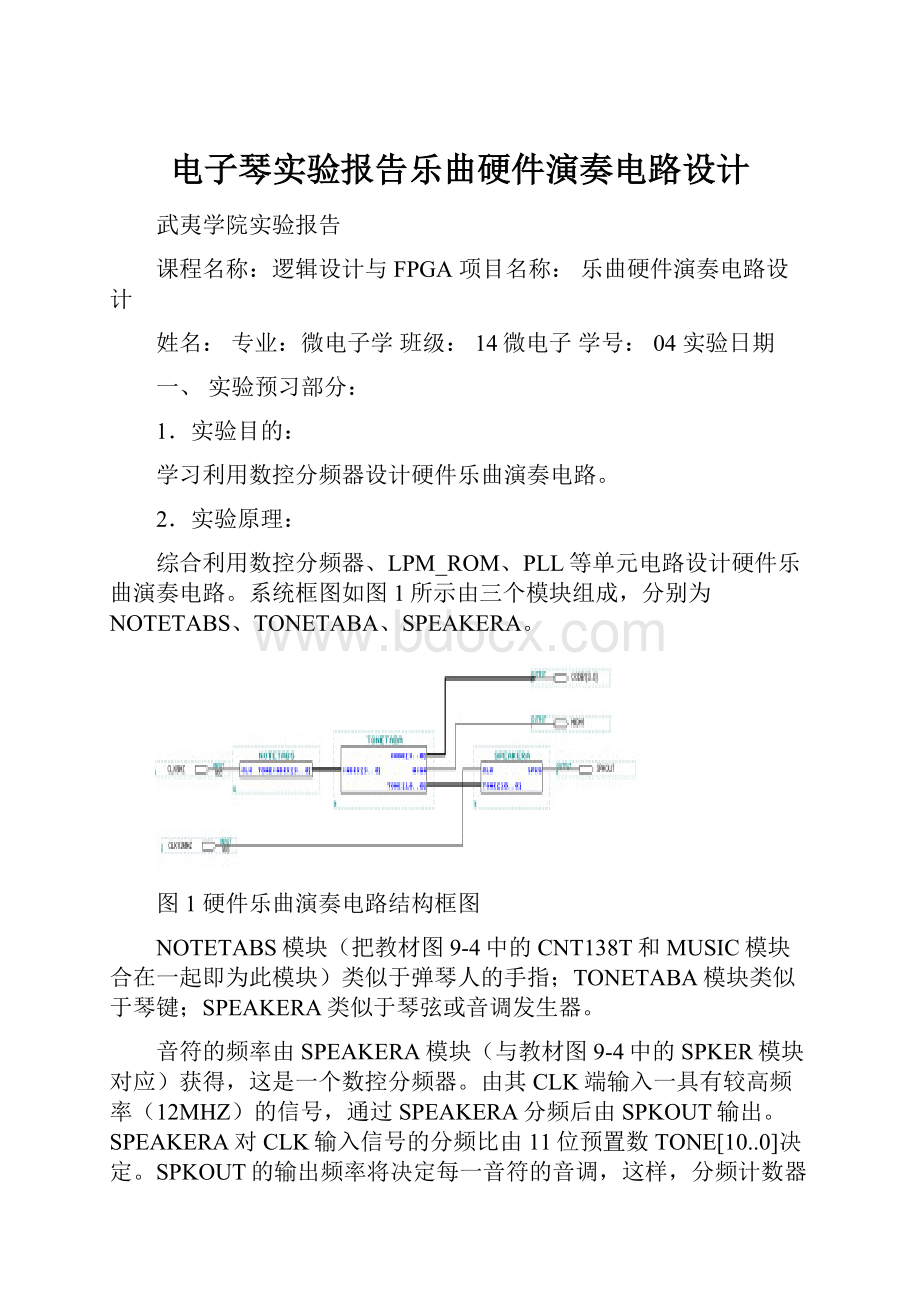

综合利用数控分频器、LPM_ROM、PLL等单元电路设计硬件乐曲演奏电路。

系统框图如图1所示由三个模块组成,分别为NOTETABS、TONETABA、SPEAKERA。

图1硬件乐曲演奏电路结构框图

NOTETABS模块(把教材图9-4中的CNT138T和MUSIC模块合在一起即为此模块)类似于弹琴人的手指;TONETABA模块类似于琴键;SPEAKERA类似于琴弦或音调发生器。

音符的频率由SPEAKERA模块(与教材图9-4中的SPKER模块对应)获得,这是一个数控分频器。

由其CLK端输入一具有较高频率(12MHZ)的信号,通过SPEAKERA分频后由SPKOUT输出。

SPEAKERA对CLK输入信号的分频比由11位预置数TONE[10..0]决定。

SPKOUT的输出频率将决定每一音符的音调,这样,分频计数器的预置值TONE[10..0]与SPKOUT的输出频率就有了对应关系。

例如在TONETABA模块(与教材图9-4中的F_CODE模块对应)中若取TONE[10..0]=1036,将发出音符“3”音的信号频率。

音符的持续时间需根据乐曲的速度及每个音符的节拍数来确定,TONETABA模块的功能首先是为SPEAKERA提供决定所发音符的分频预置数,而此数在SPEAKERA输入口停留的时间即为此音符的节拍值。

TONETABA模块是乐曲简谱码对应的分频预置数查表电路,其中需设置“梁祝”乐曲全部音符所对应的分频预置数,共13个,每一音符的停留时间由音乐节拍和音调发生器模块NOTATABS的CLK的输入频率决定,在此为4HZ。

这13个值的输出由对应于TONETABA的4位输入值INDEX[3..0]确定。

在NOTETABS中设置了一个8位二进制计数器(计数最大值为138),作为音符数据ROM的地址发生器。

这个计数器的计数频率选为4HZ,即每一计数值的停留时间为0.25秒,恰为当全音符设为1秒时,四四拍的4分音符持续时间。

例如,“梁祝”乐曲的第一个音符为“3”,此音在逻辑中停留了4个时钟节拍,即1秒时间,相应地,所对应的“3”音符分频预置值为1036,在SPEAKERA的输入端停留了1秒。

随着NOTETABS中的计数器按4HZ的时钟频率作加法计数时,即随地址递增时,音符数据ROM中的音符数据将从ROM通过TONEINDEX[3..0]端口输向TONETABA模块,乐曲就开始连续自然地演奏起来了。

具体参考教材实验9-1中说明。

3.实验仪器:

PC机1台QuartusII系统

开发板1块开发板外接扬声器

4.实验步骤及方法:

分模块设计和仿真测试,通过后联合仿真测试,最后下载到硬件中测试。

5.注意事项:

所有实验数据放入一个文件夹内,并且不要把文件夹放在系统盘上,实验结束后备份好实验数据,以备教师随时查阅。

实验预习成绩(百分制)实验指导教师签字:

二、实验过程记录部分:

1.实验过程记录:

1.1输入信号锁相环PLL0调节:

图2.1锁相环

管脚clk_50m(设置为B12)接入FPGA内部的50mhz的时钟信号,C0口为得到数控分屏器模块的输入时钟750KHZ,将分频比设置为1/67,即50000000HZ/67=74.6K约等于75K;c1口为2KHZ(配合下级的500分频模块),设置为:

c1=50000000HZ/25000=2KHZ。

1.2500分频模块count500(即500进制的计数器):

图2.2分频电路程序设计

如图2.2,因为梁祝歌曲只用低音和中音来演奏,为1/4拍,即四分之一拍,每个音符持续0.25秒的时间。

因为前级电路已经实现了从50MHZ到2KHZ的转换,要得到4HZ的频率,则用500进制的计数器(0到499的计数)产生的进位信号对2KHZ实现500分频(输出波形分析见后)。

1.4音符谱码存储模块设计构建:

1.4.1ROM的设置:

图2.4音符谱码存储模块ROM

音符谱码存储模的主体构想,是为了让前级模块所产生的139个状态与实际音符(DoReMiFaSoLaSi)构成映射。

因此需要构建一个包含《梁祝》乐谱的mif文件。

1.4.2构建《梁祝》乐谱.mif文件:

图2.5《梁祝》乐谱(部分截取)

因此综上所述,结合1.3的分析,音符谱码存储ROM,即输入为8位数据线,含256bit数据(实际只用了139bit);输出为4根线,这是由于《梁祝》这首歌曲只有低音的123567,以及中音的12356合高音部分的1,加上休止符一共13个状态,因此用4根数据线完全足够。

出于简化电路设计原则以及综合考虑电路测试的难易程度,我将高音部分的1当做中音的7来处理,将13个状态音符分为低音音符,中音音符和休止符;这样的好处是:

在测试时候,只需用一个LED的亮灭并结合七段数码管来具体表示播放的音符,此时若灯亮且七段数码管显示为“7”,实际代表输出为高音的“Do”。

注:

在以下的段落中,若出现“中音”,则用以表示“中音”的1235和“高音”的1.

因为下级模块“数控分频器”的最大计数值为11位2进制数,因此本级模块的输出TOO也为11位线宽。

因为下级模块数控分频器的最大计数值为2047,预置数为NT,计数模值为2047-NT+1=2048-NT,如NT=912,那么计数模值(分频系数)为2047-912=1135,因此将十进制的912改为十一位二进制的01110010000,赋值给TOO端(如图2.6),作为输出。

同时CODE端输出对应的音符(1到7),送至下级电路“谱码指示模块”;同时为了区别输出的音符为“低音”的(1到7)还是“中音”的(1到7),因此定义输出端口H,并接到FPGA的一个LED,若灯不亮则表示为“低音”,若点亮则表示“高音”,再配合谱码指示模块中的“七段数码管”上显示的数值进而显示具体的音符。

1.6数控分频器模块spker设计:

图2.7数控分频器模块spker代码及原理图

如图2.7,该模块主要作用是将预置数通过计数器与对应音符的频率构成映射。

由于数控分频器所给的的输入时钟为750KHZ。

由之前的分析,数控分频器的最大计数值为11位2进制数,即2^11=2047,逢2047后预置NT,为加法计数,输出为进位信号,进位信号总是取最大状态2047的译码。

不妨取1.5的假设,当NT=912时,计数模值:

2047-912=1135,数控分频器输出频率为750KHZ/1135=660HZ,再由下级电路模块对数控分频输出进行2分频,则输出频率为660HZ/2=330HZ,对应为低音的2(Re)。

(其余见附录一)即,对应总公式:

fo=[750KHZ/(2048-TN)]/2

其中,f0为音符频率; TN即(TOO)为预置数。

图2.8七段数码管译码转换模块代码及原理图

如图13所示T’触发器由D触发器加非门电路组成,构成一个二分频电路,由于直接从数控分频器出来的信号是脉宽极窄的信号,为了有利于驱动扬声器而添加此电路。

由1.5分析可知,f_code模块代的输出端CODE为4根线,而查阅PFGA开发板手册可知七段数码管的引脚有8个(包含一个小数点)。

因此,若想在数码管上显示对应的音符,必须开发一个模块,将4位二进制数(13个状态音符)用七位二进制数表示,对应7个输出端。

(因为本实验中用不到小数点,所以只考虑用数码管显示数值部分的7段LED)

1.7.2七段数码管的设置:

图2.9谱码指示模块总原理图

如图2.9,因为译码电路属于组合电路,属于异步,不受CLK控制,所以本级模块不设CLK端。

结合(附录二)由于FPGA的七段数码管是共阳极接法,所以输出为0则点亮,例如音符“0001”,对应输出“1111001”。

1.8二分频模块的设计:

图2.10二分频模块原理图

由1.6可知,承接数控分频器模块的输出频率,为输出真正的音符频率,还需要一个二分频模块实现,直接调用D触发器,外接非门构成T’触发器,实现二分频功能。

此外由于从数控分频器输出的某些音符的频率的占空比很小,如果不加本模块,会出现音符出现的声音非常短暂的情况,因此,本模块还起到提高占空比50%,进而提升功率的作用。

2.实验现象及原始数据记录:

2.1设计电路总图:

图2.11总原理图

2.2开发板管脚设置图:

图2.12全体管脚映射图

附录一

附录二

实验操作成绩(百分制)__________实验指导教师签字:

__________

图3.1实物图

1.2500分频模块波形仿真图:

图3.2500分频模块波形

由图3.2可见,计数器计数值从0到499,到达计数最大模值499时进位输出pm端由低电平转入高电平,即500进制实现500分频。

1.3cnt138模块波形仿真图:

图3.3138模块波形

由图3.3,计数器从0计数到138,一共139个不同输出状态,从cnt8端输出。

2.实验改进、心得体会及思考题:

2.1实验心得体会:

这次实验自己非常重视,花了很多时间,收获了很多。

自己对模块化设计电路有了更深,更直观的感受。

此外对用计数器来实现分频功能有了深刻的理解;在开发过程中也遇到了一系列的问题,例如在对“数控分频器”的VHDL代码编写中,开始不懂得signal和variable的区别,用前者时,信号在进程结束后才被改变,因此与所需音符状态无法及时对应;而后,我又发现如果在同一个进程中反复对variable所定义的变量进行赋值的话,软件只会把最后一次赋值的值赋给“变量”。

诸如此类的不再一一赘述,希望日后继续努力。

2.2实验思考题:

1.教材图9-4中由D触发器INST1和非门INST2构成的2分频电路对扬声器发声有什么影响?

答:

该电路模块实现对前级输出频率的二分频,让输出音符的频率全部处于人耳朵的听觉范围内。

同时还起到提高占空比至50%,进而提升功率的作用。

2.在电路上应该满足哪些条件,才能用数字器件直接输出的方波驱动扬声器发声?

答:

(1):

输出频率要在扬声器工作范围内;

(2):

输出的电流要能驱动扬声器的正常工作。

实验报告成绩(百分制)实验指导教师签字:

日期:

目录

第一章总论1

一、项目概况1

二、项目提出的理由与过程6

三、项目建设的必要性8

四、项目的可行性12

第二章市场预测15

一、市场分析15

二、市场预测16

三、产品市场竞争力分析19

第三章建设规模与产品方案22

一、建设规模22

二、产品方案22

三、质量标准22

第四章项目建设地点25

一、项目建设地点选择25

二、项目建设地条件25

第五章技术方案、设备方案和工程方案28

一、技术方案28

二、产品特点30

三、主要设备方案32

四、工程方案32

第六章原材料与原料供应35

一、原料来源及运输方式35

二、燃料供应与运输方式35

第七章总图布置、运输、总体布局与公用辅助工程37

一、总图布置37

二、运输38

三、总体布局38

四、公用辅助工程39

第八章节能、节水与安全措施44

一、主要依据及标准44

二、节能44

三、节水45

四、消防与安全45

第九章环境影响与评价47

一、法规依据47

二、项目建设对环境影响48

三、环境保护措施48

四、环境影响评价49

第十章项目组织管理与运行50

一、项目建设期管理50

二、项目运行期组织管理52

第十一章项目实施进度55

第十二章投资估算和资金筹措56