EDA课程设计UART控制器设计.docx

《EDA课程设计UART控制器设计.docx》由会员分享,可在线阅读,更多相关《EDA课程设计UART控制器设计.docx(16页珍藏版)》请在冰豆网上搜索。

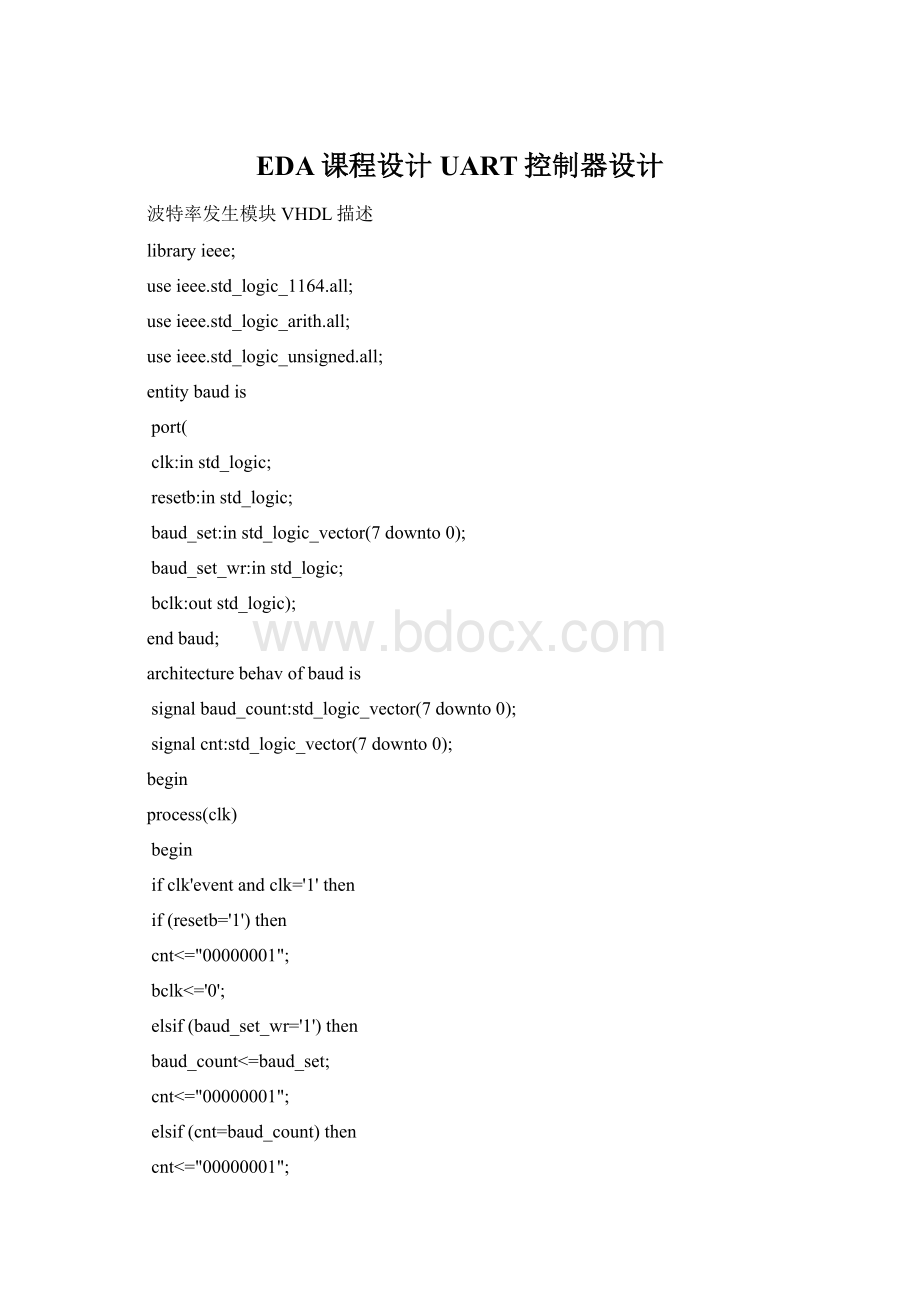

EDA课程设计UART控制器设计

波特率发生模块VHDL描述

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

entitybaudis

port(

clk:

instd_logic;

resetb:

instd_logic;

baud_set:

instd_logic_vector(7downto0);

baud_set_wr:

instd_logic;

bclk:

outstd_logic);

endbaud;

architecturebehavofbaudis

signalbaud_count:

std_logic_vector(7downto0);

signalcnt:

std_logic_vector(7downto0);

begin

process(clk)

begin

ifclk'eventandclk='1'then

if(resetb='1')then

cnt<="00000001";

bclk<='0';

elsif(baud_set_wr='1')then

baud_count<=baud_set;

cnt<="00000001";

elsif(cnt=baud_count)then

cnt<="00000001";

bclk<='1';

else

cnt<=cnt+1;

bclk<='0';

endif;

endif;

endprocess;

endbehav;

UART发送模块VHDL描述

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

entityUART_Transferis

Port(

bclkt:

instd_logic;

resett:

instd_logic;

cmd_p:

instd_logic;

txdbuf:

instd_logic_vector(7downto0);

txd:

outstd_logic;

txd_done:

outstd_logic);

endUART_Transfer;

architecturebehavofUART_Transferis

typestatesis(s_idle,s_start,s_wait,s_shift,s_stop);

signalstate:

states:

=s_idle;

signaltcnt:

integer:

=0;

signalxcnt16:

std_logic_vector(4downto0):

="00000";

signalprob:

std_logic_vector(4downto0);

begin

process(bclkt)

variablexbitcnt:

integer:

=0;

variableframlent:

integer:

=8;

variabletxds:

std_logic;

begin

if(bclkt'eventandbclkt='1')then

if(resett='1')then

state<=s_idle;

txd_done<='0';

txds:

='1';

else

casestateis

whens_idle=>

if(cmd_p='1')then

state<=s_start;

txd_done<='0';

else

state<=s_idle;

txd_done<='0';

txds:

='1';

endif;

whens_start=>

if(xcnt16>="01111")then

txds:

='0';

state<=s_wait;

xcnt16<="00000";

else

xcnt16<=xcnt16+'1';

state<=s_start;

endif;

whens_wait=>

if(xcnt16>="01110")then

if(xbitcnt=framlent)then

state<=s_stop;

xbitcnt:

=0;

else

state<=s_shift;

endif;

xcnt16<="00000";

else

xcnt16<=xcnt16+'1';

state<=s_wait;

endif;

whens_shift=>

txds:

=txdbuf(xbitcnt);

xbitcnt:

=xbitcnt+1;

state<=s_wait;

whens_stop=>

if(xcnt16>="01111")then

if(cmd_p='0')then

state<=s_idle;

xcnt16<="00000";

else

xcnt16<=xcnt16;

state<=s_stop;

endif;

txd_done<='1';

else

xcnt16<=xcnt16+1;

txds:

='1';

state<=s_stop;

endif;

whenothers=>state<=s_idle;

endcase;

endif;

txd<=txds;

prob<=xcnt16;

endif;

endprocess;

endbehav;

UART接收模块VHDL描述

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

entityUART_Recieveris

generic(framlenr:

integer:

=8);

port(

bclkr:

instd_logic;

resetr:

instd_logic;

rxdr:

instd_logic;

s_ready:

outstd_logic;

rbuf:

outstd_logic_vector(7downto0));

endUART_Reciever;

architecturebehavofUART_Recieveris

typestatesis(s_start,s_center,s_wait,s_sample,s_stop);

signalstate:

states:

=s_start;

signalrxd_sync:

std_logic;

begin

pro1:

process(rxdr)

begin

if(rxdr='0')then

rxd_sync<='0';

else

rxd_sync<='1';

endif;

endprocess;

pro2:

process(bclkr)

variablecount:

std_logic_vector(3downto0);

variablercnt:

integer:

=0;

variablerbufs:

std_logic_vector(7downto0);

begin

if(bclkr'eventandbclkr='1')then

if(resetr='1')then

state<=s_start;

count:

="0000";

else

casestateis

whens_start=>

if(rxd_sync='0')then

state<=s_center;

s_ready<='0';

rcnt:

=0;

else

state<=s_start;

s_ready<='0';

endif;

whens_center=>

if(rxd_sync='0')then

if(count="1000")then

state<=s_wait;

count:

="0000";

else

count:

=count+1;

state<=s_center;

endif;

else

state<=s_start;

endif;

whens_wait=>

if(count>="1110")then

if(rcnt=framlenr)then

state<=s_stop;

else

state<=s_sample;

endif;

count:

="0000";

else

count:

=count+1;

state<=s_wait;

endif;

whens_sample=>

rbufs(rcnt):

=rxd_sync;

rcnt:

=rcnt+1;

state<=s_wait;

whens_stop=>

s_ready<='1';

rbuf<=rbufs;

state<=s_start;

whenothers=>

state<=s_start;

endcase;

endif;

endif;

endprocess;

endbehav;

UART顶层模块VHDL描述

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

entitytopis

port(

clk:

instd_logic;

reset:

instd_logic;

rxd:

instd_logic;

xmit_cmd_p_in:

instd_logic;

baud_set_wr:

instd_logic;

rec_ready:

outstd_logic;

txd_out:

outstd_logic;

txd_done_out:

outstd_logic;

baud_set:

instd_logic_vector(7downto0);

txdbuf_in:

instd_logic_vector(7downto0);

rec_buf:

outstd_logic_vector(7downto0));

endtop;

architecturebehavoftopis

componentUART_Receiver

port(

bclkr:

instd_logic;

resetr:

instd_logic;

rxdr:

instd_logic;

r_ready:

outstd_logic;

rbuf:

outstd_logic_vector(7downto0));

endcomponent;

componentUART_Transfer

Port(

bclkt:

instd_logic;

resett:

instd_logic;

xmit_cmd_p:

i