NORSRAMSDRAMNAND结构和容量计算.docx

《NORSRAMSDRAMNAND结构和容量计算.docx》由会员分享,可在线阅读,更多相关《NORSRAMSDRAMNAND结构和容量计算.docx(24页珍藏版)》请在冰豆网上搜索。

NORSRAMSDRAMNAND结构和容量计算

NORflash,NANDflash,SDRAM构造和容量分析

1.NORflash构造和容量分析

例如:

HY29LV160。

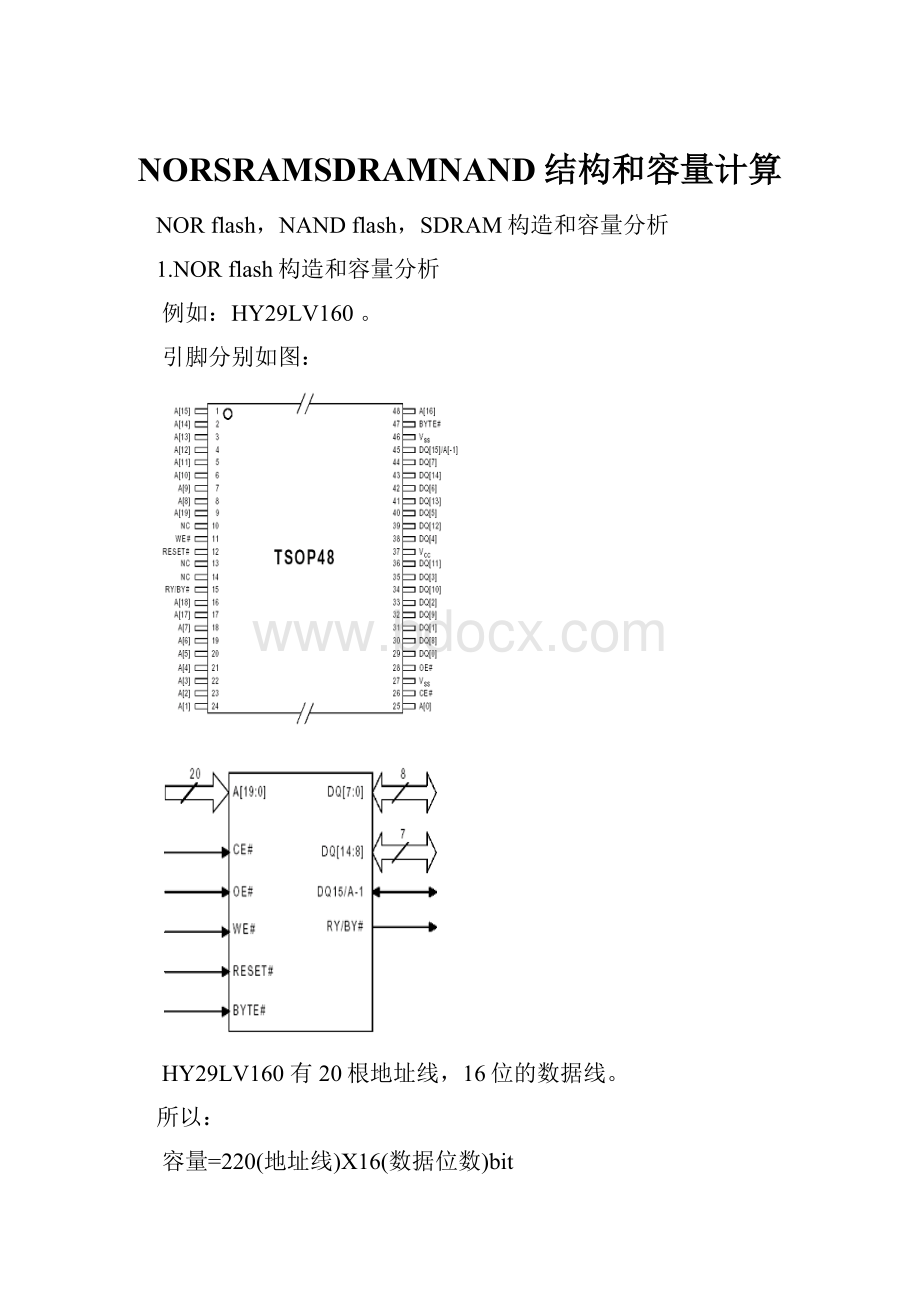

引脚分别如图:

HY29LV160有20根地址线,16位的数据线。

所以:

容量=220(地址线)X16(数据位数)bit

=1MX16bit=1MX2B

=2MB

2.SRAM简单介绍

SRAM是英文StaticRAM的缩写,它是一种具有静止存取功能的存,不需要刷新电路即能保存它部存储的数据。

SRAM不需要刷新电路即能保存它部存储的数据。

而DRAM〔DynamicRandomAccessMemory)每隔一段时间,要刷新充电一次,否那么部的数据即会消失,因此SRAM具有较高的性能,但是SRAM也有它的缺点,即它的集成度较低,一样容量的DRAM存可以设计为较小的体积,但是SRAM却需要很大的体积,且功耗较大。

所以在主板上SRAM存储器要占用一局部面积。

SRAM一种是置于CPU与主存间的高速缓存,它有两种规格:

一种是固定在主板上的高速缓存〔CacheMemory〕;另一种是插在卡槽上的COAST〔CacheOnAStick〕扩大用的高速缓存,另外在CMOS芯片1468l8的电路里,它的部也有较小容量的128字节SRAM,存储我们所设置的配置数据。

还有为了加速CPU部数据的传送,自80486CPU起,在CPU的部也设计有高速缓存,故在PentiumCPU就有所谓的L1Cache〔一级高速缓存〕和L2Cache〔二级高速缓存〕的名词,一般L1Cache是建在CPU的部,L2Cache是设计在CPU的外部,但是PentiumPro把L1和L2Cache同时设计在CPU的部,故PentiumPro的体积较大。

最新的PentiumII又把L2Cache移至CPU核之外的黑盒子里。

SRAM显然速度快,不需要刷新的操作,但是也有另外的缺点,就是价格高,体积大,所以在主板上还不能作为用量较大的主存。

现将它的特点归纳如下:

◎优点,速度快,不必配合存刷新电路,可提高整体的工作效率。

◎缺点,集成度低,功耗较大,一样的容量体积较大,而且价格较高,少量用于关键性系统以提高效率。

◎SRAM使用的系统:

○CPU与主存之间的高速缓存。

○CPU部的L1/L2或外部的L2高速缓存。

○CPU外部扩大用的COAST高速缓存。

○CMOS146818芯片〔RT&CMOSSRAM〕。

主要用途:

SRAM主要用于二级高速缓存(Level2Cache)。

它利用晶体管来存储数据。

与DRAM相比,SRAM的速度快,但在一样面积中SRAM的容量要比其他类型的存小。

SRAM

SRAM的速度快但昂贵,一般用小容量的SRAM作为更高速CPU和较低速DRAM之间的缓存〔cache〕.SRAM也有许多种,如AsyncSRAM(AsynchronousSRAM,异步SRAM)、SyncSRAM(SynchronousSRAM,同步SRAM)、PBSRAM(PipelinedBurstSRAM,流水式突发SRAM),还有INTEL没有公布细节的CSRAM等。

根本的SRAM的架构如图1所示,SRAM一般可分为五大局部:

存储单元阵列(corecellsarray),行/列地址译码器(decode),灵敏放大器(SenseAmplifier),控制电路(controlcircuit),缓冲/驱动电路(FFIO)。

SRAM是静态存储方式,以双稳态电路作为存储单元,SRAM不象DRAM一样需要不断刷新,而且工作速度较快,但由于存储单元器件较多,集成度不太高,功耗也较大。

3.SDRAM构造和容量分析

●SDRAM根底知识

SDRAM:

SynchronousDynamicRandomAccessMemory,同步动态随机存取存储器。

同步是指Memory工作需要步时钟,部的命令的发送与数据的传输都以它为基准。

动态是指存储阵列需要不断的刷新来保证数据不丧失。

随机是指数据不是线性依次存储,而是由指定地址进展数据读写。

SDRAM从开展到现在已经经历了四代,分别是:

第一代SDRSDRAM,第二代DDRSDRAM,第三代DDR2SDRAM,第四代DDR3SDRAM.

第一代与第二代SDRAM均采用单端〔Single-Ended〕时钟信号,第三代与第四代由于工作频率比拟快,所以采用可降低干扰的差分时钟信号作为同步时钟。

SDRSDRAM的时钟频率就是数据存储的频率,第一代存用时钟频率命名,如pc100,pc133那么说明时钟信号为100或133MHz,数据读写速率也为100或133MHz。

之后的第二,三,四代DDR〔DoubleDataRate〕存那么采用数据读写速率作为命名标准,并且在前面加上表示其DDR代数的符号,PC-即DDR,PC2=DDR2,PC3=DDR3。

如PC2700是DDR333,其工作频率是333/2=166MHz,2700表示带宽为2.7G。

DDR的读写频率从DDR200到DDR400,DDR2从DDR2-400到DDR2-800,DDR3从DDR3-800到DDR3-1666。

例如:

HY57V641620:

HY57V641620引脚分布:

●HY57V641620有12根地址线。

但要注意:

SDRAM的行地址和列地址是公用这12根地址线的。

行地址:

A11~A0,列地址:

A7~A0。

RAS#行地址锁存有效时,地址为行地址,A11~A0。

CAS#列地址锁存有效时,地址为列地址,A7~A0。

●HY57V641620有两个Bank地址。

AB1,BA0.用于片4个组BanK的选择。

●HY57V641620有16位数据总线:

DQ15~DQ0。

所以HY57V641620的容量计算公式是:

容量=212(行地址)X28(列地址)X16(数据位数)X22(片bank数)bit

=220X16X4bit

=1MX2X4Byte

=8MB

4.NANDflash构造和容量分析

●NANDFLASH和NORFLASH的区别

NANDFLASH在对大容量的数据存储需要中日益开展,到现今,所有的数码相机、多数MP3播放器、各种类型的U盘、很多PDA里面都有NANDFLASH的身影。

1.Flash的简介

NORFlash:

程序和数据可存放在同一片芯片上,拥有独立的数据总线和地址总线,能快速随机地读取,允许系统直接从Flash中读取代码执行,而无需先将代码下载至RAM中再执行

可以单字节或单字编程,但不能单字节擦除,必须以块为单位或对整片执行擦除操作,在对存储器进展编程之前需要对块或整片进展预编程和擦除操作。

NANDFLASH

以页为单位进展读写操作,1页为256B或512B;以块为单位进展擦除操作,1块为4KB、8KB或16KB。

具有快编程和快擦除的功能

数据、地址采用同一总线,实现串行读取。

随机读取速度慢且不能按字节随机编程

芯片尺寸小,引脚少,是位本钱〔bitcost〕最低的固态存储器

芯片存储位错误率较高,推荐使用ECC校验,并包含有冗余块,其数目大概占1%,当某个存储块发生错误后可以进展标注,并以冗余块代替

Samsung、TOSHIBA和Fujistu三家公司支持采用NAND技术NANDFlash。

目前,Samsung公司推出的最大存储容量可达8Gbit。

NAND主要作为SmartMedia卡、CompactFlash卡、PCMCIAATA卡、固态盘的存储介质,并正成为Flash磁盘技术的核心。

2.NANDFLASH和NORFLASH的比拟

1)性能比拟

flash闪存是非易失存储器,可以对称为块的存储器单元块进展擦写和再编程。

任何flash器件的写入操作只能在空或已擦除的单元进展,所以大多数情况下,在进展写入操作之前必须先执行擦除。

NAND器件执行擦除操作是十分简单的,而NOR那么要求在进展擦除前先要将目标块所有的位都写为0。

由于擦除NOR器件时是以64~128KB的块进展的,执行一个写入/擦除操作的时间为5s,与此相反,擦除NAND器件是以8~32KB的块进展的,执行一样的操作最多只需要4ms。

执行擦除时块尺寸的不同进一步拉大了NOR和NADN之间的性能差距,统计说明,对于给定的一套写入操作(尤其是更新小文件时),更多的擦除操作必须在基于NOR的单元中进展。

这样,中选择存储解决方案时,设计师必须权衡以下的各项因素。

●NOR的读速度比NAND稍快一些。

●NAND的写入速度比NOR快很多。

●NAND的4ms擦除速度远比NOR的5s快。

●大多数写入操作需要先进展擦除操作。

●NAND的擦除单元更小,相应的擦除电路更少。

2)接口差异

NORflash带有SRAM接口,有足够的地址引脚来寻址,可以很容易地存取其部的每一个字节。

NAND器件使用复杂的I/O口来串行地存取数据,共用8位总线〔各个产品或厂商的方法可能各不一样〕。

8个引脚用来传送控制、地址和数据信息。

NAND读和写操作采用512字节的页和32KB的块为单位,这一点有点像硬盘管理此类操作,很自然地,基于NAND的存储器就可以取代硬盘或其他块设备。

3)容量和本钱

NANDflash的单元尺寸几乎是NOR器件的一半,由于生产过程更为简单,NAND构造可以在给定的模具尺寸提供更高的容量,也就相应地降低了价格,大概只有NOR的十分之一。

NORflash占据了容量为1~16MB闪存市场的大局部,而NANDflash只是用在8~128MB的产品当中,这也说明NOR主要应用在代码存储介质中,NAND适合于数据存储,NAND在CompactFlash、SecureDigital、PCCards和MMC存储卡市场上所占份额最大。

4)可靠性和耐用性

采用flahs介质时一个需要重点考虑的问题是可靠性。

对于需要扩展MTBF的系统来说,Flash是非常适宜的存储方案。

可以从寿命(耐用性)、位交换和坏块处理三个方面来比拟NOR和NAND的可靠性。

在NAND闪存中每个块的最大擦写次数是一百万次,而NOR的擦写次数是十万次。

NAND存储器除了具有10比1的块擦除周期优势,典型的NAND块尺寸要比NOR器件小8倍,每个NAND存储器块在给定的时间的删除次数要少一些。

5)位交换〔错误率〕

所有flash器件都受位交换现象的困扰。

在某些情况下(很少见,NAND发生的次数要比NOR多),一个比特位会发生反转或被报告反转了。

一位的变化可能不很明显,但是如果发生在一个关键文件上,这个小小的故障可能导致系统停机。

如果只是报告有问题,多读几次就可能解决了。

当然,如果这个位真的改变了,就必须采用错误探测/错误更正(EDC/ECC)算法。

位反转的问题更多见于NAND闪存,NAND的供给商建议使用NAND闪存的时候,同时使用EDC/ECC算法。

这个问题对于用NAND存储多媒体信息时倒不是致命的。

当然,如果用本地存储设备来存储操作系统、配置文件或其他敏感信息时,必须使用EDC/ECC系统以确保可靠性。

6)坏块处理

NAND器件中的坏块是随机分布的。

以前也曾有过消除坏块的努力,但发现成品率太低,代价太高,根本不划算。

NAND器件需要对介质进展初始化扫描以发现坏块,并将坏块标记为不可用。

现在的FLSAH一般都提供冗余块来代替坏块如发现某个块的数据发生错误〔ECC校验〕,那么将该块标注成坏块,并以冗余块代替。

这导致了在NANDFlash中,一般都需要对坏块进展编号管理,让每一个块都有自己的逻辑地址。

7)易于使用

可以非常直接地使用基于NOR的闪存,可以像其他存储器那样连接,并可以在上面直接运行代码。

由于需要I/O接口,NAND要复杂得多。

各种NAND器件的存取方法因厂家而异。

在使用NAND器件时,必须先写入驱动程序,才能继续执行其他操作。

向NAND器件写入信息需要相当的技巧,因为设计师绝不能向坏块写入,这就意味着在NAND器件上自始至终都必须进展虚拟映射。

8)软件支持

当讨论软件支持的时候,应该区别根本的读/写/擦操作和高一级的用于磁盘仿真和闪存管理算法的软件,包括性能优化。

在NOR器件上运行代码不需要任何的软件支持,在NAND器件上进展同样操作时,通常需要驱动程序,也就是存技术驱动程序(MTD),NAND和NOR器件在进展写入和擦除操作时都需要MTD。

使用NOR器件时所需要的MTD要相对少一些,许多厂商都提供用于NOR器件的更高级软件,这其中包括M-System的TrueFFS驱动,该驱动被WindRiverSystem、Microsoft、QNXSoftwareSystem、Symbian和Intel等厂商所采用。

驱动还用于对DiskOnChip产品进展仿真和NAND闪存的管理,包括纠错、坏块处理和损耗平衡。

在掌上电脑里要使用NANDFLASH存储数据和程序,但是必须有NORFLASH来启动。

除了SAMSUNG处理器,其他用在掌上电脑的主流处理器还不支持直接由NANDFLASH启动程序。

因此,必须先用一片小的NORFLASH启动机器,在把OS等软件从NANDFLASH载入SDRAM中运行才行。

9)主要供给商

NORFLASH的主要供给商是INTEL,MICRO等厂商,曾经是FLASH的主流产品,但现在被NANDFLASH挤的比拟难受。

它的优点是可以直接从FLASH中运行程序,但是工艺复杂,价格比拟贵。

NANDFLASH的主要供给商是SAMSUNG和东芝,在U盘、各种存储卡、MP3播放器里面的都是这种FLASH,由于工艺上的不同,它比NORFLASH拥有更大存储容量,而且廉价。

但也有缺点,就是无法寻址直接运行程序,只能存储数据。

另外NANDFLASH非常容易出现坏区,所以需要有校验的算法。

Nand-flash存储器是flash存储器的-种,其部采用非线性宏单元模式,为固态大容量存储器的实现提供了廉价有效的解决方案。

Nand-flash存储器具有容量较大,改写速度快,适用于大量资料的存储,因而在业界得到了越来越广泛的应用,如嵌入式产品中包括数码相机、MP3随身听记忆卡、体积小巧的U盘等。

存和NOR型闪存的根本存储单元是bit,用户可以随机访问任何一个bit的信息。

而NAND型闪存的根本存储单元是页〔Page〕〔可以看到,NAND型闪存的页就类似硬盘的扇区,硬盘的一个扇区也为512字节〕。

每一页的有效容量是512字节的倍数。

所谓的有效容量是指用于数据存储的局部,实际上还要加上16字节的校验信息,因此我们可以在闪存厂商的技术资料当中看到“〔512+16〕Byte〞的表示方式。

目前2Gb以下容量的NAND型闪存绝大多数是〔512+16〕字节的页面容量,2Gb以上容量的NAND型闪存那么将页容量扩大到〔2048+64〕字节。

NAND型闪存以块为单位进展擦除操作。

闪存的写入操作必须在空白区域进展,如果目标区域已经有数据,必须先擦除后写入,因此擦除操作是闪存的根本操作。

一般每个块包含32个512字节的页,容量16KB;而大容量闪存采用2KB页时,那么每个块包含64个页,容量128KB。

每颗NAND型闪存的I/O接口一般是8条,每条数据线每次传输〔512+16〕bit信息,8条就是〔512+16〕×8bit,也就是前面说的512字节。

但较大容量的NAND型闪存也越来越多地采用16条I/O线的设计,如三星编号K9K1G16U0A的芯片就是64M×16bit的NAND型闪存,容量1Gb,根本数据单位是〔256+8〕×16bit,还是512字节。

寻址时,NAND型闪存通过8条I/O接口数据线传输地址信息包,每包传送8位地址信息。

由于闪存芯片容量比拟大,一组8位地址只够寻址256个页,显然是不够的,因此通常一次地址传送需要分假设干组,占用假设干个时钟周期。

NAND的地址信息包括列地址〔页面中的起始操作地址〕、块地址和相应的页面地址,传送时分别分组,至少需要三次,占用三个周期。

随着容量的增大,地址信息会更多,需要占用更多的时钟周期传输,因此NAND型闪存的一个重要特点就是容量越大,寻址时间越长。

而且,由于传送地址周期比其他存储介质长,因此NAND型闪存比其他存储介质更不适合大量的小容量读写请求。

和磁盘类似,NANDFlash读写数据的根本粒度为页〔page〕,然而读、写数据所需的时间却不一样,一般写入时间是读出的3到10倍。

此外,Flash不允许数据的直接覆盖写,必须首先擦除旧有数据才能写入新的,而擦除的粒度为块〔block〕,通常一个块包含有64个页。

擦除的速度是很慢的,而且每一块的擦除次数也有限,平均为100万次。

下面将给出一个例子来具体说明NANDFlash的特点。

下面是三星K9K8G08U0M芯片的Flash组织构造图。

NANDFlash组织构造图

从图中可以看出,整个Flash的容量为8448Mbit,其中含有8192个物理块,每块包含64个页,每页除了2K的数据区之外,还有64字节的额外空间(又成为OOB)用于存放错误校验码等信息。

除了Flash的主体,我们还可以看到一个一页大小的数据存放器。

事实上,每一次Flash的读写操作都需要使用这个存放器来完成。

例如,读操作实际上分成两个阶段,首先是把指定地址中的整页数据载入到存放器中〔时间为20微秒〕,然后再从存放器输出数据,可以连续输出,也可以根据指定偏移量随机输出,且随机输出的次数不限〔每个字节的输出周期为20纳秒〕;而写操作也分为两个阶段,第一阶段是把数据从外界输入到存放器,可以整页输入,也可以随机输入,且随机输入的次数不限,每字节的输入周期也是20纳秒,第二阶段便是把存放器中的数据固化到Flash上,时间为200微秒,每一页原那么上只能有一次固化操作,然而大局部NANDFlash〔如本例〕允许在同一页中的几个片断按照先后顺序分几次写入,本例中为4次,这种情况叫做partialpageprogramming。

除了partialpageprogramming,NANDFlash还有另外一种有意思的操作,也和数据存放器相关,叫做copy-back。

就是说,当某个数据页需要被复制到新的位置时,只需将其载入到数据存放器中,然后根据接收到的目标地址将该页数据固化到Flash上新的位置,这样就省去了整页数据在存放器和RAM之间的输入输出过程。

另外,在数据被载入到存放器之后,Flash允许程序使用随机输入数据的方式改写该页的局部容,然后再固化到目标位置。

●NAND根底知识

vcell:

NANDFlash的数据是以bit的方式保存在memorycell,一般来说,一个cell中只能存储一个bit。

vBitline:

这些cell以8个或者16个为单位,连成bitline,形成所谓的byte(x8)/word(x16),这就是NANDDevice的位宽。

这些Line会再组成Page.

NANDflash,largepage大小为2048字节,Smallpage为512字节

vNandflash以页为单位读写数据,而以块为单位擦除数据。

v按照这样的组织方式可以形成所谓的三类地址:

BlockAddress|PageAddress|ColumnAddress

v对于NANDFlash来讲,地址和命令只能在I/O[7:

0]上传递,数据宽度是8位。

而数据位可以是8位,或者16位,是根据IO的口的数量来决定的。

vNANDFLASH主要以页〔page〕为单位进展读写,以块(block)为单位进展擦除。

FLASH页的大小和块的大小因不同类型块构造而不同,块构造有两种:

小块〔图7〕和大块〔图8〕,小块NANDFLASH包含32个页,每页512+16字节;大块NANDFLASH包含64页,每页2048+64字节。

v其中,512B〔或1024B〕用于存放数据,16B〔64B〕用于存放其他信息〔包括:

块好坏的标记、块的逻辑地址、页数据的ECC校验和等〕。

NAND设备的随机读取得效率很低,一般以页为单位进展读操作。

系统在每次读一页后会计算其校验和,并和存储在页的冗余的16B的校验和做比拟,以此来判断读出的数据是否正确。

v大块和小块NANDFLASH都有与页大小一样的页存放器,用于数据缓存。

当读数据时,先从NANDFLASH存单元把数据读到页存放器,外部通过访问NANDFLASHI/O端口获得页存放器中数据〔地址自动累加〕;当写数据时,外部通过NANDFLASHI/O端口输入的数据首先缓存在页存放器,写命令发出后才写入到存单元中。

●NandFlash有多种构造

〔1〕下面针对三星K9F1208U0M,页面为512byte,IO数据为8位。

K9F1208U0M:

512Mbit=64MByte。

1Block=16KByte,

Numberof(block)=4096

1Block=32Page

1Page由3个分区,mainarea的两个分区,和sarearea三个分区组成

1Page=528Byte=512Byte(MainArea)+16Byte(SpareArea)

用户数据保存在mainarea中。

●首先,必须清楚一点,对于NANDFlash来讲,地址和命令只能在I/O[7:

0]上传递,数据宽度可以是8位或者16位,但是,对于x16的NANDDevice,I/O[15:

8]只用于传递数据。

●512byte需要9bit来表示,对于528byte系列的NAND,这512byte被分成1sthalf和2ndhalf,各自的访问由所谓的pointeroperation命令来选择,也就是选择了bit8的上下。

因此A8就是halfpagepointer〔这是我给出的一个名字〕,A[7:

0]就是所谓的columnaddress。

A8这一位地址被用来设置512byte的1sthalfpage还是2ndhalfpage,0表示1st,1表示2nd。

Block的地址是由A14以上的bit来表示。

A8是由硬件存放器决定的。

选择哪半个page是由IO传输的命令控制的。

具体参照datasheet,如下列图:

28=256byte256bytex2=512byte〔A8〕

●32个page需要5bit来表示,占用A[13:

9],即该page在块的相对地址,即pageaddress。

25=32page〔一个block有32个page〕

●Block的地址是由A14以上的bit来表示,例如512Mb的NAND,共4096block,因此,需要12个bit来表示,即A[25:

14],如果是1Gbit的528byte/page的NANDFlash,那么blockaddress用A[26:

14]表示。

2〔26-14+1〕=8192blocks〔总共有这些block〕

2〔26-9+1〕+2〔7-0+1〕=226=67108864page〔总共有这些pages〕

在编程上面可以这样:

NANDFlash的地址表示为:

BlockAddress|PageAddressinblock|halfpagepointer|ColumnAddress

地址传送顺序是Col