电子万年历时钟设计.docx

《电子万年历时钟设计.docx》由会员分享,可在线阅读,更多相关《电子万年历时钟设计.docx(36页珍藏版)》请在冰豆网上搜索。

电子万年历时钟设计

基于DS1302的数字时钟设计

一、设计目的

1、掌握电子时钟的基本工作方式。

2、进一步熟悉DS1302芯片的特性。

3、通过使用各基本指令,进一步熟练掌握单片机的编程和程序调试。

二、设计思路

利用AT89C52的特点及DS1302的特点,设计一种基于DS1302单片机控制,再利用数码管静态显示的可调可定时数字钟。

本系统硬件利用AT89S52作为CPU进行总体控制,通过DS1302时钟芯片获取准确详细的时间(年、月、日、周、日、时、分、秒准确时间),对时钟信号进行控制,同时利用数码管对时间进行准确显示年、月、日、周、日、时、分、秒。

三、设计过程

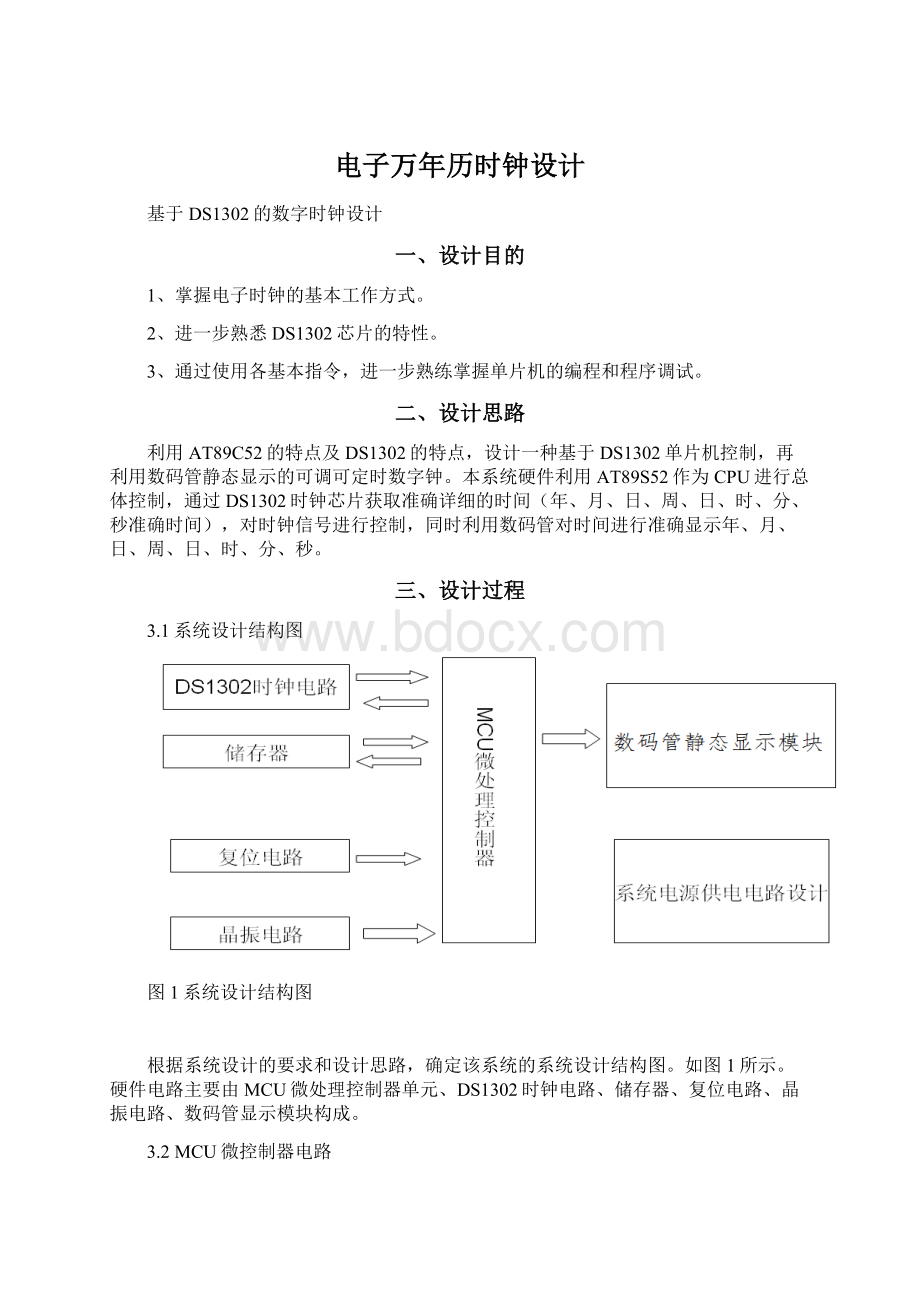

3.1系统设计结构图

图1系统设计结构图

根据系统设计的要求和设计思路,确定该系统的系统设计结构图。

如图1所示。

硬件电路主要由MCU微处理控制器单元、DS1302时钟电路、储存器、复位电路、晶振电路、数码管显示模块构成。

3.2MCU微控制器电路

AT89S52作为系统的核心控制元件,只有它能正常工作后才能使其它的元件进入正常工作状态。

因此,下面对AT89S52进行必要的说明,AT89S52的管脚如图3所示。

图3AT89S52的管脚

1)VCC:

40脚,供电电压,一般接+5V电压。

2)GND:

20脚,接工作地。

3)P0口:

1~8脚,P0口是一个8位漏极开路的双向I/O口。

作为输出口,每位能驱动8个TTL逻辑电平。

对P0端口写“1”时,引脚用作高阻抗输入。

当访问外部程序和数据存储器时,P0口也被作为低8位地址/数据复用。

在这种模式下,P0具有内部上电阻。

但是P0口在程序校验作为输出指令字节时,需要外部加上拉电阻,一般上拉电阻选4.7K~10K为宜。

本设计中用5.1K的排阻对P0口进行上拉电平。

4)P1口:

32~39脚,P1口是一个内部具有上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4个TTL门电流。

P1端口写入“1”后,被内部上拉电阻把端口拉高,此时可以作为作输入口使用。

作为输入使用时,被外部拉低的引脚由于内部电阻的原因,将输出电流。

5)P2口:

20~27脚,P2口是一个具有内部上拉电阻的8位双向I/O口,P2输出缓冲器能驱动4个TTL逻辑电平。

对P2端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入口使用。

6)P3口:

10~17脚,P3口是一个具有内部上拉电阻的8位双向I/O口,P3输出缓冲器能驱动4个TTL逻辑电平。

对P3端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入口使用。

7)RESET:

9脚,复位输入端。

当振荡器复位器件时,要保持RST脚两个机器周期的高电平时间。

8)ALE/P非:

30脚,当访问外部存储器时,地址锁存允许的输出电平用于锁存地址的地位字节。

在FLASH编程期间,此引脚用于输入编程脉冲。

在平时,ALE端以不变的频率周期输出正脉冲信号,此频率为振荡器频率的1/6。

因此它可用作对外部输出的脉冲或用于系统校验。

9)PSEN:

29脚,外部程序存储器的选通信号。

10)RST非/VP:

31脚,访问外部程序存储器控制信号。

当EA非为低电平时,读取外部程序存储器;当EA非端为高电平时,则读取内部程序存储器,设计中一般接高电平。

11)XTAL1:

19脚,振荡器反相放大器和内部时钟发生电路的输入端。

如采用外部时钟源时,XTAL1为输入端。

12)XTAL2:

18脚,振荡器反相放大器的输出端。

如采用外部时钟源时,XTAL2

应悬空不接。

3.3数码管静态显示电路

在Proteus仿真中,我用了带有译码器的单个数码管,实际中是没有带译码器的数码管的,这里有两种方法可以解决:

在实际焊板子是要改变端口对应且要改变程序以适应实际的八脚数码管。

用7447芯片来转换。

采用74HC595芯片驱动数码管,有关74HC芯片的介绍如下:

8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

1、特点

8位串行输入

8位串行或并行输出

存储状态寄存器,三种状态

输出寄存器可以直接清除

100MHz的移位频率

2、输出能力

并行输出,总线驱动

串行输出;标准

中等规模集成电路

3、应用

串行到并行的数据转换

4、描述

595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

6、参考数据

符号

参数

条件

TYP

单位

HC

HCt

tPHL/tPLH

传输延时

SHcp到Q7’

STcp到Qn

MR到Q7’

CL=15pF

Vcc=5V

16

17

14

21

20

19

Ns

Ns

Ns

fmax

STcp到SHcp

最大时钟速度

100

57

MHz

CL

输入电容

Notes1

3.53.5

pF

CPD

Powerdissipationcapacitanceperpackage.

Notes2

115130

pF

7、CPD决定动态的能耗,

PD=CPD×VCC×f1+∑(CL×VCC2×f0)

F1=输入频率,CL=输出电容f0=输出频率(MHz)Vcc=电源电压8、引脚说明

符号

引脚

描述

Q0…Q7

15,1,7

并行数据输出

GND

8

地

Q7’

9

串行数据输出

MR

10

主复位(低电平)

SHCP

11

移位寄存器时钟输入

STCP

12

存储寄存器时钟输入

OE

13

输出有效(低电平)

DS

14

串行数据输入

VCC

16

电源

9、功能表

输入

输出

功能

SHCP

STCP

OE

MR

DS

Q7’

Qn

×

×

L

↓

×

L

NC

MR为低电平时紧紧影响移位寄存器

×

↑

L

L

×

L

L

空移位寄存器到输出寄存器

×

×

H

L

×

L

Z

清空移位寄存器,并行输出为高阻状态

↑

×

L

H

H

Q6’

NC

逻辑高电平移入移位寄存器状态0,包含所有的移位寄存器状态移入,例如,以前的状态6(内部Q6”)出现在串行输出位。

×

↑

L

H

×

NC

Qn’

移位寄存器的内容到达保持寄存器并从并口输出

↑

↑

L

H

×

Q6’

Qn’

移位寄存器内容移入,先前的移位寄存器的内容到达保持寄存器并输出。

H=高电平状态

L=低电平状态

↑=上升沿

↓=下降沿

Z=高阻

NC=无变化

×=无效

图4全位静态数码管显示电路

图574HC595电路

3.4实时时钟电路

本设计使用的实时时钟电路芯片是美国DALLAS公司生产的一种高性能、低功耗、带RAM的实时时钟电路芯片DS1302。

VCC1为后备电源,VCC2为主电源。

在主电源关闭的情况下,也能保持时钟的连续运行。

DS1302由VCC1或VCC2两者中的较大者供电;当VCC2大于VCC1+0.2V时,VCC2给DS1302供电;当VCC2小于VCC1时,DS1302由VCC1供电。

X1和X2是振荡源,外接32.768kHz晶振。

RST非是复位/片选线,通过把RST非输入驱动置高电平来启动所有的数据传送。

3.5复位电路

在AT89S52单片机中的振荡器运行时,RST非引脚上保持到少2个机器周期的高电平输入信号,复位过程即可完成。

根据此原理,本设计采用上电复位和按键复位嵌套在系统中,增强了系统的实用性。

3.6晶振电路

AT89S52在工作时需要外部提供时钟信号,因此,本设计选择在其18脚19脚之间接上12MHz的晶振,为单片机提供1μs的机器振荡周期。

其电路连接图如图所示。

在图中,电容器C3、C4起稳定振荡频率、快速起振的作用,其电容值一般在20~50pF。

四、系统调试与结果

4.1系统调试过程

用Proteus画仿真电路后,将程序烧入芯片中起初出现乱码及按键功能混乱等错误,之后经过多次调整程序并解决了问题成功仿真。

4.2系统调试结果

图8调试结果

五、主要元器件与设备

Protues软件、AT89C512芯片、DS1302芯片、74HC595芯片及各电路模块

六、课程设计体会

本设计利用单片机AT89C512控制串行实时时钟芯DS1302构成数字时钟电路,实现计时功能。

该电路使用简单的三线接口,为单片机节省大量的接口资源,时钟芯片带有后备电池。

该时钟功能强大,性能优越,能为很多领域,特别是对时钟工作的准确性和可靠性有较高要求。

通过对电子时钟的设计的设计与制作,让我了解了电子时钟模块的编程思想,也让我明白了电子时钟的基本原理与设计理念,要设计一个电路必须先编好程序,用仿真软件测试成功后再得出结论。

通过这次学习,让我对该软件有了更熟悉的了解,我们应该自己动手,实际操作,才会有更深刻的理解。

经过这次设计我学到很多很多的的东西,不仅巩固了以前所学过的知识,而且通过这次课程设计使我懂得了理论与实际相结合的重要性,同时也提高了自己的实际动手能力和独立思考的能力。

最后感谢老师的授课和教导!

七、参考文献

[1]张义和.例说51单片机[M].北京:

人民邮电出版社,2010年

[2]阎石编著数字电子技术基础(第五版)北京高等教育出版社]2006.1~550

[3]蔡明文冯先成主编单片机课程设计华中科技大学出版社2007.3

[4]陈明萤编著8051单片机课程设计实训教材清华大学出版社2004

[5]康华光编著模拟电子技术基础(第五版)高等教育出版社2006

[6]黄智伟编著全国大学生电子设计竞赛电路(第一版)航空航天大学出版社2006.36

附录

源程序代码:

#include

#include

//---------------------------------------------------------------------------------------------------------------

#defineuintunsignedint

#defineucharunsignedchar

//---------------------------------------------------------------------------------------------------------------

/*ucharcodetable[]={0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,

0x80,0x98,0x88,0x83,0xc6,0xa1,0x86,0x8e};//共阳极数码管代码*/

ucharcodexingqi[8]={0x00,0x07,0x01,0x02,0x03,0x04,0x05,0x06};//星期显示代码

ucharmiao,shi,fen,date,month,day,year