电容式触摸屏设计规范组件研发部汇总.docx

《电容式触摸屏设计规范组件研发部汇总.docx》由会员分享,可在线阅读,更多相关《电容式触摸屏设计规范组件研发部汇总.docx(32页珍藏版)》请在冰豆网上搜索。

电容式触摸屏设计规范组件研发部汇总

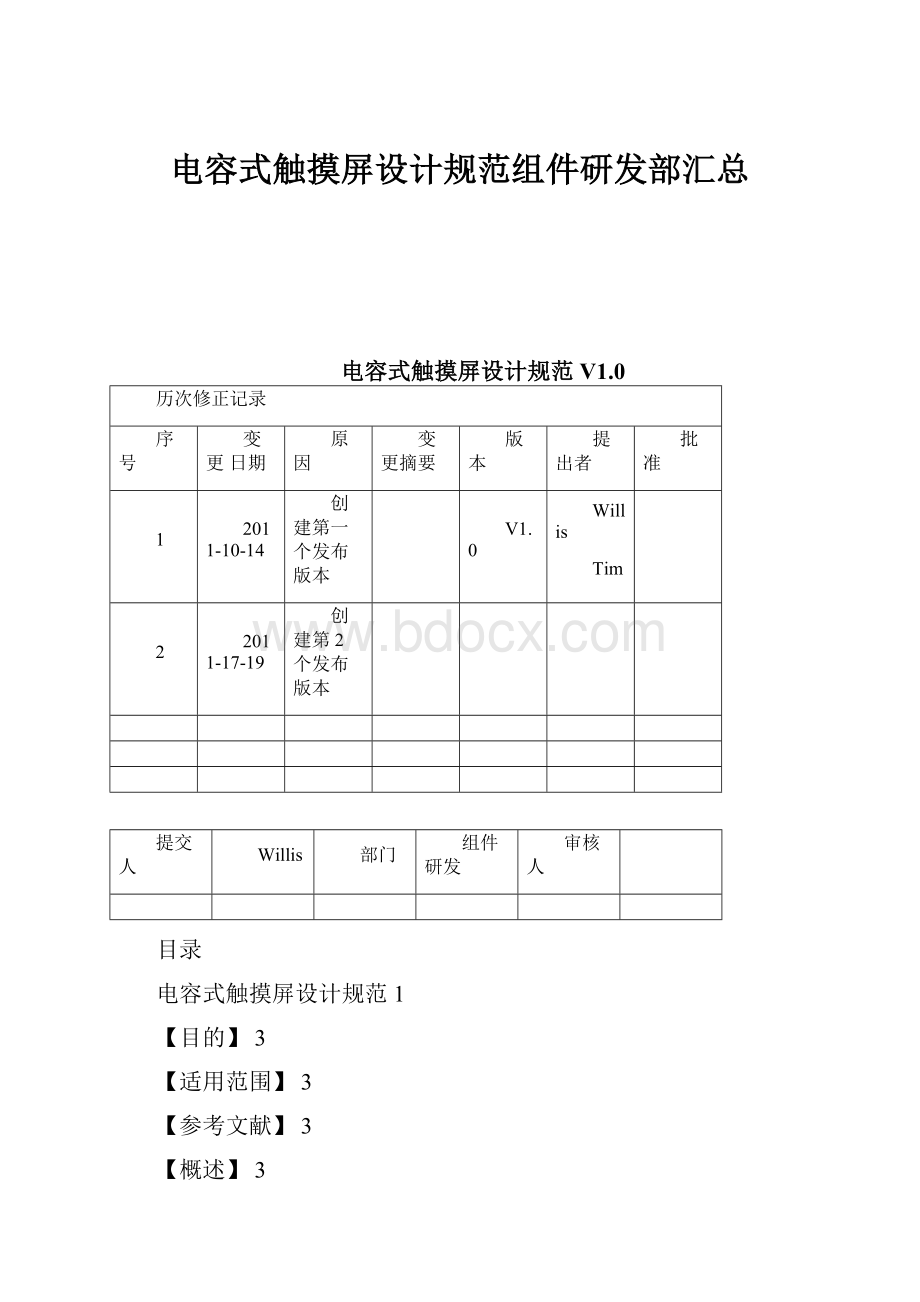

电容式触摸屏设计规范V1.0

历次修正记录

序号

变更日期

原因

变更摘要

版本

提出者

批准

1

2011-10-14

创建第一个发布版本

V1.0

Willis

Tim

2

2011-17-19

创建第2个发布版本

提交人

Willis

部门

组件研发

审核人

目录

电容式触摸屏设计规范1

【目的】3

【适用范围】3

【参考文献】3

【概述】3

【名词解释】3

【电子设计】3

一、电容式触摸屏简介3

1、实现原理3

2、自电容与互电容3

三、驱动IC简介3

三、ITO图形设计3

四、布局设计要求3

1、关键器件布局3

2、布线3

五、ESD防护3

六、技术展望3

【结构设计】3

一、结构及材料使用3

1、结构3

2、材料使用3

二、设计规范3

三、结构设计注意点3

四、生产工艺3

【目的】

本规范的制定是为了了解电容屏的相关知识,协助公司内部相关人员更好的设计应用电容屏及相关事项,确保产品设计符合客户要求和供应商制程能力,给工程师提供设计参照和依据。

【适用范围】

驱动、基带、射频、结构、组件等与电容屏相关的直接或间接部门。

【参考文献】

电容屏驱动IC原厂提供的设计指导、供应商提供的介绍资料等,以及驱动芯片规格书。

【概述】

本文简单介绍了电容屏方面的相关知识,正文主要分为电子设计和结构设计两个部分。

电子设计部分包含了原理介绍、电路设计等方面,结构设计部分包好了外形结构设计、原料用材、供应商工艺等方面。

【名词解释】

1.V.A区:

装机后可看到的区域,不能出现不透明的线路及色差明显的区域等。

2.A.A区:

可操作的区域,保证机械性能和电器性能的区域。

3.ITO:

IndiumTinOxide氧化铟锡。

涂镀在Film或Glass上的导电材料。

4.ITOFILM:

有导电功能的透明PET胶片。

5.ITOGALSS:

导电玻璃。

6.OCA:

OpticallyClearAdhesive光学透明胶。

7.FPC:

可挠性印刷电路板。

8.CoverGlass(lens):

表面装饰用的盖板玻璃。

9.Sensor:

装饰玻璃下面有触摸功能的部件。

(FlimSensorORGlassSensor)

【电子设计】

一、电容式触摸屏简介

电容式触摸屏即CapacitiveTouchPanel(CapacitiveTouchScreen),简称CTP。

根据其驱动原理不同可分为自电容式CTP和互电容式CTP,根据应用领域不同可分为单点触摸CTP和多点触摸CTP。

1、实现原理

电容式触摸屏的采用多层ITO膜,形成矩阵式分布,以X、Y交叉分布作为电容矩阵,当手指触碰屏幕时,通过对X、Y轴的扫描,检测到触碰位置的电容变化,进而计算出手指触碰点位置。

电容矩阵如下图1所示。

图1电容分布矩阵

电容变化检测原理示意简介如下所示:

名词解释:

ε0:

真空介电常数。

ε1、ε2:

不同介质相对真空状态下的介电常数。

S1、d1、S2、d2分别为形成电容的面积及间距。

图2触摸与非触摸状态下电容分布示意

非触控状态下:

C=Cm1=ε1ε0S1/d1

触控状态下:

C=Cm1*Cmg/(Cm1+Cmg),Cm1=ε1ε0S1/d1,Cmg=Cm1=ε2ε0S2/d2

电容触摸驱动IC会根据非触控状态下的电容值与触控状态下的电容值的差异来判断是否有触摸动作并定位触控位置。

2、自电容与互电容

自电容式CTP是利用单个电极自身的电容变化传输电荷,由一端接地,另一端接激励或采样电路来实现电容的识别(测量信号线本身的电容)。

自电容式CTP的坐标检测是依次检测横向和纵向电极阵列,根据触摸前后电容变化分别确定横向和纵向坐标,然后组合成平面坐标确定触摸位置。

当触摸点只有一个时,组合后的坐标也是唯一的一个,可以准确定位;当触摸点有两个时,横向和纵向分别有两个坐标,两两组合后出现四组坐标,其中只有两个时真实触摸点,另两个就是属称的“鬼点”。

所以自电容式CTP无法实现真正的多点触摸。

互电容式CTP失利用两个电极进行传输电荷,一端接激励,另一端接采样电路来实现电容的识别(测量垂直相交的两个信号之间的电容)。

互电容式CTP坐标检测也是检测横向和纵向电极阵列,不同的是它是由横向依次发送激励而纵向同时接收信号,这样可以得到所有横向和纵向交汇点的电容值,根据电容值的变化可以计算出每一个触摸点的坐标,这样即使有多个触摸点也能计算出每个触摸点的真实坐标。

所以互电容式CTP可以实现真实多点触控。

自电容的优点是简单、计算量小,缺点是单点、速度慢;互电容的优点是真实多点、速度快,缺点是复杂、功耗大、成本高。

3、结构及材料使用

三、驱动IC简介

电容屏驱动IC是电容屏工作处理的主体,是采集触摸动作信息和反馈信息的载体,IC采用电容屏工作的原理采集触摸信息并通过内部MPU对信息进行分析处理从而反馈终端所需资料进行触摸控制。

IC与外部连接是通过对外的引脚进行的,电容屏驱动IC厂家众多,各自的设计也不尽相同,但是基本原理也是大同小异,因此个驱动IC的芯片引脚也比较类似,只有个别引脚是各自功能中特殊的设计,如下对电容屏驱动IC的引脚做一个简单的说明。

驱动信号线:

即Driver或TX,是电容屏的电容驱动信号输出脚。

感应信号线:

即Sensor或RX,是电容屏的电容感应信号输入脚。

电源电压:

分模拟电源电压和数字电源电压。

模拟电压范围一般为2.6V~3.6V,典型值为2.8V和3.3V;数字电压即电平电压为1.8V~3.3V,由主板端决定。

电容屏设计可以设计为单电源和双电源两种模式,目前以单电源供电为主(可以减少接口管脚数)。

GND:

也分为模拟地和数字地两种,一般两种地共用,特殊情况下需将两种地分开以减少两种地之间的串扰现象。

I2C接口:

I2C接口包括I2C_SCL和I2C_SDA。

I2C_SCL为时钟输入信号,I2C_SDA为数据输入输出信号。

SPI接口:

SPI接口包括SPI_SSEL、SPI_SCK、SPI_SDI、SPI_SDO。

SPI_SSEL为片选信号,低电平有效;SPI_SCK为时钟输入信号;SPI_SDI为数据输入信号;SPI_SDO为数据输出信号。

RESET:

芯片复位信号,低电平有效。

WACK:

芯片唤醒信号。

TEXT_EN:

测试模式使能信号。

GPIO0~N:

综合功能输入输出IO口。

VREF:

基准参考电压。

VDD5:

内部产生的5V工作电压。

以上引脚定义没有包含全部的驱动IC的功能,如LED、Sensor_ID、Key_Sensor等特殊功能作用的管脚,这些管脚需根据具体IC确认其具体作用及用法。

如下是Focaltech的FT5X06系列的管脚说明。

Name

Type

Description

TX0~TXN

O

Transmitoutputpins.

RX0~RXN

I

Receiverinputpins.

AVDD

P

Analogpowersupply.

DVDD

P

Digitalpowersupply(1.8V).

AGND

GND

AnalogGND.

DGND

GND

DigitalGND.

INT

O

Externalinterrupttothehost.

I2C_SCL

I/O

I2Cclockinput.

I2C_SDA

I/O

I2Cdatainputandoutput.

SPI_SSEL

I

SPISlavemode,chipselect,activelow.

SPI_SCK

I

SPISlavemode,clockinput.

SPI_MOSI

I

SPISlavemode,datainput.

SPI_MISO

O

SPISlavemode,dataoutput.

/RST

I

ExternalReset,Lowisactive.

WAKE

I

Externalinterruptfromthehost.

TEST_EN

I

Testmodeenabledathighandfloatinnormalmode.

GPIO0~N

I/O

GeneralPurposeInput/Outputport.

VDD5

P

internalgenerated5Vpowersupply.

三、ITO图形设计

ITO可蚀刻成不同的图形,不过造价师相同的,而且很难讲哪个图像比其他图形工作效率高,因为触摸屏必须与电子间配合才能发挥作用。

I-phone采用的图形是最简单的一种,即在ITO在玻璃一面为横向电极,在另一面为纵向电极,此设计简单巧妙但几何学要求特别的工艺电能来产生准确的焦点。

图3I-phonePattern

闭路锁合的钻石形Pattern是最常见的ITO图形,45°角的轴线组成菱形块,每个菱形块通过小桥连接,此图形用于两片玻璃,一片是横向菱形排,另一片是纵向的菱形列,导电图形在玻璃内侧,行与列对应锁定后贴合。

菱形图形大小不一,取决于制造商,但基本在4-8mm之间,几乎所有电子控制器(CTP控制IC)都可用于此图形。

图4菱形Pattern

复杂图形的ITO图形需要专用的电子控制器,有时需要购买许可。

一些IC厂会根据自身的特点设计特定的Pattern,且为避免滥用或保护权利会申请图形专利。

目前基础ITOPattern有Diamond、Rectangle、Diamond&Rectangle、Hexagon等。

四、布局设计要求

根据驱动IC的放置位目前可分为COF、COB两种方式。

COF即ChiponFPC,作为终端导向方式被广泛应用,这种设计方式可根据实际应用效果和市场变化在不更改主板的情况下更换电容屏设计方案,可兼容多种电容屏驱动IC设计方案。

缺点是前期和后期调试工作量大,备料周期长。

COB即ChiponBoard,将驱动IC融合在主板端带来的一个问题是主板和电容屏驱动IC方案确定后不能随意更改设计方案,因为电容屏驱动IC基本都不是PINtoPIN兼容的,更换方案意味着重新布局相关的主板设计。

COB方案的优点成本降低,交期短,方便备料,前期设计和后期调试工作量小。

无论是COF或COB方案都需要在布局走线时注意相关设计要求,根据IC原厂建议以及供应商的实际应用经验,总结如下设计注意事项:

1、关键器件布局

各组电源对应的滤波电容需靠近芯片引脚放置,走线尽量短,如下为IC周围元件布局示意图:

图5元件布局示意图

电容屏与主板连接端口周围不要走高速信号线。

对于COB方案,触控IC尽量靠近HostIC。

触控IC及FPC出线路径要求远离FM天线、ADV天线、DTV天线、GSM天线、GPS天线、BT天线等。

与触控IC相关器件尽量放进屏蔽罩中,且尽可能采用单独的屏蔽罩。

触控IC附近有开关电源电路、RF电路或其它逻辑电路时,需注意用地线隔离保护触控IC、芯片电源、信号线等。

RF是手机中最大的干扰信号,因此对芯片与RF天线间的间距有一定要求:

在顶部要求间距≥20mm,在底部要求间距≥10mm。

适用于COF和COB方案。

2、布线

1)电源线尽量短、粗,宽度至少0.2mm,建议≥0.3mm。

驱动和感应信号线走线尽量短,减小驱动和感应走线的环路面积。

驱动IC未使用的驱动和感应通道需悬空,不能接地或电源。

对于COB方案,主板上的信号线走线尽量短,尽量接近与屏体的连接接口。

建议将IC周围的驱动和感应信号按比例预留测试点,方便量产测试,最少需要各留两个测试点。

I2C、SPI、INT、RESET等接口预留测试点,方便Debug。

2)用地线屏蔽驱动通道,避免驱动通道对Vref等敏感信号或电压造成干扰。

图6驱动通道的地线屏蔽

3)信号线(驱动通道和感应通道)建议平行走线,避免交叉走线。

对于不同层走线的情况,避免两面重合的平行走线方式(FPC的两面重合平行走线会形成电容),相邻的驱动通道和感应通道平行走线之间以宽度≥0.2mm的地线隔离,如下图所示:

图7正确走线方式

图8错误走线方式

由于结构的限制,导致驱动和感应通道必须交叉走线时,尽量减少交叉的面积(降低因走线而产生的结点电容,形成的电容与面积有关),强制建议交叉进行垂直交叉走线,特别注意避免多次交叉。

同时驱动和感应走线宽度使用最小走线宽度(0.07~0.08mm)。

图9推荐走线方式(完全垂直)

图10错误走线方式(非垂直走线)

对于COB方案的多层方案,建议驱动和感应通道采用分层走线,且中间以地线屏蔽。

4)信号线(驱动和感应通道)必须避免和通讯信号线(如I2C、SPI等)相邻、近距离平行或交叉,以避免通讯产生的脉冲信号对检测数据造成干扰。

对于距离较近的通讯信号线,需要用地线进行屏蔽

图11平行走线下地线屏蔽隔离

图12错误走线方式(交叉)

5)地线及屏蔽保护

芯片衬底必须接地,衬底上需放置可靠的地线过孔,建议过孔数量4~8个。

驱动和感应通道压合点两侧均须放置地线压合点,空间允许情况下,驱动和感应通道走线两侧必须放置地线,建议地线宽度≥0.2mm。

图13地线保护

FPC未走线区域需要灌铜,大面积灌铜能减小GND走线电阻,屏蔽外部干扰。

建议采用网格状灌铜,既起到屏蔽作用又不增加驱动和感应线对地电容。

建议网格铜规格:

Grid=0.3mm,Track=0.1mm。

无论COF或COB,连接Sensor和Guitar芯片的FPC,其信号线走线背面需铺铜,同时建议增加接地的屏蔽膜。

图14接地屏蔽膜

与主控板接口排线尽可能设置两根≥0.2mm的地线,保证电气可靠接地。

如结构允许,补强可用钢板,若能保证钢板可靠接地则效果更好。

6)设计参考

FPC设计时需要考虑的关键尺寸如下图所示:

图15FPC关键尺寸示意图

FPC走线禁止直角或折线,折弯处需倒圆弧;元件摆放区必须予以补强,方便贴片或焊接;所有过孔尽量打在补强板区域,FPC弯折区及附近不能有过孔;设计图上必须标注补强区位置及总FPC厚度,弯折区及附近不能有补强;弯折区与元件区过渡的圆角要达到R=1.0mm,并建议在拐角处加铜线以补充强度,减少撕裂风险。

图16弯折区与元件区过渡之圆角

在FPC设计中还要注意元件区空间的大小,特别是在结构图确认中,要充分考虑元件区大小预留结构空间。

我司后续可能常用的IC(主要为4.5寸以下)的封装尺寸及外围元件:

ICType

Components

Channel

(TX*RX)

Package

(mm)

PanelSize

FPCOutline

(mm)

Thickness

(mm)

FT5206

4C1R

15*10

5*5QFN

<3.5

9*12

0.75

FT5306

4C1R

20*12

6*6QFN

<5.7

11*11

0.75

GT818

4C1R

16*10

5*5QFN

<4.5

8*11

0.75

五、ESD防护

ESD性能是电子产品都需要关注的基本性能,ESD性能直接影响了电子产品的电气性能甚至使用寿命。

在CTP设计时应特别注意ESD防护,建议参考事项:

1)FPC边缘与机壳开孔或缝隙的距离≥3mm,避免ESD直接对FPC放电。

2)机壳设计时,建议选用有接地的金属外壳或无金属结构件的塑胶外壳,提供ESD能力。

3)部分IC可增加防ESD的TVS管等器件,如Focaltech,可提供抗ESD能力。

4)FPC设计中,增加网格的GND屏蔽(必要时增加接地屏蔽膜),保护I2C信号,放置ESD干扰串入主板。

5)减小VDD与GND距离,提高抗辐射的ESD干扰能力。

6)ITOSensor周围进行围地保护,避免ESD直接干扰Sensor。

7)隔离地线保护,IC工作电源地与FPC周围保护地分离,在IC外围进行充分连接,防止ESD直接打到IC上。

六、技术展望

随着电容屏的广泛应用及其市场潜力的开发,电容屏技术越来越受到大家的关注和肯定。

在市场整合方面,电容屏的标准化、共用性是电容屏供应商急需努力和实施的市场技术要求。

在技术方面,也有几个不同的发展方向。

1、驱动IC方面,在提高驱动IC性能的同时,将LCM驱动和CTP驱动融合在一起是一种方向。

2、在玻璃面板方面,轻薄是未来努力的主要方向。

一种是在LCD玻璃表面做CTP的ITOSensor,将LCM与CTP融合到一起;一种是in-cell,即直接将CTPSensor融合在LCD玻璃里面,即LCD玻璃本身带有CTP功能。

【结构设计】

一、结构及材料使用

1、结构

G+F结构↓

结构:

coverglass+filmsensor。

特点:

此结构用单层filmsensor,ITO为三角形结构,只支持单点,可做到虚拟两点手势。

优点:

开模成本很低,性价比高,单价属电容TP中最低的结构,总厚度可做薄,透光性好,交期短,Cover外形可更换。

缺点:

单点为主,手写较差,虚拟两点手势准确度差。

G+F+F↓

结构:

coverglass+filmsensor+filmsensor。

特点:

此结构用两层filmsensor,ITO为菱形结构,支持真实多点操作。

优点:

准确度高,手写效果好,支持真实两点,cover外形可更变。

缺点:

透光性差,比G/G结构低5%。

价格比G/F高,比G/G低。

G+G↓

结构:

coverglass+glasssensor

特点:

此结构用单层glasssensor,ITO为菱形结构,支持真实多点。

优点:

准确度高,透光性好,手写效果好。

支持真实多点,cover外形可更变,可靠性好及使用寿命长。

缺点:

受撞击后的底面glasssensor容易破坏,开发成本高,周期长,可替换性差。

2、材料使用

1)ITOGLASS:

是IndiumTinOxide三个英文字母的缩写,即氧化铟锡。

ITO玻璃是在清洁的绝缘素玻璃表面上,以真空镀膜法依序镀上SiO2层及ITO层所制成,ITO薄膜的特性是,在可见光区具有高度的穿透率与极佳的电导性。

a、目前常用的ITOGLASS厂家有:

百旭子,旭硝子。

b、GLASSSENSOR:

0.33mm,0.4mm,0.55mm。

2)ITOFilm:

氧化铟锡薄膜。

常用0.125mm。

3)OCA:

常用规格有50um、100um、150um、200um、250um、300um。

厂家主要有3M,日立化成,三菱树酯。

4)CoverGlass:

使用强化玻璃,厚度有0.55、0.7、0.8、0.95、1.0、1.1规格的,表面硬度一般为7H。

5)PMMA:

使用厚度建议1.0mm以上,且LCM与CTP间隙至少要0.5mm。

二、设计规范

1、COVERGLASS结构设计要求:

说明

分类

Smbol

TYPE

Min

NOTE

窄边部分

玻璃厚度T=0.55mm

A

2.5mm以上

玻璃厚度T=0.70mm

1.5mm以上

玻璃厚度T=1.00mm

1.0mm以上

听筒部分

1.2mm成本上比

1.4mm高出很多

B

1.4mm以上

1.2mm

C

R0.7mm以上

独立钻孔部分

D

R0.5mm以上

开槽部分

槽深3.0mm以上

E

R1.5mm以上

槽深3.0mm以内

G

R0.7mm以上

残留窄边

F

1.0mm以上

2、G+F+F结构尺寸设计要求:

(参考牧东规范)

Symbol

Definition

A1/A2

BezelWidth

B1

DistancebetweenTSPOutlinetoActiveAreaatTop

C1

DistancebetweenTSPOutlinetoActiveAreaatBottom

D1

HeightofACFBondingArea

E1/E2

DistancebetweenFPCBOutlinetoTSPoutline

F1

WidthofICMountingArea

F2

HeightofICMountingArea

W

WidthofTouchscreenActiveArea

H

HeightofTouchscreenActiveArea

No.

1

2

3

4

5

TSPSize

2.8"

3.2"

3.5"

4.3"

5.0"

W(±0.1mm)

43.2

42.12

45.36

95.04

108

H(±0.1mm)

57.6

70.2

75.6

53.86

64.8

A1(±0.2mm)

1.9

2.44

2.44

2.56

2.08

B1(±0.2mm)

1

1

1

1

1

C1(±0.2mm)

3.51

4.78

4.78

5.26

5.64

D1(±0.2mm)

1.8

1.8

1.8

1.8

1.8

E1(±0.2mm)

≥2.0

≥2.0

≥2.0

≥2.0

≥2.0

F1(±0.2mm)

TBD

TBD

TBD

TBD

TBD

F2(±0.2mm)

TBD

TBD

TBD

TBD

TBD

T1(±0.05mm)

0.7

0.7

0.7

0.7

0.7

T2(±10%)

1.3

1.3

1.3

1.3

1.3

T3(±10%)

0.14

0.14

0.14

0.14

0.14

T4(±10%)

0.6-0.8

0.6-0.8

0.6-0.8

0.6-0.8

0.6-0.8

T5(±10%)

0.4-0.45

0.4-0.45

0.4-0.45

0.4-0.45

0.4-0.45

T6(±10%)

T1+T5

T1+T5

T1+T5

T1+T5

T1+T5

以上结构尺寸为牧东给出的建议要求。

其边框走线制程为60um铜制程,相对欧菲和信利的100um的制程边框宽度要明显小。

以下为欧菲光电根据其设计经验给出的参考。

不同厂家制作工艺方面稍有不同,建议尽量大于设计要求值。

1.G+F+F结构设计要求:

(注:

以下参数为参考Synaptics设计标准,单位:

mm)

显示模组类型

VA

左右边框

上下边框

显示模组类型

VA

左右边框

上下边框

4:

3

2.5"

>2.3

>4.0

16:

9