整理硬件实验各器件芯片说明.docx

《整理硬件实验各器件芯片说明.docx》由会员分享,可在线阅读,更多相关《整理硬件实验各器件芯片说明.docx(13页珍藏版)》请在冰豆网上搜索。

整理硬件实验各器件芯片说明

积分电路

微分电路

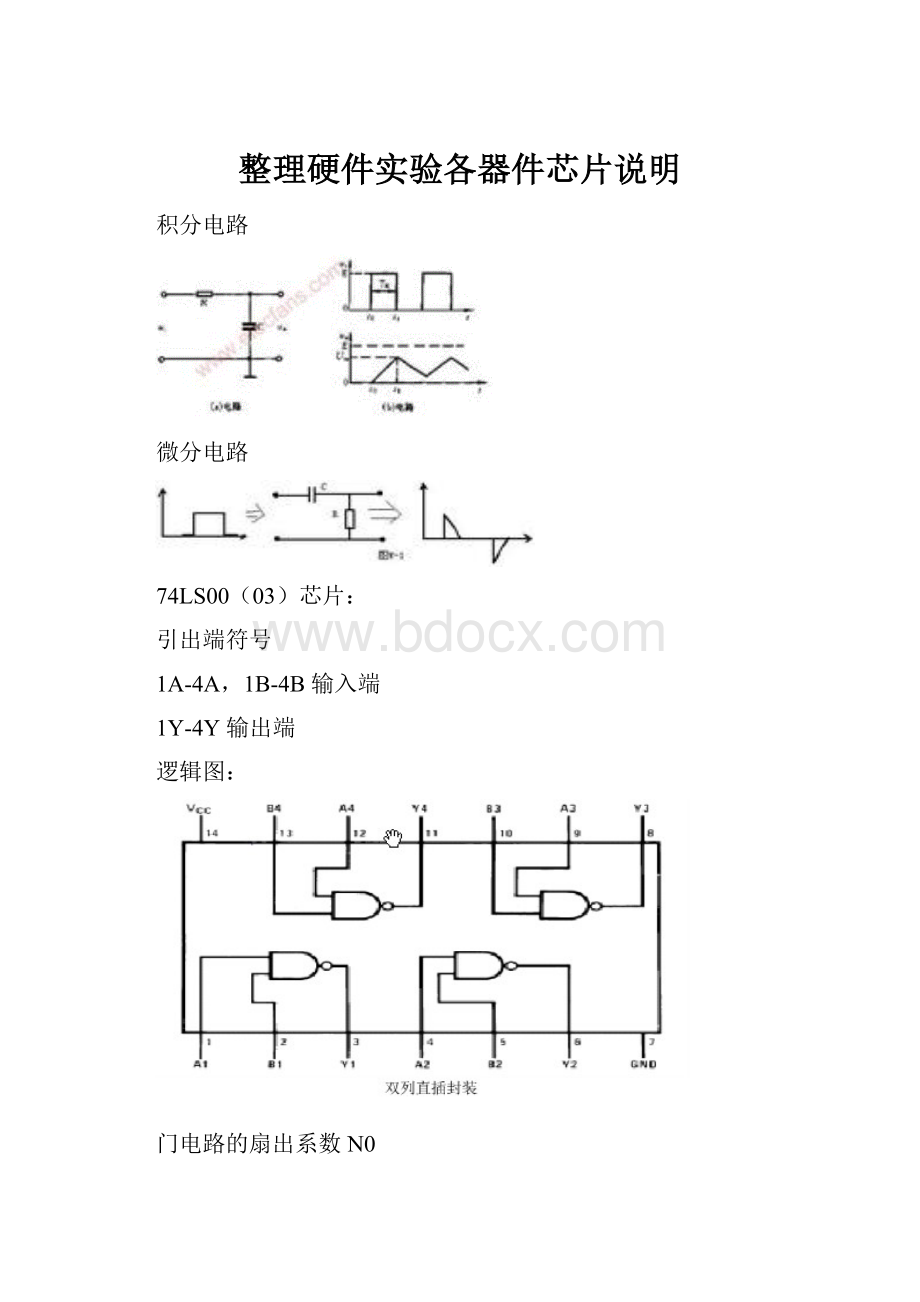

74LS00(03)芯片:

引出端符号

1A-4A,1B-4B输入端

1Y-4Y输出端

逻辑图:

门电路的扇出系数N0

扇出系数N0指门电路能驱动同类门的个数,它是衡量门电路负载能力的一个参数,TTL集成与非门有两种不同性质的负载,即灌电流负载和拉电流负载。

因此,它有两种扇出系数,即低电平扇出系数N0L和高电平扇出系数N0H。

通常有IiHN0L,故常以N0L作为门的扇出系数。

N0L的测试电路如图1-3所示,门的输入端全部悬空,输出端接灌电流负载RL,调节RL使IOL增大,VOL随之增高,当VOL达到VOlm(手册中规定低电平规范值为0.4V)时的IOL就是允许灌入的最大负载电流,则

N0L=IOL÷Iis,通常N0L>8

(Iis是短路电流,测法如下)

图1-3扇出系数测试电路:

74LS04(06)

74LS125:

引出端符号:

A1~A4输入端

C1~C4三态允许端(低电平有效)

Y1~Y4输出端

功能表:

Y=A

输入

输出

AC

Y

LL

HLXH

L

HHi-Z

74LS138

管脚图:

引出端符号:

A,B,C译码地址输入端

G1选通端

/(G2A),/(G2B)选通端(低电平有效)

Y0~Y7译码输出端(低电平有效)

同步RS触发器

CLK

S

R

Qn

Qn*

说明

0

X

X

1

1

保持

1

0

0

0

0

RS无效,则保持

1

0

0

1

1

RS无效,则保持

1

0

1

0

0

R有效,则置0

1

0

1

1

0

R有效,则置0

1

1

0

0

1

S有效,则置1

1

1

0

1

1

S有效,则置1

1

1

1

1

不定

一般不允许出现这种情况

实验数据(触发器的测试表)

S

R

Qn

Qn+1

1

0

0

0

1

1

0

0

0

1

1

1

0

0

1

不定

1

0

环境总经济价值=环境使用价值+环境非使用价值1

一、环境影响评价的发展与管理体系、相关法律法规体系和技术导则的应用0

1

1

1

1

0

一、环境影响评价的基础1

0

2.建设项目环境影响评价文件的报批时限1

二、建设项目环境影响评价0

6.提出安全对策措施建议0

4.建设项目环境影响评价文件的分级审批0

第五章 环境影响评价与安全预评价不定

从实验测得的特性表明:

表三:

周围环境概况和工艺流程与污染流程;当S、R输入分别为1、0时,无论现态是什么,次态都是为零,所以此时S、R锁的功能是将置0;

当S、R输入分别为0、1时,无论现态是什么,次态都是为1,所以此时S、R锁的功能是将置1;

当S、R输入分别为1、1时,无论现态是什么,次态都是和现态一样的,所以此时S、R锁的功能是保持上一状态;

当S、R输入分别为0、0时,现态和次态是没规律的。

4)按执行性质分。

环境标准按执行性质分为强制性标准和推荐性标准。

环境质量标准和污染物排放标准以及法律、法规规定必须执行的其他标准属于强制性标准,强制性标准必须执行。

强制性标准以外的环境标准属于推荐性标准。

74LS74

双上升沿D触发器(有预置、清除端)

1CP、2CP时钟输入端

1D、2D数据输入端

1Q、2Q、1Q非、2Q非输出端

CLR1、CLR2直接复位端(低电平有效)

PR1、PR2直接置位端(低电平有效)

74LS175

四上升沿D触发器(有公共清除端)

CP时钟输入端

CR非清除端(低电平有效)

1D--4D数据输入端

1Q--4Q输出端

1Q非--4Q非互补输出端

74LS112

双下降沿JK触发器(有预置、清除端)

CLK1、CLK2时钟输入端(下降沿有效)

J1、J2、K1、K2数据输入端

Q1、Q2、Q1非、Q2非输出端

CLR1、CLR2直接复位端(低电平有效)

PR1、PR2直接置位端(低电平有效)

用两个D触发器组成一个4分频的器件

单循环的环形计数器

555定时器

555定时器的静态测试

Vi

0

1.02

2.48

3.03

3.35

3.41

3.48

5.01

Vo

3.70

3.70

3.70

3.70

0.02

0.01

0.01

0.02

发光二极管

暗

暗

暗

暗

黄

黄

黄

黄

Vi

5.01

4.09

3.10

2.02

1.82

1.72

1.61

0.74

Vo

0.02

0.01

0.02

0.01

0.01

3.71

3.70

3.70

发光二极管

暗

暗

暗

暗

黄

黄

黄

黄

数字定时器设计

74LS48: